# République algérienne démocratique et populaire

# Ministère de l'enseignement supérieur et de la recherche scientifique

Université Saad Dahlab Blida 1

# Faculté des sciences Département informatique

Mémoire de fin d'études pour l'obtention du diplôme de Master en Informatique

Option : Système informatique et réseaux

L'algorithme des chauves-souris pour le mapping des Applications sur Noc.

<u>Réalisé par :</u>

**Encadré par :**

Aba Abdenour

Mme Boumahdi

Amrouche Wafa

Fatima

Année universitaire 2021-2022

## Résumé

Au cours des dernières décennies, les systèmes sur puces (Soc) ont été fréquemment utilisés pour équiper des systèmes et des dispositifs complexes, ils permettent d'intégrer un ensemble de composants sur une seule puce, communiquant entre eux par une structure de communication (point à point, bus partage et cross-bar). Cependant, avec la complexité de nouvelles technologies et ses tailles, ces systèmes ont trouvé leurs limites. Un nouveau paradigme est apparu comme une solution viable aux faiblesses des interconnexions traditionnelles, connu sous le nom de réseau sur puce (Noc).

Un Noc se compose d'un ensemble de ressources (R) et de routeurs (S) sont connectés entre eux par des liens. La paire (R; S) forme une tuile. La phase de mapping est une étape critique dans le processus de conception de réseau sur puce. En fait, un placement incorrect des composants logiciels d'une application peut réduire considérablement les performances globales du système final. L'étape de mapping est un problème NP-difficile, auquel cas l'utilisation de métaheuristiques est un bon moyen d'obtenir une solution optimale.

L'objectif principal de notre projet est de développer une nouvelle technique de mapping des IP dans une architecture réseau sur puce afin de minimiser les coûts de communication, l'énergie de communication et la latence. La nouvelle solution est basée sur une méta-heuristique appelée *l'algorithme des chauves-souris*, où nous considérons des architectures Noc homogènes (c'est-à-dire que les nœuds de calcul sont tous les mêmes) avec différentes topologies : 2D, 3D et 2D wifi.

**Mot clés :** Réseau sur puce (Noc), problème d'optimisation, Mapping, Algorithme de chauves-souris (Bat).

### **Abstract**

In recent decades, chip-based systems (Soc) have been frequently used to equip complex systems and devices, allowing a set of components to be integrated into a single chip, communicating with each other through a communication structure (point to point, bus sharing and crossbar). However, with the complexity of new technologies and their size, these systems have found their limits. A new paradigm emerged as a viable solution to the weaknesses of traditional interconnections, known as network on chip (NOC).

A Noc consists of a set of resources (R) and router (S) are connected together by links. The pair (R; S) forms a tile. The mapping phase is a critical step in the smart grid design process. In fact, incorrect placement of software components in an application can significantly reduce the overall performance of the final system. The mapping step is a NP-difficult problem, in which case the use of metaheuristics is a good way to obtain an optimal solution.

The main objective of our project is to develop a new IP mapping technique in a network-on-chip architecture in order to minimize communication costs, communication energy and latency. The new solution is based on a meta-heuristic called the bat algorithm, where we consider homogeneous Noc architectures (that is, the calculation nodes are all the same) with different topologies: 2D, 3D and 2DWIFI.

**Keywords:** Network on chip (Noc), optimization problem, Mapping, Bat algorithm (bat Algorithm).

## الملخص

في العقود الأخيرة، تم استخدام الأنظمة القائمة على الشرائح بشكل متكرر لتجهيز الأنظمة والأجهزة المعقدة، مما يسمح بدمج مجموعة من المكونات في شريحة واحدة، والتواصل مع بعضها البعض من خلال بنية اتصال. ومع ذلك، مع تعقيد التقنيات الجديدة وحجمها، وجدت هذه الأنظمة حدودها. ظهر نموذج جديد كحل قابل للتطبيق لنقاط الضعف في الترابط التقليدي، المعروف باسم الشبكة على الرقاقة.

يتكون Noc من مجموعة من الموارد والموجه متصلان ببعضهما البعض عن طريق الروابط. الزوج) الموارد، الموجه) يشكل بلاطة. تعد مرحلة رسم الخرائط خطوة حاسمة في عملية تصميم الشبكة الذكية. في الواقع، يمكن أن يؤدي التنسيب غير الصحيح لمكونات البرنامج في أحد التطبيقات إلى تقليل الأداء العام للنظام النهائي بشكل كبير. تعد خطوة رسم الخرائط مشكلة صعبة، وفي هذه الحالة يكون استخدام الخصائص الوصفية طريقة جيدة للحصول على الحل الأمثل.

يتمثل الهدف الرئيسي لمشروعنا في تطوير تقنية جديدة لرسم خرائط في بنية شبكة على شريحة لتقليل تكاليف الاتصالات وطاقة الاتصال وزمن الانتقال. يعتمد الحل الجديد على يسمى خوارزمية، حيث نعتبر معماريات المتجانسة (أي أن عقد الحساب كلها متشابهة) مع طوبولوجيا مختلفة.

الكلمات المفتاحية: الشبكة على الرقاقة، مشكلة التحسين، الخرائط، خوارزمية الخفافيش.

### Remerciement

Nous remercions en premier lieu Dieu le tout puissant de nous avoir donné le courage, la patience et la force de réaliser ce projet de fin d'étude.

Nous adressons nos sincères remerciements à notre promotrice Mme Boumahdi pour sa patience, sa disponibilité et surtout son soutien moral et son encouragement, qui ont contribué à alimenter notre réflexion.

Nous tenons à remercier très chaleureusement toute l'équipe pédagogique du département d'informatique de l'université Saad Dahleb (USDB), qui ont assurés notre formation tout au long des (05) années d'études, et nous ont transmis leur savoir sans réservé.

Nous tenons à remercier également Ms Boughrara qui nous a accordé de son temps et nous a conseillé.

Nous présentons nos respects et nos sincères remerciements aux membres du jury qui nous ont fait l'honneur d'avoir accepté de faire partie du jury et de nous avoir consacré de leur temps précieux.

Enfin, nous tenons à témoigner toute nos gratitudes à toutes les personnes ayant participé de près ou de loin et plus particulièrement à nos familles à la réalisation de ce projet.

## Dédicaces

Je dédie ce modeste travail accompagné d'un immense amour :

À mes parents qui m'a toujours offert le bonheur.

À mon support dans la vie celui qui ont été toujours à mes côtés

Mes sœurs Ikram , safa & Hana

À ceux avec qui j'ai passé les meilleurs moments de mon master :

Wissam , Hana , Wiam , Ferdaous , Riyadh et Lynda

A tous mes enseignants de département informatique , particulièrement

Ms.ould khaoua et Mme.Zahra .

Wafa

# Dédicaces

A mes chers parents.

A mes sœurs Imane & Mélissa.

A mon frère Mounir.

A toute ma famille, particulièrement Ma grand-mère.

A tous mes amis.

Abdenour

# Table des matières

| ını | гоаисі | non ( | senerale                              | 1   |

|-----|--------|-------|---------------------------------------|-----|

| Ch  | apitre | 1 : K | Réseaux sur puce (Noc)                | 5   |

|     | 1.1    | Intr  | oduction                              | 6   |

|     | 1.2    | Syst  | ème sur puce                          | 6   |

|     | 1.3    | Rés   | eaux sur puce                         | 6   |

|     | 1.4    | Arcl  | nitecture en couches                  | . 7 |

|     | 1.5    | Les   | principaux composants d'un réseau sur | 9   |

|     | 1.5.3  | 1     | IP (Intellectual Properties)          | 9   |

|     | 1.5.2  | 2     | Liens                                 | 9   |

|     | 1.5.3  | 3     | Routeurs                              | LO  |

|     | 1.5.4  | 4     | Interfaces réseaux                    | L1  |

|     | 1.6    | Мо    | des de commutation                    | L2  |

|     | 1.6.3  | 1     | Commutation par Circuit               | L3  |

|     | 1.6.2  | 2     | Commutation par paquet                | L3  |

|     | 1.7    | Тор   | ologies et ses Classification         | 15  |

|     | 1.7.   | 1     | Régulière & Irrégulière               | 16  |

|     | 1.7.2  | 2     | Directe & indirecte                   | L7  |

|     | 1.8    | Тор   | ologie émergente de Noc               | 21  |

|     | 1.8.3  | 1     | Réseau sue puce wifi (W-Noc)          | 21  |

|     | 1.8.2  | 2     | Topologie 3D                          | 22  |

|     | 1.9    | Algo  | orithmes de Routage                   | 23  |

|     | 1.10   | Les   | paramètres de performance             | 24  |

|     | 1.11   | Con   | clusion                               | 25  |

| Ch  | apitre | 2:1   | Travaux Connexes                      | 27  |

|     | 2.1    | Intr  | oduction2                             | 28  |

|     | 2.2    | Les   | phase de conception d'un Noc          | 28  |

|     | 2.3    | Prol  | olème de Mapping2                     | 29  |

|     | 2.3.   | 1     | Mapping Dynamique                     | 30  |

|     | 2.3.2  | 2     | Mapping Statique                      | 30  |

|     | 2.3.3  | 3     | Les défit de Mapping                  | 30  |

|     | 2.4    | Trav  | aux liers                             | 31  |

| 2.5                                      | Conclusion     |                                           |            |

|------------------------------------------|----------------|-------------------------------------------|------------|

| Chapitre 3 : Conception & Implémentation |                |                                           | <i>3</i> 8 |

| 3.1                                      | 1 Introduction |                                           | 39         |

| 3.2                                      | Con            | texte de projet                           | 39         |

| 3.2.1<br>3.2.2                           |                | Problème d'optimisation                   | 39         |

|                                          |                | Méta-heuristique & Heuristique            | 41         |

| 3.3                                      | Arch           | nitecture de la solution proposée         | 42         |

| 3.3.                                     | .1             | Module 1 : Applications                   | 44         |

| 3.3.2                                    |                | Module 2 : Topologies                     | 49         |

| 3.3.                                     | .3             | Présentation de F1 & F2                   | 57         |

| 3.3.                                     | .4             | Algorithme des chauves-souris             | 58         |

| 3.4                                      | Con            | clusion                                   | 66         |

| Chapitre 4 : Tests & Résultats           |                |                                           | 67         |

| 4.1                                      | Intro          | oduction                                  | 68         |

| 4.2                                      | Out            | ils d'implémentation utilisés             | 68         |

| 4.3                                      | La g           | énération des Benchmark : TGFF            | 68         |

| 4.4 Les                                  |                | Benchmark utilisés                        | 68         |

| 4.4.                                     | .1             | PIP                                       | 69         |

| 4.4.                                     | .2             | MDW                                       | 69         |

| 4.4.                                     | .3             | VODP                                      | 70         |

| 4.4.                                     | .4             | MPEG4                                     | 70         |

| 4.4.                                     | .5             | Benchmark Aléatoire                       | 71         |

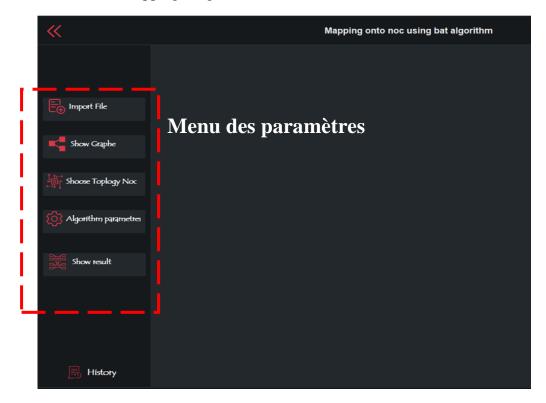

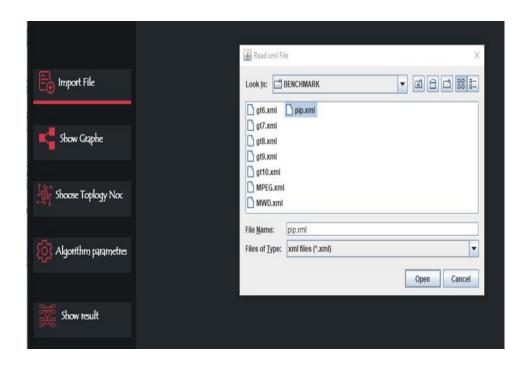

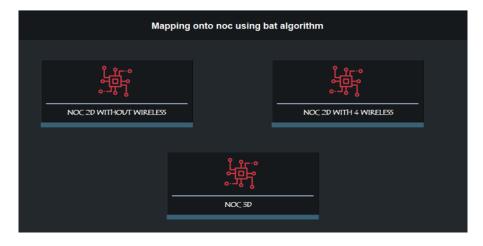

| 4.5                                      | Prés           | sentation des interfaces                  | 72         |

| 4.6                                      | Test           | s et résultats                            | 76         |

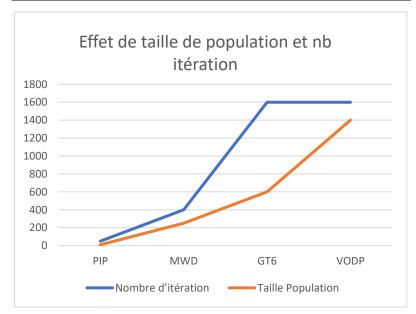

| 4.6.                                     | .1             | Etude paramétrique                        | 76         |

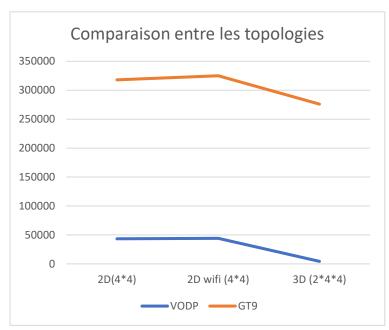

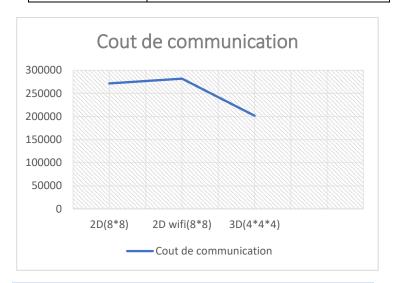

| 4.6.                                     | .2             | Etude comparative entre 2D, 2D wifi et 3D | 79         |

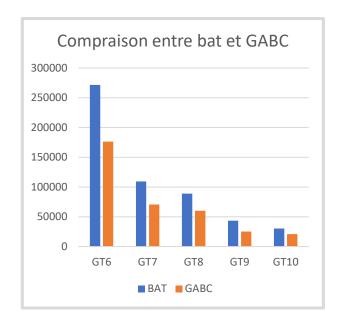

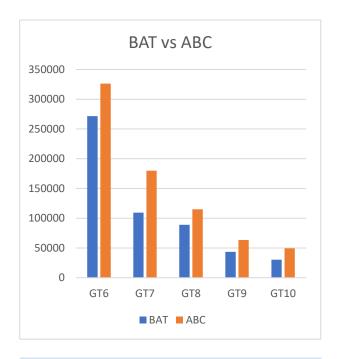

| 4.6.                                     | .3             | La comparaison avec la littérature        | 82         |

|                                          |                | clusion                                   | 91         |

| Conclusi                                 | ion G          | énérale                                   | 92         |

| Bibliogra                                | aphie          | ·S                                        | 94         |

# Tables des figures

| FIGURE 2-1: COUCHES OSI.(CHARIET, 2014)                        | 8  |

|----------------------------------------------------------------|----|

| FIGURE 2-2: COMPOSANTS DE RESEAU SUR PUCE. (BOUGUETTAYA, 2017) | 9  |

| FIGURE 2-3: ARCHITECTURE D'UN ROUTEUR.(DJABALLAH, 2011)        | 10 |

| FIGURE 2-4: ARCHITECTURE D'UN ROUTEUR AVEC LES POSTIONS DE     |    |

| Buffer.(Bouguettaya et al., 2016)                              | 11 |

| FIGURE 2-5: ARCHITECTURE NA.(DJABALLAH, 2011)                  | 12 |

| FIGURE 2-6: TYPES DE MODE COMMUTATION.(ISIAKA ET AL., 2013)    | 13 |

| FIGURE 2-7: STORE AND FORWARD.(DELORME, 2007)                  | 14 |

| FIGURE 2-8:TECHNIQUE VCT.(DELORME, 2007)                       | 15 |

| FIGURE 2-9: TECHNIQUE WORMHOLE.(DELORME, 2007)                 | 15 |

| FIGURE 2-10:TOPOLOGIE REGULIERE.(TATAS ET AL., 2012)           | 17 |

| FIGURE 2-11:TOPOLOGIE IRREGULIERE.(TATAS ET AL., 2012)         | 17 |

| FIGURE 2-12 :TOPOLOGIE 2D MESH.(TATAS ET AL., 2012)            | 19 |

| FIGURE 2-13: TOPOLOGIE TORE.(COTA ET AL, 2012)                 | 19 |

| FIGURE 2-14:TOPOLOGIE ANNEAU.(TATAS ET AL., 2012)              | 20 |

| Figure 2-15: Arbre elargie .(TOUATI, 2012)                     | 20 |

| FIGURE 2-16: ARBRE ELARGI EN PAPILLON.(TOUATI, 2012)           | 21 |

| FIGURE 2-17: EMPILEMENT DE PLUSIEURS PUCES PAR WIRE            |    |

| BONDING.(SHEIBANYRD & PETROT, 2014)                            | 22 |

| FIGURE 2-18: TOPOLOGIE 3D AVEC LIEN TSV.(MICHAEL ET AL, 2018)  | 23 |

| FIGURE 2-19:LES TOURS ASSOCIES A CHAQUE ALGORITHME.(CHARIET,   |    |

| 2014)                                                          | 24 |

| FIGURE 2-1: ORGANIGRAMME DES ETAPES DE CONCEPTION DE           |    |

| Noc.(Lemaire, 2006)                                            | 29 |

| FIGURE 2-2:TYPES MAPPING                                       | 30 |

| FIGURE 3.1.CL ASSIGNATION DES METHODES D'ORTIMISATION          | 40 |

| FIGURE 3-2:SCHEMA DE TRAVAIL.                                      | 43             |

|--------------------------------------------------------------------|----------------|

| FIGURE 3-3:GRAPHE DES TACHES.                                      | 44             |

| FIGURE 3-4: STRUCTURE XML.                                         | 46             |

| FIGURE 3-5 : SCHÉMA DTD.                                           | 46             |

| FIGURE 3-6:DIAGRAMME DES CLASSES.                                  | 48             |

| FIGURE 3-7: DIAGRAMME DES CLASSES DES TOPOLOGIE                    | 49             |

| FIGURE 3-8: REPRESENTATION DE LA CLASSE 2D.                        | 50             |

| FIGURE 3-9:PSEUDO CODE DE LA FONCTION GENERER ()                   | 51             |

| FIGURE 3-10:PSEUDO CODE DE LA FONCTION GENERER () 2DWIFI           | 52             |

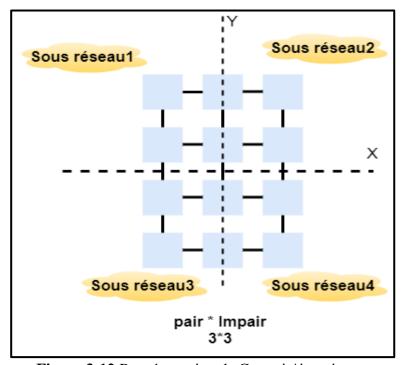

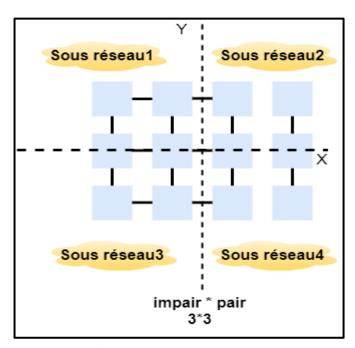

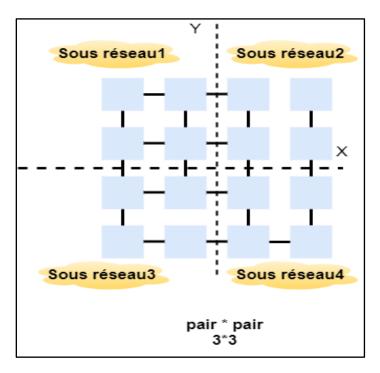

| FIGURE 3-11: REPRESENTATION DE CAS IMPAIRE * IMPAIRE               | 53             |

| FIGURE 3-12:REPRESENTATION DE CAS PAIR*IMPAIR                      | 53             |

| FIGURE 3-13:CAS IMPAIR*PAIR.                                       | 54             |

| FIGURE 3-14:CAS PAIR*PAIR ERROR! BOOKMARK                          | K NOT DEFINED. |

| FIGURE 3-15: REPRESENTATION DE LA STRUCTURE 3D.                    | 56             |

| FIGURE 3-16:PSEUDO CODE DE FONCTION GENERER 3 D ()                 | 57             |

| FIGURE 3-17: REPRESENTATION DE PROBLEME DE MAPPING <b>ERROR! B</b> | OOKMARK NOT    |

| DEFINED.                                                           |                |

| FIGURE 3-18: L'ORGANIGRAMME DE L'ALGORITHME DE CHAUVES-            |                |

| SOURIS.(SAPPA & DORNAIKA, 2019)                                    | 59             |

| FIGURE 3-19: FORMULATION DE SOLUTION                               | 60             |

| FIGURE 3-20:PSEUDO CODE DE LA FONCTION GENERER UNE                 |                |

| POPULATION.                                                        | 61             |

| FIGURE 3-21:CHOISIR LA SOLUTION GLOBALE                            | 65             |

| FIGURE 3-22:EXAMPLE DE FICHIER XML DE LA SOLUTION FINALE           | 66             |

| FIGURE 4-1:APPLICATION PIP.(TOUBALINE & AL, 2017)                  | 69             |

| FIGURE 4-2: APPLICATION MDW. (TOUBALINE & AL, 2017)                | 69             |

| FIGURE 4-3: APPLICATION VODP. (TOUBALINE & AL, 2017)               | 70             |

| FIGURE 4-4: APPLICATION MPEG4. (TOUBALINE & AL, 2017)              | 71             |

| FIGURE 4-5: INTERFACE D'ACCUEIL ERROR! BOOKMARK                    | K NOT DEFINED. |

| FIGURE 4-6:CHOIX DE BENCHMARK.                                     | 73             |

| FIGURE 4-7: AFFICHAGE DE GRAPHE.                                   | 73             |

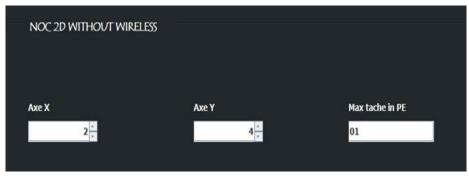

| FIGURE 4-8:CHOIX DE TOPOLOGIE.                                     | 74             |

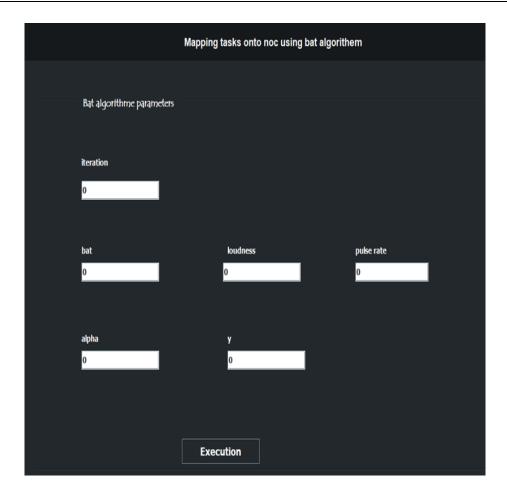

| FIGURE 4-9: PARAMETRES BAT.                                        | 75             |

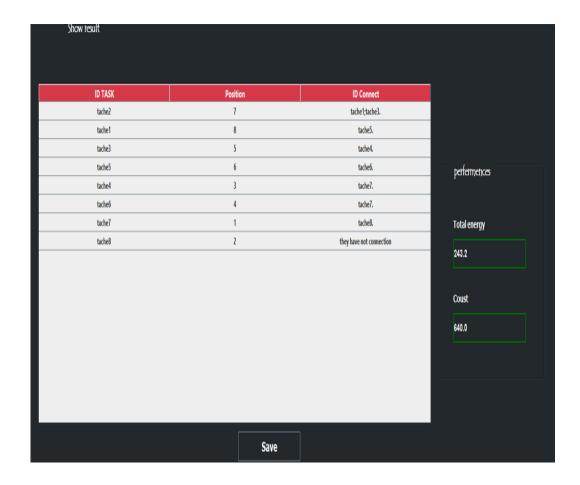

| FIGURE 4-10: AFFICHAGE RESULTAT.                                   | 76             |

| FIGURE 4-11:HISTORIQUE ERROR! BOOKMARK NOT I                | DEFINED. |

|-------------------------------------------------------------|----------|

| FIGURE 4-12: HISTOGRAMME REPRESENTE LA VARIANCE DE          |          |

| PARAMETRES ENTRE LES BENCHMARKS                             | 79       |

| FIGURE 4-13: COMPARAISON GRAPHIQUE DE TEST 4 ERROR! BOOKM.  | ARK NOT  |

| DEFINED.                                                    |          |

| FIGURE 4-14: REPRESENTATION GRAPHIQUE DE TEST 5.            | 82       |

| FIGURE 4-15: COMPARAISON BAT AVEC GABC SUR 2D               | 84       |

| FIGURE 4-16: COMPARAISON GRAPHIQUE DE BATAVEC ABC SUR 2D    | 85       |

| FIGURE 4-17: COMPARAISON BAT AVEC BFO SUR 2D ERROR! BOOKM.  | ARK NOT  |

| DEFINED.                                                    |          |

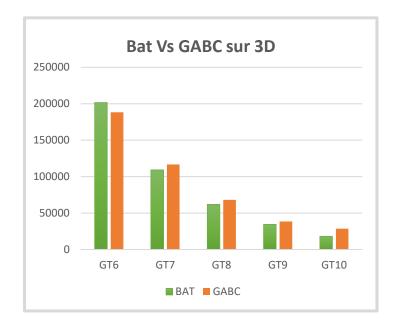

| FIGURE 4-18: COMPARAISON GRAPHIQUE ENTRE BAT ET GABC SUR 3D | 87       |

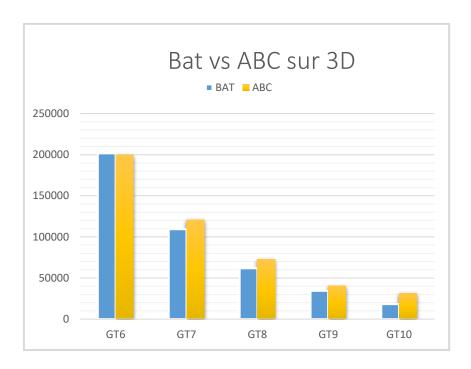

| FIGURE 4-19: COMPARAISON ENTRE BAT ET ABC SUR 3D.           | 88       |

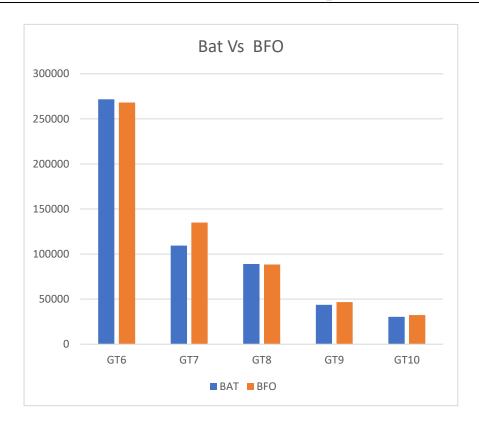

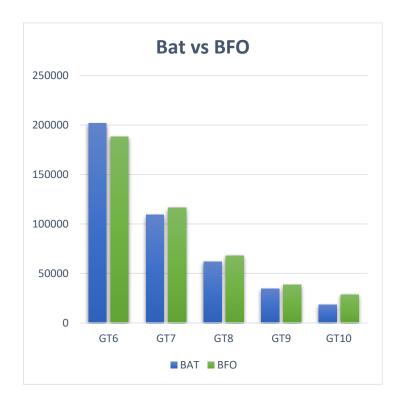

| FIGURE 4-20: COMPARAISON ENTRE BAT ET BFO SUE 3D            | 89       |

# Listes des Tableaux

| TABLEAU 1:COMPARAISON ENTRE LES ARTICLES              | 36 |

|-------------------------------------------------------|----|

| TABLEAU 2:BENCHMARKS ALEATOIRE.                       | 71 |

| TABLEAU 3: RESULTAT DES TESTS DE POPULATION & NOMBRE  |    |

| ITERATION.                                            | 78 |

| TABLEAU 4:RESULTAT D'ETUDE PARAMETRIQUE.              | 79 |

| TABLEAU 5:RESULTAT DE TEST1                           | 80 |

| TABLEAU 6:RESULTAT DE TEST 2                          | 80 |

| TABLEAU 7:RESULTAT DE TEST 3                          | 81 |

| Tableau 8:Resultat test 4                             | 81 |

| TABLEAU 9:RESULTAT TEST 5                             | 82 |

| TABLEAU 10:COMPARAISON ENTRE BAT ET GABC SUR 2D.      | 83 |

| TABLEAU 11: COMPARAISON BAT AVEC ABC SUR 2D.          | 84 |

| TABLEAU 12: COMPARAISON BAT AVEC BFO SUR 2D.          | 85 |

| TABLEAU 13: COMPARAISON ENTRE BAT ET GABC SUR 3D.     | 86 |

| TABLEAU 14: COMPARAISON ENTRE BAT ET ABC SUR 3D       | 87 |

| TABLEAU 15: COMPARAISON ENTRE BAT ET BFO SUR 3D       | 88 |

| TABLEAU 16: COMPARAISON ENTRE RESULTATS DE BAT ET LES |    |

| METHODES DE LITTERATEUR                               | 90 |

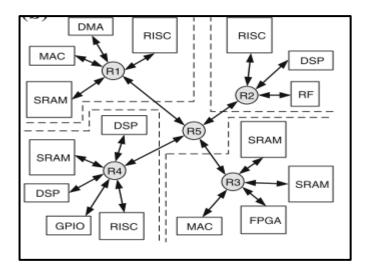

Typiquement, Un système sur puce, regroupe plusieurs composants complexes et hétérogènes tels que des processeurs programmables, des mémoires, des interfaces d'entrée/sortie, du matériel personnalisé, des périphériques, des blocs d'interface IP (propriété intellectuelle) externes, Parmi les problèmes majeurs durant la conception des Soc c'est le choix de la structure d'interconnexion entre ces éléments.(Khan et al., 2018)

Depuis 1990, la structure d'interconnexion utilisée dans les Soc est la communication à bus partage (Zerioul,2015), où tous les composants sont liés à un seul support de transport qui ne permet qu'une seule communication à la fois gérée par un arbitre. Lorsque le nombre de cœurs participants est supérieur à dix, le système de bus aura un problème de goulot d'étranglement de performances en raison de sa limitation de bande passante et ne répond pas aux besoins des nouvelles technologies où il commence à bloquer le trafic. La structure des bus commence à être étroite et elle sera moins utilisée. Des autres structures ont été également proposée afin de résoudre ces faiblesses comme : l'interconnexion entièrement cross bar et interconnexion point à point, mais elles présentent également des problèmes tels que la flexibilité et la sécurité. Pour surmonter ces défis, les concepteurs ont mis au point un nouveau concept appelé Network-on-Chip, qui s'inspire des réseaux informatiques standard.

Aujourd'hui, la majorité des applications et appareil repose sur la notion de Noc, car elle est un facteur crucial. Par rapport aux autres architectures, cette structure offre une très grande bande passante, Une diversité des chemins, le parallélisme des communications, la flexibilité, l'extensibilité et la réutilisation facile des IPs. (Bouguettaya et al., 2016)

#### Problématique:

Lors de la conception des réseaux sur puce il faut prendre en compte plusieurs des paramètres, tel que le choix de topologie, le choix de la technologie d'intégration et le placement des composants communicants (mapping), Ce dernier est un domaine

important qui intéresse les chercheurs et qui fait l'objet de notre travail de recherches au cours de ce mémoire.

Ce problème consiste à trouver un emplacement pour les IPs sur les tuiles d'une architecture Noc. Ce dernier est connu comme un problème NP difficile. Ceci est encore plus difficile lorsqu'il y a plusieurs facteurs souvent contradictoires à prendre en compte comme : la communication vs l'équilibrage de charge, la latence vs l'énergie de consommation, ces décisions du Mapping peuvent avoir une influence considérable sur la performance du système final.

#### **Objectif:**

Le but de notre travail est de trouver une solution qui maximise les performances des réseaux sur puce dans un cadre mono-objectifs.

Le problème de mapping est un problème d'optimisation difficile à résoudre et à trouver sa solution optimale, les métaheuristiques sont donc de bons candidats pour résoudre ce problème, nous proposons un algorithme appelé algorithme de chaves de souris, qui permet un mapping statique d'applications parallèles sur une architecture homogène de Noc afin de minimise le coût de communication.

#### Plan de mémoire :

Notre mémoire est constitué de 4 chapitres :

- Le chapitre 1 introduit le principe du réseau sur puce (Noc) et donne quelques généralisations, Nous allons commencer par une définition de Noc et ses composants, ainsi que les principaux paramètres qui jouent un rôle important dans l'évaluation de leur performance, telles que la topologie, les modèles de commutation et les algorithmes de routage, enfin, les paramètres de performance.

- Dans le chapitre 2, il sera intéressant de discuter et de définir le problème de mapping et ses types, puis nous présenterons quelques travaux connexes et comparerons les méthodes utilisées pour obtenir une vue d'ensemble de notre travail.

- Dans le chapitre 3, nous allons présenter notre phase conception et formulation de problématique, ainsi que l'adaptation de l'algorithme de chaves souris sur notre problème.

- Dans le chapitre 4, nous allons présenter tous les outils et les Framework utilisée pour la réalisation de ce travail, et les différents tests et résultats obtenus.

#### 1.1 Introduction

Les systèmes embarqués sont aujourd'hui utilisés dans la plupart des systèmes informatiques et des appareils électroniques : téléphones portables, voitures, téléviseurs, avions, appareils médicaux, qui sont équipés de microcontrôleurs, de logiciels et de systèmes d'exploitation en temps réel, qui sont basés sur des systèmes sur puce (Soc).

Du succès des Soc et de leur évolution rapide et de plus en plus complexe en taille, ainsi que les rôles multiples des éléments présents sur une même puce, les exigences de communication et d'interconnexion des blocs IP (Intelctutuel Property) à l'intérieur de la puce deviennent de plus en plus importantes et constituent une partie fondamentale lors de la conception de tels systèmes, et plusieurs facteurs, tels que la réduction du temps de mise sur le marché, la flexibilité et les besoins de bande passante, nécessitent une approche de conception appropriée. Par conséquent, les chercheurs ont adopté un nouveau concept, le réseau sur puce, pour répondre à la complexité croissante et aux besoins de communication des futurs systèmes sur puce. Ces réseaux sont conçus à l'image des réseaux informatiques traditionnels, mais avec certaines normes, qui sont générées par l'environnement de ces réseaux.

Dans ce chapitre nous allons définir les réseaux sur puce, leur composant, architecture et aussi les algorithmes de routage et les principales topologies, mais avant ça, nous avons présente c'est quoi les systèmes sur puce pour mieux comprendre le fonctionnement de ce concept.

#### 1.2 Système sur puce

Un système sur puce (System on Chip en anglais, Soc) peut intégrer sur une seule et même puce des processeurs, des mémoires, des réseaux d'interconnexions et des circuits spécifiques. Il existe différents types de systèmes d'interconnexion utilisables dans un Soc dont le point-à-point, le bus partagé ou hiérarchique, le cross-bar et le réseau sur puce. (Claasen, 2006)

### 1.3 Réseaux sur puce

La technologie réseau sur puce (network on chip en anglais, Noc) est une approche relativement nouvelle de la signalisation qui permet non seulement des interconnexions plus efficaces, mais également des processus de conception et de

vérification plus efficaces pour les systèmes sur puce moderne. Elle est une approche de la signalisation qui correspond aux besoins du signal à divers protocoles de communication d'une manière qui réduit la complexité de l'interconnexion de la puce. Les signaux lents ou à faible bande passante peuvent être multiplexés sur une seule ligne avec d'autres signaux, tandis que seuls les signaux à la vitesse la plus élevée et à la bande passante la plus élevée communiquent directement sur des chemins parallèles encombrants(Tatas et al., 2014).

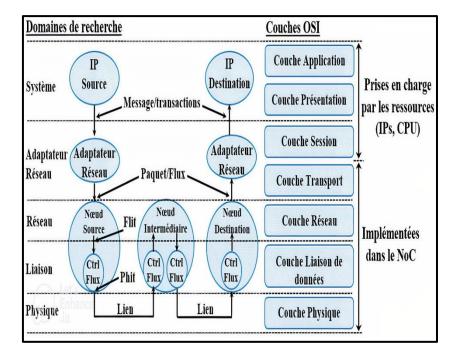

#### 1.4 Architecture en couches

Le réseau sur puce est un réseau de communication à commutation de paquets provenant du domaine informatique parallèle. La communication globale sur puce est décomposée en couches similaires au modèle de référence OSI vu dans les réseaux informatiques (Figure 1.1). Le modèle ISO/OSI ne définit pas exactement comment un système doit être construit, mais sert plutôt de guide conceptuel(Tatas et al., 2014). Plus précisément, en permettant à chaque couche de cacher sa propre complexité aux couches supérieures et de ne communiquer qu'avec les couches adjacentes (Tatas et al., 2014). Dans ce modèle, la fonction de réseau est divisée en sept couches différentes, de bas en haut, la couche physique, la couche liaison de données, la couche réseau, la couche transport, la couche session, la couche présentation et la couche application :

**La couche application**: C'est dans cette couche que se trouvent les ressources (IPs).(Tatas et al., 2014)

La couche présentation : Comme les ressources IP peuvent avoir différentes représentations de données, il doit y avoir certaines opérations de conversion entre elle. Ces opérations sont localisées dans la couche présentation(Tatas et al., 2014).

La couche session: En utilisant la couche transport, la couche session sera responsable de l'établissement de connexions entre les ressources. Elle adapte les protocoles de l'IP et du Noc (Tatas et al., 2014).

Figure 1-1: Couches OSI.(Chariet, 2014)

La couche transport : Cette couche est chargée de la transformation des messages en paquets, et inversement. Elle assure le contrôle de flux de bout en bout afin d'éviter que des données ne soient envoyées vers une destination qui n'a plus de place disponible pour les recevoir. De plus elle gère l'adaptation de protocole entre le Noc et les IP via l'adaptateur réseau(Tatas et al., 2014).

La couche réseau : La couche réseau gère les problèmes liés à la topologie et au routage qui en résulte schème(Chariet, 2014).

Couche de liaison ou commutation : Utilise la couche physique pour implémenter le mécanisme de transmission de données à travers le réseau (échange de données entre les différents routeurs avec détection et correction d'erreur de transmission)(Tatas et al., 2014).

**Couche physique :** Définit la structure physique et les protocoles nécessaires (nature d'inter connexion et largeur en nombre de bits des mots de données) pour établir la communication au niveau des liens entre les différents routeurs (Tatas et al., 2014).

Cette classification peut être résumés comme suit : (Tatas et al., 2014)

- ✓ Les couches doivent échanger un minimum d'informations à travers les interfaces.

- ✓ Il doit y avoir suffisamment de couches pour que des fonctions non liées ne soient pas insérées la même couche.

- ✓ Chaque couche doit avoir des limites avec sa couche supérieure et inférieure uniquement.

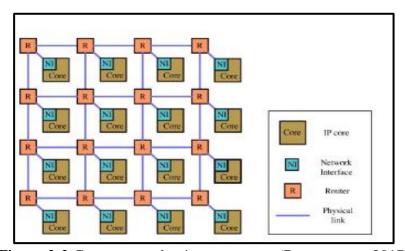

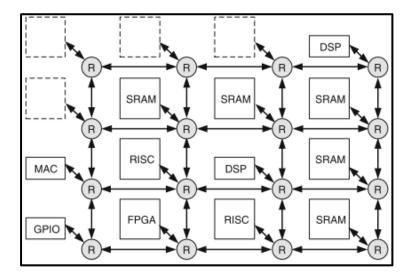

#### 1.5 Les principaux composants d'un réseau sur

Un réseau sur puce est constitué de quatre principaux composants (*Figure 1.2*), Le premier et le plus important sont les IPs , Le deuxième liens qui relient physiquement les nœuds et mettent réellement en œuvre la communication, Le troisième est le routeur qui permet d'acheminer les données à partir d'une source vers une destination, le dernier composant est l'interface réseau qui fait la connexion logique entre les cœurs IP et le réseau, puisque chaque IP peut avoir un protocole d'interface distinct par rapport au réseau (Cota et al., 2012).

#### **1.5.1** IP (Intellectual Properties)

Les IP sont n'importe quels composants tels qu'un microprocesseur, un circuit intégré spécifique à une application (ASIC), une mémoire, ou une combinaison de composants reliés entre eux. Ces IP sont reliées à des routeurs réseau via une interface réseau (Bouguettaya, 2017).

**Figure 2-2**:Composants de réseau sur puce.(Bouguettaya, 2017)

#### 1.5.2 Liens

Les liens résument les connexions entre l'interface réseau et le routeur, et entre le routeur lui-même. Ils fournissent une bande passante pour la communication entre la source et la destination et peuvent être unidirectionnels ou bidirectionnels.(Cota

et al., 2012) Un lien peut être constitué de plusieurs canaux physiques ou logiques pour réduire les taux de congestion lors des communications(Leroy, 2007).

#### 1.5.3 Routeurs

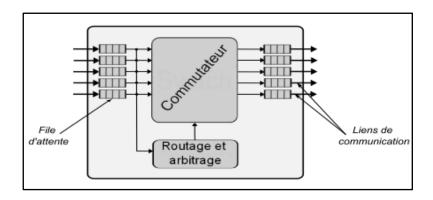

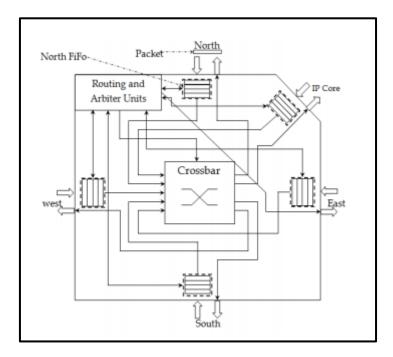

Le rôle des routeurs est d'aiguiller les données qu'il reçoit vers leurs destinataires, son architecture dépend de la topologie du Noc(figure1.3). Généralement, Il est constitué d'un ensemble de files d'attente (buffer Fifo) à chaque port, un cross-bar (matrice de commutation) qui relie les ports d'entrée avec ceux de sortie, une unité de routage et d'arbitrage(Bouguettaya, 2017).

**Figure 2-3**: Architecture d'un routeur. (Djaballah, 2011)

File d'attente: Utilisée pour le stockage temporaire des données transmises, sa taille est très importante car elle affecte directement le délai de routage, la perte de paquets, la consommation d'énergie et la surface, selon le mode de commutation choisi, les files d'attente peuvent contenir plusieurs paquets, un seul paquet, ou une partie d'un paquet. Concernant leur largeur, elle ne peut être inférieure d'une unité de contrôle de flux, Ils peuvent être placés en entrée, en sortie, ou encore en sortie virtuelle (*figure 1.4*)(Palesi & Daneshtalab, 2014).

**Figure 2-4:** Architecture d'un routeur avec les postions de Buffer.(Bouguettaya et al., 2016)

- ➤ Matrice de commutation : est un commutateur ne bloque pas qui active des connexions entre l'entrée et la sortie d'un routeur. Il est utilisé pour envoyer le paquet du tampon d'entrée vers le port de sortie approprié en fonction de l'adresse contenue dans l'en-tête du paquet(Bouguettaya et al., 2016).

- ➤ Unité de routage : permet de décoder les unités d'information envoyées par les messages entrants. Il est basé sur l'algorithme de routage et la destination du message. Sa fonction principale est de sélectionner le port de sortie le plus approprié pour la transmission des messages(Bouguettaya et al., 2016).

- ➤ Unité d'arbitrage : est utilisée pour déterminer quel paquet aura la priorité lorsque plusieurs paquets provenant de différentes sources sont en concurrence pour la transmission sur la même interconnexion. Par conséquent, lorsqu'un paquet se déplace de la source à la destination, il traverse plusieurs liaisons et passe par un ou plusieurs routeurs du réseau NoC(Bouguettaya et al., 2016).

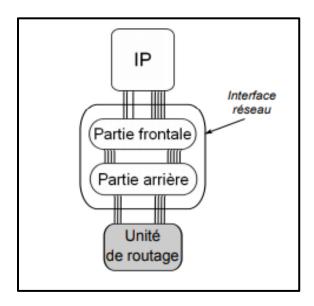

#### 1.5.4 Interfaces réseaux

Le quatrième composant de construction NoC est l'interface réseau (NI) ou l'adaptateur réseau (NA). Il fait la connexion logique entre les cœurs IP et le réseau. Ce composant est important car il permet la séparation entre le calcul et la

communication. Cela permet la réutilisation à la fois de l'infrastructure centrale et de l'infrastructure de communication indépendamment l'une de l'autre(Bjerregaard & Mahadevan, 2006).

L'adaptateur peut être divisé en deux parties : une partie frontale (front end) une partie arrière (back end). (Figure 1.5) Le frontal implémente généralement un protocole de communication point à point standardisé. La partie arrière gère le protocole réseau (assemble et désassemble le paquet, réorganise les tampons, met en œuvre des protocoles de synchronisation, aide le routeur en termes de stockage, ect)(Cota et al., 2012).

Figure 2-5: Architecture NA.(Djaballah, 2011)

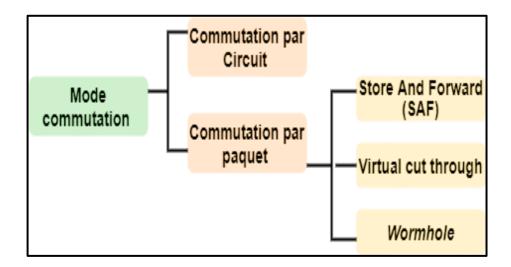

#### 1.6 Modes de commutation

Les techniques de commutation déterminent le moment et la manière dont les données sont transmises du nœud source au nœud cible (destinataire). Il existe deux principaux types (figure 1.6) de commutation dans le NoC commutation par circuit et commutation par paquet (isiaka et al., 2013)

**Figure 2-6:**types de mode commutation.(isiaka et al., 2013)

#### 1.6.1 Commutation par Circuit

La commutation de circuit (*circuit switching : en anglais*) est basée sur l'établissement d'un chemin physique réservé, composé de routeurs et de liens, entre la source et la destination avant la transmission des données. Elle peut être utilisée aussi pour améliorer l'évolutivité du réseau.

Bien que la commutation de circuits offre des transferts à faible latence en raison de l'utilisation complète de la bande passante des liaisons et l'envoi des donnes sans les mettre en mémoire tampon, elle gaspille les liaisons établies lorsqu'il n'y a pas de transmission de données, ce qui entraîne des problèmes d'évolutivité(isiaka et al., 2013).

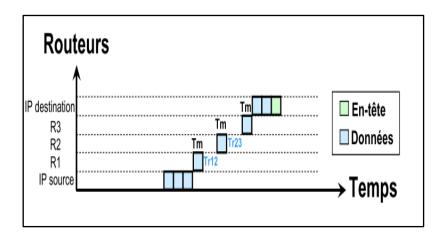

#### **1.6.2** Commutation par paquet

Ce mode divise un message en paquets, chaque paquet contient deux parties : une partie appelée l'en-tête pour le contrôle et la deuxième partie qui est l'information transportée. Les routeurs analysent et appliquent des modifications sur les en-têtes des paquets qui les traversent sur leurs ports, et guident le flux de données vers le port de sortie ciblé par les en-têtes de paquets.

D'autre part, cette technique implique que le paquet entier doit être stocké dans le routeur avant de décider d'acheminer les données vers le port de sortie, pour lequel une stratégie de commutation est requise. Il définit comment les ressources réseau doivent être allouées et libérées une fois le transfert terminé. Trois principales

stratégies de commutation sont distinguées : Store And Forward (SAF), Wormhole (WH) et Virtual Cut Through (VCT)(Palesi & Daneshtalab, 2014).

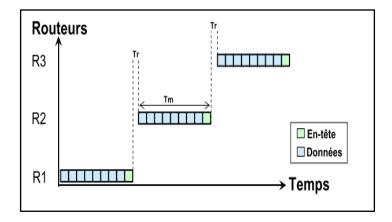

➤ Store and Forward: en commutation SAF, les paquets sont stockés en mémoire tampon FIFO avant d'être transmis à la prochaine routeur (Figure 1.7). L'inconvénient principale de cette commutation est la nécessité d'utiliser des tampons de grande taille, ce qui engendre en conséquence une grande surface de silicium en plus de la latence engendrée par l'attente de la réception de la totalité du paquet(Palesi & Daneshtalab, 2014).

Figure 2-7: Store and Forward.(Delorme, 2007)

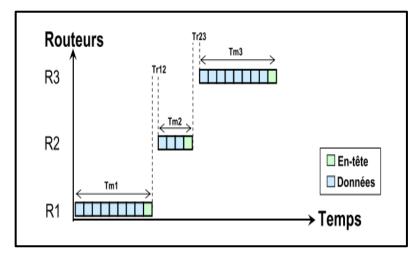

➤ Virtual Cut Through : Ce mode de commutation réduire la latence des modes (SAF) ainsi que les risques de blocage. Un routeur peut envoyer un paquet au routeur suivant avant qu'il ne le possède entièrement (figure1.8), à condition que ce dernier garantisse qu'il dispose un espace mémoire suffisant pour stocker l'intégralité du paquet. Dans le pire des cas, où l'on retombe en mode SAF s'il y a contention. L'inconvénient de ce mode est que celui-ci requiert le même espace de stockage que le SAF(TOUATI, 2012).

Figure 2-8: Téchnique VCT. (Delorme, 2007)

Wormhole: Dans cette stratégie, le paquet est découpé en plusieurs flits et envoyé un par un au routeur suivant, (figure 1.9) sans que ce dernier ne puisse mémoriser sa totalité, contrairement à la stratégie SAF (BELKACEMI, 2020). Par conséquent, l'espace tampon requis par un routeur donné et son délai de transmission sont réduits à la fois. En revanche, si le premier flit (appelé flit d'en-tête) est bloqué dans le routeur, les flits qui le suivent (appelés flit de données) appartenant au même paquet bloquent à leur tour les liens intermédiaires. Cette condition est appelée blocage en tête de ligne (HOL) et constitue le principal inconvénient de ce type d'échange(BELKACEMI, 2020).

**Figure 2-9**:technique Wormhole.(Delorme, 2007)

#### 1.7 Topologies et ses Classification

La topologie d'un réseau sur puce définit comment les différents composants sont interconnectés, Elle est souvent modélisée sous la forme d'un graphe G(N,C) dans lequel N représente l'ensemble des routeurs et C l'ensembles des liens de

communication sont respectivement associés aux sommets et aux arrêtes de graphe(Cota et al., 2012).

Une topologie peut classifier selon plusieurs critères :

#### 1.7.1 Régulière & Irrégulière

Les topologies Noc peut être classifier au premier lieu selon leur régularité. D'où un Noc est caractérisé soit comme régulier, soit comme irrégulier (Fehmi & Chatmen, 2016). Ces deux topologies présentent des avantages peut être exploitable par le domaine d'application cible. Une topologie régulière (figure 1.10) repose sur une distribution homogène des routeurs, elle convient principalement aux architectures à base de maillage et de tore. De plus, les topologies régulières sont réutilisables et imposent un minimal effort de reconception, dans le cas où elles seraient utilisées pour différentes applications/architectures(Tatas et al., 2014). Malgré ces avantages, l'utilisation de topologies régulières n'est pas fortement acceptable pour les produits commerciaux car elles imposent un certain nombre de lacunes. L'utilisation non optimale du réseau d'interconnexion c'est la raison principale de ces limitations, ce qui conduit à une augmentation des délais et de consommation d'énergie.

Une topologie irrégulière (figure 1.11), ou personnalisées a été également proposée afin de pallier ces inconvenants. Étant donné que ces topologies sont principalement orientées application, elles sont utilisées généralement aux Soc constitués de cœurs hétérogènes. De plus, la conception de cette topologie exige des algorithmes de routage plus avancés qui compte tenu de la non-uniformité du réseau sous-jacent. Par exemple, supposons une architecture Noc où chacun des routeurs doit être relie à un nombre différent de nœuds. Dans le cas où une topologie régulière est utilisée, certains des routeurs resteront non pleinement utilisés, ce qui entraînera à son tour des retards, une puissance et des surfaces importants(Tatas et al., 2014). D'autre part, il est possible de concevoir une architecture Noc hétérogène, où chaque routeur possède un nombre de ports différent. Une telle personnalisation des composants matériels se traduit par des performances supérieures, par rapport au cas où une topologie régulière est employée(KAMECHE, 2013). Cependant, l'hétérogénéité introduite impose un effort de conception supplémentaire à la fois pour les routeurs, ainsi que pour l'ensemble du Noc(Tatas et al., 2014).

Figure 2-10:Topologie Régulière.(Tatas et al., 2014)

**Figure 2-11**:Topologie Irrégulière.(Tatas et al., 2014)

#### 1.7.2 Directe & indirecte

Une topologie peut être également classé selon la manière dont les nœud sont connecte, trois grandes classes sont distingué par (Cota et al., 2012):

- Directe : chaque routeur est connecté à au moins un élément communicant (IP).

- Indirecte : les routeurs peuvent être connectés seulement à d'autres routeurs.

- Hybride : l'interconnexion des routeurs est une combinaison des réseaux directes et indirecte.

**Topologie directe:** chaque nœud est directement connecté à un nombre fixe de nœuds voisins et un message entre deux nœuds passe par un ou plusieurs nœuds intermédiaires (Rahman,2009). Seuls les routeurs sont impliqués dans la

communication dans une topologie directe et la communication est basée sur l'algorithme de routage mis en œuvre par les routeurs. La plupart des implémentations Noc sont basées sur des dispositions orthogonales des routeurs dans une topologie directe. Dans cette disposition, les nœuds sont répartis dans un espace à n dimensions et le paquet se déplace dans une dimension à la fois. Ces dispositions sont celles qui présentent le meilleur compromis entre le coût et les performances, et présentent également une bonne évolutivité(Cota et al., 2012).

Les topologies directes les plus courantes sont MeSH 2D (maillage à deux dimensions), Tore, Anneau :

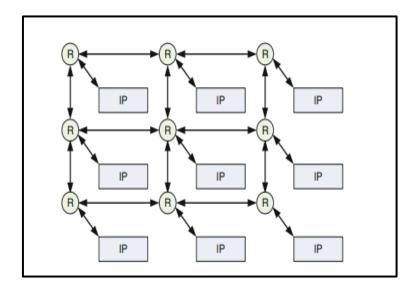

Topologie de maillage à deux dimensions (MeSH 2D) : représenté sur la Figure 1.12, est la topologie la plus simple et la plus utilisé pour les Noc. Il se constitue d'un maillage M × N de commutateurs interconnectant des nœuds, ces nœuds peuvent être des cœurs de traitement, des mémoires, etc. Chaque commutateur (ou routeur), à l'exception de ceux situés sur les côtés, est connecté à quatre commutateurs voisins et à un nœud(Rahman,2009).. Donc le nombre de commutateurs est égal au nombre de nœuds. Des canaux de communication sont utilisé afin de réaliser le chemin de communication physique entre nœuds et commutateurs (ou entre commutateurs), dont chacun se compose de deux liaisons unidirectionnelles entre soit un commutateur et un nœud, soit deux commutateurs(Cota et al., 2012). La topologie maillée 2D est simple de mise en œuvre et facilement implantable sur une technologie silicium car tous les liens ont la même longueur et impose donc une régularité inhérente qui simplifie la conception physique. Au plus, elle est plus facile à la prédation des exigences de surface pour les topologies maillées, car elle permet d'augmentent d'une façon presque linéaire avec l'augmentation du nombre de nœuds. Mais malgré ces avantages, l'utilisation de la topologie maillée présente également certains inconvénients. La pléthore de routeurs incorporés dans cette topologie conduit généralement à des régions encombrées sur le périphérique (Tatas et al., 2014).

**Topologie Tore :** C'est une topologie dérivée d'une structure 2D, avec la propriété de replier le bord extérieur sur lui-même (Figure 1.13). En tant que tel, il offre une bande passante légèrement supérieure à un maillage 2D(Delorme, 2007).

Figure 2-12 :Topologie 2D MeSH.(Tatas et al., 2014)

Figure 2-13: Topologie Tore.(Cota et al., 2012)

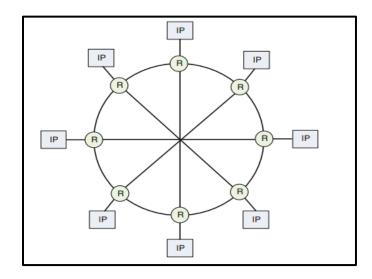

Topologie en anneau: C'est est une configuration simple, telle qu'elle est illustrée à la Figure 1.14, consiste en un anneau de huit nœuds, liés entre eux par 12 liaisons bidirectionnelles(Djaballah, 2011). Ces liaisons doté une communication à deux sauts entre n'importe quelle paire de nœuds dans l'anneau, lequel permet d'utiliser un algorithme simple pour effectuer un routage rapide mais efficace par le plus court chemin. Cette topologie suppose que chaque nœud est associé à un nœud et à un commutateur, alors que pour accomplir la communication nécessaire entre deux couples des nœuds, aux plus deux sauts sont nécessaires à l'intérieur de l'unité octogonale de base(Tatas et al., 2014).

Figure 2-14:Topologie Anneau.(Tatas et al., 2014)

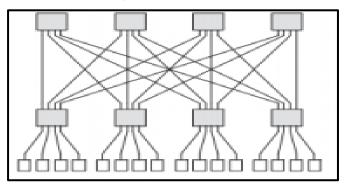

Dans **la topologie indirecte**, tous les routeurs ne sont pas connectés à des unités de traitement comme dans le modèle direct. Au lieu de cela, certains routeurs ne sont utilisés que pour propager les messages à travers le réseau, tandis que d'autres routeurs sont connectés à la logique et seuls ceux-ci peuvent être la source et/ou la cible d'un message. Les plus connu Papillon (Butterfly flat-tree) et Arbre élargi (Cota et al., 2012).

Arbre élargi : est un réseau indirect (le nombre de nœuds est indépendant du nombre de cœurs IP) (Figure 1.15), où les nœuds représentent les routeurs et les feuilles sont des cœurs connectés au réseau. Un routeur au-dessus d'une feuille est appelé son ancêtre, et les feuilles en dessous de son ancêtre sont appelées ses descendants, respectivement. Dans cette topologie, chaque nœud a plusieurs ancêtres, ce qui signifie qu'il existe de nombreux chemins alternatifs entre les nœuds(Fehmi & Chatmen, 2016).

Figure 2-15: Arbre élargie .(TOUATI, 2012)

La topologie papillon (Butterfly flat-tree): cette topologie conduit à l'augmentation de la complexité d'interconnexion et le coût en surface en raison de sa hauteur d'arbre plus élevée (figure 1.16). Dans cette topologie chaque nœud dispose de deux ancêtres et de quatre nœuds descendants(Fehmi & Chatmen, 2016). Pour pointer les nœuds, des coordonnées (L, P) sont données à chaque nœud où L'indique le niveau du nœud, et P indique sa position à l'intérieur de ce niveau. L'adresse de niveau le plus bas est zéro et les adresses des nœuds sont définis de 0 à (N-1). Il y a N / 4 nœuds au premier niveau et N / 2j +1 nœuds pour le j- éme niveau. Le nombre de commutateurs à chaque niveau est divisé par 2(Fehmi & Chatmen, 2016).

Figure 2-16: Arbre élargi en papillon. (TOUATI, 2012)

#### 1.8 Topologie émergente de Noc

La topologie maillée 2D est la plus utilisée dans les Noc en raison de sa simplicité, mais cette topologie ne peut pas répondre aux exigences d'un système sur puce trop complexe. L'intégration du wifi dans le Noc, ou l'architecture 3D, est une solution efficace au problème complexe de l'interconnexion des Soc à grande échelle.

#### 1.8.1 Réseau sue puce wifi (W-Noc)

Un réseau sur puce wifi (W-noc) est un nouveau concept basé sur les réseaux sur puce simple. Elle utilisé deux types d'interconnexion de communication entre les cœurs : une liaison filaire et autre sans fil. Le W-Noc se compose des mêmes composants que le Noc simple, la différence est en routeurs, Deux type de routeurs sont existant : Le routeur basique a la même microarchitecture que le routeur

conventionnel, et le routeur hybride qui est une combinaison de routeur basique et unité de communication sans fil (Wireless communication unit)(Yin et al., 2012).

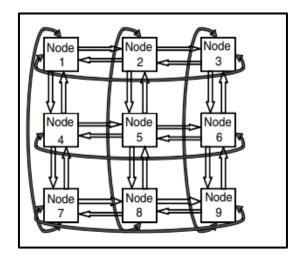

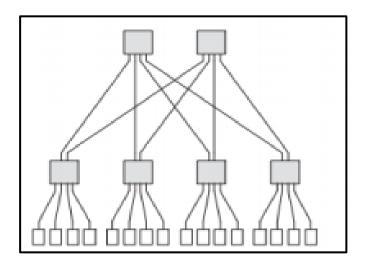

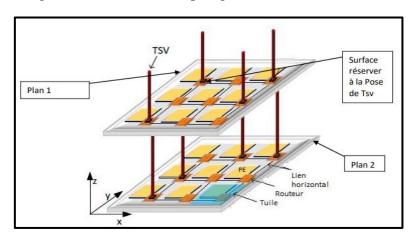

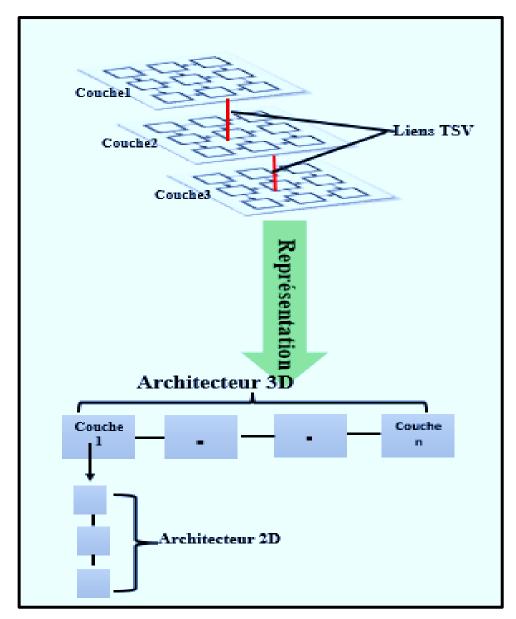

#### 1.8.2 Topologie 3D

Le réseau sur puce en 3D est une amélioration de la topologie 2D. L'intégration 3D fournit des communications verticales à travers des liens verticaux courts (TSV), ainsi que des communications horizontales. L'avantage principal de cette intégration est la réduction considérable de la longueur des liens d'interconnexions et donc, elle diminue le chemin parcouru pour le transfert de données (Toubaline, 2018).

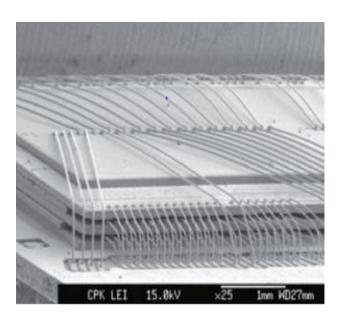

#### 1.8.2.1 Les liens TSV

Au début des années 1950(Al Attar, 2012), une proposition a été appliquée aux diapositives électroniques pour permettre la communication verticale. La première tentative consistait à empiler une puce sur une autre et à utiliser un câble à l'extérieur de la puce (Figure 1.17). Cependant, la grande surface occupée par ces liens a obligé les chercheurs à envisager un autre type d'interconnexion connu sous le nom de vias traversants en silicium, abrégé en TSV(Al Attar, 2012).

**Figure 2-17**:Empilement de plusieurs puces Par wire bonding.(Sheibanyrd & Pétrot, 2011)

La figure 1.18 illustre une topologie 3D avec des liens TSV :

Figure 2-18: Topologie 3D avec lien TSV.(Michael et al, 2018)

# 1.9 Algorithmes de Routage

Après avoir déterminé la topologie du réseau, que nous avons préalablement définies comme une organisation physique d'un réseau de nœuds, nous devons choisir un algorithme de routage. Les algorithmes de routage sont chargés de décider du chemin qu'un message doit emprunter afin d'être acheminé efficacement de sa source à sa destination. Le choix de l'algorithme de routage devient très important pour améliorer les performances du réseau, son but est de répartir le trafic de la même manière entre les chemins fournis par la topologie du réseau, améliorant ainsi le délai et le débit du réseau(Bouguettaya, 2017).

Un routage peut être déterministe ou adaptatif :

## Routage déterministe

Pour le routage déterministe, le chemin emprunté par un paquet entre la source et la destination est unique et prédéfini ,un exemple d'algorithme de routage déterministe est l'algorithme XY appliqué dans un réseau à topologie maillée 2D , dans ce cas où le paquet se déplace dans la direction x (axe des abscisses) puis dans la direction y vers la destination, un seul tour du paquet est autorisé le long du chemin de routage(Agrawal et al., 2009)(Saravankumar et al., 2013).

### Routage adaptive

Pour le routage adaptatif, plusieurs chemins peuvent être envisagés lors de la transmission du paquet, et le chemin choisi est celui qui montre le moins d'encombrement possible, contrairement aux algorithmes déterministes, dans ce cas, le paquet peut réaliser plusieurs tours avant d'atteindre sa destination(figure1.19), certains algorithmes adaptatifs comme (west first turns, north last turns, negative first turns, Odd-even turn model OE) ne permettent pas certains tours afin d'éviter les deadlock(Pétrot, 2009).

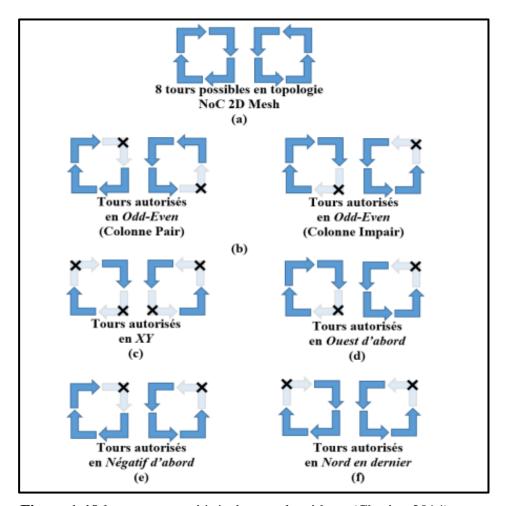

**Figure 1-19**:les tours associés à chaque algorithme.(Chariet, 2014)

# 1.10 Les paramètres de performance

Les performances d'un réseau sur puce sont évaluées par quelques critères, nous citons : la bande passante, le débit et la latence :

La bande passante : définit au taux maximal de propagation des données une fois qu'un message est dans le réseau. L'unité de mesure de la bande passante est le bit

par seconde (bps) et prend généralement en compte l'ensemble du paquet, y compris les bits de l'en-tête, de la charge utile et de la queue(Cota et al., 2012).

Le débit : est défini comme le trafic maximal accepté par le réseau, c'est-à-dire la quantité maximale d'informations délivrées par unité de temps. La mesure du débit correspond aux messages par seconde ou aux messages par cycle d'horloge(Cota et al., 2012). On peut avoir un débit normalisé (indépendamment de la taille des messages et du réseau) en le divisant par la taille des messages et par la taille du réseau. Par conséquent, l'unité du débit normalisé est le bit par nœud par cycle d'horloge (ou par seconde)(Cota et al., 2012).

La latence : est le temps total entre le début de la transmission d'un message (ou d'un paquet) et sa réception complète au nœud cible. La latence est mesurée en unités de temps et principalement utilisée comme base de comparaison entre différents choix de conception. Dans ce cas, la latence peut également être exprimée en termes de cycles d'horloge du simulateur. Normalement, la latence d'un seul paquet n'est pas significative et on utilise la latence moyenne pour évaluer les performances du réseau. En revanche, lorsque certains messages présentent une latence bien supérieure à la moyenne, cela peut être important. Par conséquent, l'écart type peut également être une mesure intéressante.(Cota et al., 2012)

#### 1.11 Conclusion

Dans ce chapitre, nous avons présenté le concept de réseaux sur puce et ses caractéristiques telles que l'architecture et les composants principaux, les différentes topologies, les modes de commutation et les algorithmes de routage, parmi lesquels nous avons montré comment choisir le meilleur chemin pour envoyer des données du nœud émetteur au nœud récepteur, à la fin, nous avons présente certains des simulateurs les plus répondus, à partir desquels nous pouvons mieux comprendre comment fonctionne cette notion.

En effet, le réseau sur puce est un paradigme inspiré des réseaux informatiques. Il consiste à intégrer l'ensemble d'un réseau de communication dans un système sur puce afin d'interconnecter ses différents composants. Afin d'améliorer leur performance et réduire la consommation d'énergie et latence, Les concepteurs et les chercheurs proposent des méthodes de mapping des tâches des applications sur les tuiles des Noc.

| Dans                                         | le | chapitre | suivant, | nous | allons | présenter | quelque | des | ces | méthodes | et |

|----------------------------------------------|----|----------|----------|------|--------|-----------|---------|-----|-----|----------|----|

| explique c'est quoi un problèmes de mapping. |    |          |          |      |        |           |         |     |     |          |    |

## 2.1 Introduction

Le réseau sur puce (Noc) est un paradigme de communication sur puce qui évolue vers une meilleure alternative à l'intégration d'un grand nombre de cœurs sur un seul système sur puce (Soc). Le flux de conception Noc contient de nombreux problèmes de différents domaines, tels que la mise en réseau, la conception embarquée et l'architecture informatique. Le mapping des applications est l'un de ces problèmes, qui est bien étudié dans la littérature, mais est généralement considéré comme un problème de minimisation de l'énergie de communication, et il existe plusieurs approches pour résoudre ce type de problème.

Dans ce chapitre, nous allons présenter quelques travaux connexes, dans chacun desquels nous allons mettre l'accent sur les architectures de réseau sur puce, la méthode choisie pour résoudre le problème et dans quel but ils ont choisi cette approche, mais d'abord, nous allons définir ce qu'est un problème de mapping et ses types.

# 2.2 Les phase de conception d'un Noc

Concevoir un Noc efficace qui répond aux besoins des utilisateurs est à la fois difficile et complexe. Afin de concevoir un Noc, il faut passer par plusieurs couches allant de la couche de modélisation à la couche d'implémentation physique.

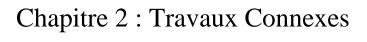

Les phases de conception d'un Noc peuvent être résumées comme suit(Pop & Kumar, 2004) :

- Modélisation du Traffic(description des applications): C'est la première étape dans la description générique d'un NOC.

- ❖ Détermination de la topologie Noc : Il s'agit d'une architecture générique spécifiquement destinée aux applications.

- Assignation des tâches aux nœuds de l'application : attribuer les tâches aux processeurs.

- Ordonnancement des tâches : Déterminez l'ordre dans lequel les tâches sont exécutées.

- ❖ Placement des tâches sur une topologie : affecter les processeurs aux tuiles de l'architecture.

- ❖ Allocation des chemins de routage et réservation des ressources : Le choix de bon chemin entre la source et la destination, car cela a un impact important sur les performances du Noc.

- Vérification des performances : Validez les performances du Noc et comparez-les aux performances souhaitées par le concepteur.

- **Développement** : développer des modèles de synthèse et de simulation.

**Figure 2-1:** Organigramme des étapes de conception de Noc.(Lemaire, 2006)

Nous nous intéressons à ce mémoire par la phase de placement des tâches (Le mapping) que nous présenterons dans la section suivante.

# 2.3 Problème de Mapping

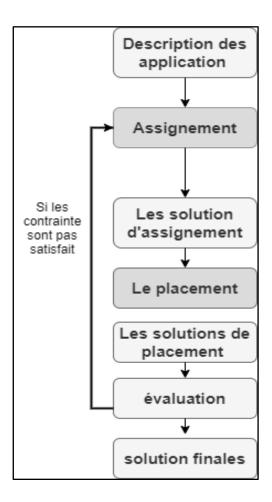

Le problème de mapping d'application est NP-difficile. Selon le moment où les tâches sont attribuées à IP pour le traitement. Les techniques de mapping peuvent être divisées en mapping dynamique et statique(Figure 2.2)(Sahu & Chattopadhyay, 2013).

Figure 2-2:types mapping.

### 2.3.1 Mapping Dynamique

L'affectation et la planification des tâches sont réalisées lors de l'exécution de l'application. Le mapping dynamique essaie toujours de détecter les goulots d'étranglement des performances et de répartir la charge de travail entre les processeurs. Étant donné que le mapping dépend de la charge actuelle du processeur, cela devrait donner une meilleure solution. Cependant, la surcharge de calcul de l'algorithme de mapping augmente la latence d'exécution et la consommation d'énergie de l'application(Sahu & Chattopadhyay, 2013).

### 2.3.2 Mapping Statique

Généralement le mapping des tâches est effectué hors ligne, avant que l'application ne soit lancée. Pour une application donnée et une infrastructure de communication cible, le mapping statique essaie toujours de définir le meilleur placement des tâches au moment de la conception. Comme le mapping est terminé avant l'exécution, l'algorithme de mapping n'est exécuté qu'une seule fois. Pour Noc, le mapping statique est généralement recommandé, car une surcharge de communication excessive dans le mapping dynamique affecte considérablement les performances du système, augmentant le retard global du système(Sahu & Chattopadhyay, 2013).

### 2.3.3 Les défit de Mapping

La complexité des fonctions intégrées dans le Soc impose diverses contraintes à la mise en œuvre de ce dernier. Ces contraintes peuvent apparaître à différents niveaux(KAMECHE, 2013) :

- Au niveau applicatif: le principal défi consiste à exploiter le parallélisme des tâches et à prendre en compte la communication concurrente dans le modèle de calcul.

- Au niveau architecture: plusieurs topologies sont explorées afin de choisir celle qui répond le mieux aux exigences et aux besoins de l'application ciblée. Ceci peut être complexe et très long à effectuer.

- Au niveau communications: l'application doit être placée sur les composants de l'architecture de telle sorte que les coûts soient minimisés.

Cette procédure est délicate car un mauvais placement peut engendrer une violation des contraintes imposées.

## 2.4 Travaux lier

Dans cette section nous allons présenter quelques travaux connexes pour mieux comprendre le problème de mapping et voire les différentes méthodes exister dans la littérature.

#### **❖** Article 1

D'après (Sahu et al., 2015), Des stratégies ont été proposé pour le mapping sur les Noc basé sur la topologie Butterfly-Fat-Tree (BFT) (figure 2.2) en utilisant une technique métaheuristique qui s'appelle *partical swarm optimisation* (PSO) unique et PSO discrète augmentée multiple. Cette approche se base sur ces principales caractéristiques :

- Les PSO ont été présentée pour le mapping des applications sur le BFT afin de minimiser le coût global de communication.

- 2. Ils ont également utilisé une PSO en plusieurs étapes. Les meilleures informations locales et globales de la i-ème étape ont été transmises aux particules dans (i+1) étape. Ceci assure une convergence plus rapide et une meilleure qualité de solution pour les étapes successives.

- 3. Quelle que soit l'étape de l'OSP, la génération initiale de la population n'est pas totalement aléatoire. Un bon nombre de particules ont été créées à l'aide d'une heuristique. Cela permis à cette technique d'explorer beaucoup mieux les régions prometteuses de l'espace de recherche.

- 4. Les valeurs métriques de coût de communication des solutions de mapping de cette approche ont été comparées à l'approche existante pour le mapping BFT. Il montre une bonne amélioration de la qualité de la solution.

- 5. Comparaison des performances dynamiques (en termes de latence du réseau) et la consommation d'énergie ont également été effectué.

Il peut être noté à partir des résultats obtenus que cette stratégie de PSO augmentée à plusieurs étapes montre de meilleurs résultats que la stratégie de mapping PSO à une étape et KL\_BFT (figure 2.3). Pour les Noc ayant un plus grand nombre de cœurs, cette stratégie PSO augmentée en plusieurs étapes produit les meilleures solutions. La comparaison des solutions produites établit les techniques de cartographie sur le Noc basé sur BFT pour être un concurrent sérieux des stratégies de cartographie précédemment disponibles.

#### \* Article 2

Dans (Çeløk, 2012), le problème de mapping d'application de flux de conception Noc est abordé d'un point de vue réseau, et l'impact du mapping sur les performances du réseau, c'est-à-dire le taux de perte généré par la mémoire tampon, est analysé. En supposant un modèle de trafic autosimilaire pour le réseau sur puce, des expressions pour le taux de perte de paquets et le nombre moyen de paquets dans la mémoire tampon sont obtenues.

Ils ont constaté que les cœurs de mapping qui ne tiennent compte que de la consommation d'énergie ont un impact dégradant significatif sur les performances du réseau en termes de taux de perte pour les systèmes de réseau sur puce. Les résultats montrent que les solutions de mapping avec une consommation d'énergie de communication acceptable peuvent varier considérablement lorsque les taux de perte observés sur les tampons sont considérés sous l'hypothèse de flux autosimilaire. Même si la consommation d'énergie est optimale, si la solution de mapping exploite un ou plusieurs tampons dans un état congestionné, cela dégradera les performances d'exécution du réseau sur puce. Par conséquent, après avoir analysé cet impact, ils ont déterminé la nécessité de résoudre le problème de

mapping d'application d'une manière qui évite également la congestion de la mémoire tampon tout en minimisant l'énergie de communication.

#### **❖** Article 3

Dans (Murali & Micheli, 2004), les auteurs ont présenté NMAP qui est un algorithme rapide pour le mapping des cœurs sur une architecture Noc maillée sous des contraintes de bande passante, minimisant le délai de communication moyen. Ils ont conçu des systèmes monolithiques complexes dans lesquels les cœurs de traitement génèrent et consomment des quantités variables de données, mettant les liens de communication au bord de la congestion. Les applications typiques sont dans le domaine du traitement multimédia. Une architecture de réseau sur puce (Noc) basée sur le maillage est proposée, dans laquelle ils explorent l'allocation de cœur aux intersections de maillage afin que le trafic sur les liaisons respecte les contraintes de bande passante. Le routage déterministe à chemin unique entre les cœurs impose des exigences élevées en matière de bande passante sur la liaison. En répartissant le trafic entre les cœurs sur plusieurs chemins, les besoins en bande passante peuvent être considérablement réduits. L'algorithme NMAP fait le routage à chemin minimum unique et pour le routage à trafic partagé. L'algorithme est appliqué à une conception DSP de référence et le Noc résultant est construit et simulé au niveau précis du cycle dans System à l'aide de macros de la bibliothèque xpipes. En outre, des expériences avec six applications de traitement vidéo montrent des économies significatives en termes de bande passante et de coût de communication pour l'algorithme NMAP par rapport aux algorithmes existants.

### **❖** Article 4

Cet article (Wang et al., 2016) étudie le problème de mapping IP sous les contraintes de bande passante et de latence qui mappe un ensemble donné de cœurs IP sur les tuiles d'une architecture de réseau sur puce (Noc) basée sur le maillage afin de minimiser la consommation d'énergie de communications.

Un algorithme a été proposé pour solver ce problème, C'est un algorithme efficace basé sur un modèle (TEM) qui génère des résultats de mapping de haute qualité avec un temps d'exécution réduit. Il est conçu sur la base de deux modèles : les graphiques avec des sommets étroitement couplés et ceux avec des sommets distribués. Dans le 1 er cas, TEM mappe d'abord les nœuds chauds avec leurs quatre

voisins les plus significatifs, après quoi les cœurs IP restants sont mappés par ordre décroissant en fonction des poids des bords. Dans le 2 -ème cas, les sommets distribués sont mappés selon un schéma de partition de graphe, d'où TEM divise le Noc en régions et le CTG en blocs ; puis il mappe les cœurs IP à l'intérieur de chaque bloc d'une manière diviser pour mieux régner.

Les tests sur les benchmarks multimédias et aléatoires montrent que TEM génère des résultats de mapping de haute qualité avec de faibles temps d'exécution et permet d'économiser en moyenne 15 % d'énergie par rapport à MOCA.

#### **❖** Article 5

Les architectures Noc sont considérées comme les systèmes d'interconnexion de nouvelle génération pour les systèmes multiprocesseurs sur puce. La sélection de l'architecture du réseau et la cartographie des nœuds IP sur la topologie Noc sont deux sujets de recherche importants.

Dans cet article (Bononi et al., 2017), Ils ont comparé quatre architectures Noc importantes : Ring et MeSH, le Spidergon STNoC et le Cross-bar sans tampon en utilisant des modèles de trafic Mpeg4 théoriques et réalistes. Le mapping PE/SE a été calculé par une version personnalisée de l'outil de partitionnement SCOTCH, tandis que le mapping Cross-bar est trivialement optimal. Ainsi que le débit maximal de livraison de réponse a été mesuré sous différents modèles de trafic homogènes et différentes tailles de réseau. Les résultats indiquent que dans de nombreux scénarios de trafic uniformes, le Noc Cross-bar surpasse les autres architectures en raison de sa cartographie optimale et de ses propriétés de distance moyenne optimales. Spidergon STNoC montre une meilleure évolutivité (exigences de tampon réduites) que MeSH tout en maintenant des performances en ligne avec le MeSH lui-même. Dans un scénario de trafic Mpeg4 réel, la barre transversale montre un comportement très évident sous un trafic complexe et non uniforme. Le manque de mémoire tampon le rend moins efficace en termes de débit. Bien qu'il existe des différences significatives dans la mise en mémoire tampon du Noc à 12 nœuds, les topologies Spidergon et Ring fonctionnent de manière similaire. De plus, Spidergon et Ring surpassent légèrement les architectures MeSh et Cross-bar, avec un bon équilibre du trafic des canaux. Les performances du maillage sont limitées par la forme rectangulaire et les propriétés de l'algorithme de routage : la sélection de chemin plus large accordée par la topologie du maillage ne constitue pas un avantage si l'algorithme de routage ne peut pas en tirer profit. Les petites différences de performances mesurées dans les scénarios MPEG suggèrent que dans ce cas, le choix du Noc à utiliser doit être principalement basé sur des facteurs tels que la surface et les exigences de tampon. Ils recommandent une analyse approfondie dans les travaux futurs de la pénalité de performance introduite par les répéteurs qui peuvent être insérés sur des liens trop longs pour respecter la synchronicité du système, tout en considérant des graphes de tâches ou plus pertinents pour les applications de streaming réalistes ou les modèles de trafic plus théoriques tels que des arbres et des forêts à routage unique/multiple.

#### Mémoire 1

Cette mémoire intitule sur « Mapping dans les réseaux sur puce 3D » (MESSAOUADI, 2019)se concentre sur le développement d'une méthode pour mapper les IP d'une application sur un réseau sur puce afin de minimiser les coûts de communication. Ils sont basés sur la topologie 3D la plus largement utilisée. Permet de répondre aux exigences et aux faiblesses des architectes 2D, notamment pour les applications avec un très nombres des tâches et de grande taille. La technique présentée dans ce travail est une méta-heuristique, appelée BFO, qui appartient à l'une des approches de résolution de problèmes d'optimisation, qui sont basée sur l'optimisation de butinage dans le monde bactérien.

Tableau 1:Comparaison entre les articles

| Article                     | Architecture Noc                | Problème                                                | Objective                                    | Méthode                               |

|-----------------------------|---------------------------------|---------------------------------------------------------|----------------------------------------------|---------------------------------------|

| (Murali &<br>Micheli, 2004) | 2D mesh                         | Mapping sur<br>les cœurs<br>noc                         | Minimiser<br>latence et<br>bande<br>passante | Algorithme<br>NMPP                    |

| (Çeløk, 2012)               | /                               | Augmenter<br>la<br>performance<br>de noc                | Minimiser<br>l'énergie                       | Conception<br>de<br>memoire<br>tampon |

| (Sahu et al, 2015)          | BTF                             | Mapping sur<br>les cœurs<br>noc                         | Minimiser<br>énergie                         | PSO                                   |

| (Wang et al., 2016)         | 2D mesh                         | Mapping sous la contrainte de latence et bande passante | Minimiser<br>energy de<br>communication      | TEM                                   |

| (Bononi et al., 2017)       | Ring/mesh/corsbar<br>/Spidergon | Comparaison entre des architectures noc                 | Trouve<br>meilleure<br>performance           | /                                     |

| (MESSAOUADI,<br>2019)       | 3D »                            | Mapping des<br>applications<br>sur la<br>topologie 3D   | Minimiser le<br>coût de<br>communication     | BFO.                                  |

## 2.5 Conclusion

Dans ce chapitre, nous avons présenté le concept de mapping et leurs types, puis nous avons étudié les travaux connexes qui traitent les méthodes de mapping sur les Noc.

En effet, les Nocs sont les cadres de communication sur puce pour les systèmes multi/multicœurs car ils surpassent les bus traditionnels en termes d'évolutivité, de parallélisme et d'efficacité énergétique. Le mapping des IPs des applications sur

leur tuile est l'étape la plus importante de la construction et de la conception de différents architectes.

Dans le chapitre suivant, Nous allons présenter notre solution pour résoudre le problème de mapping afin d'améliorer les performances de noc.

#### 3.1 Introduction

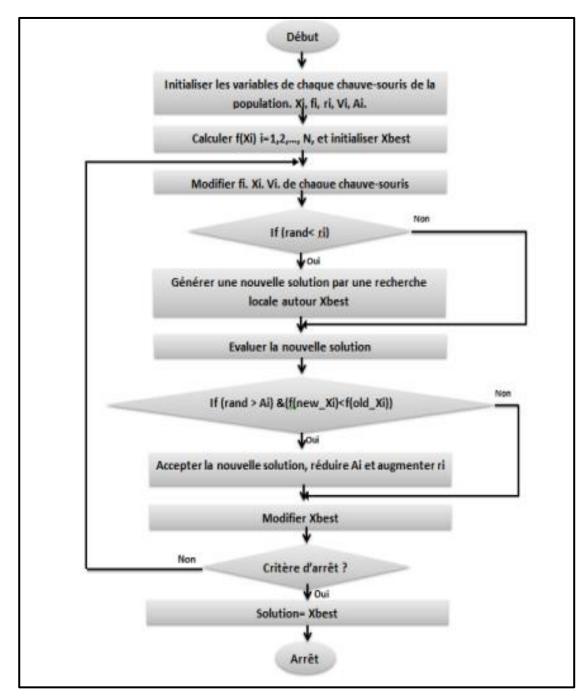

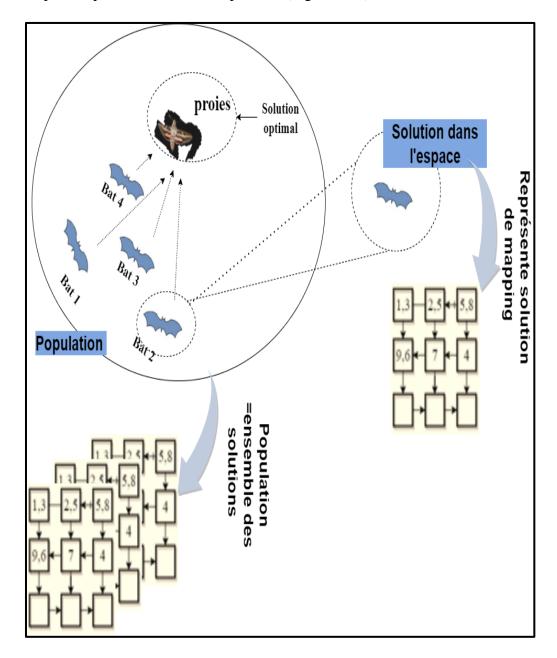

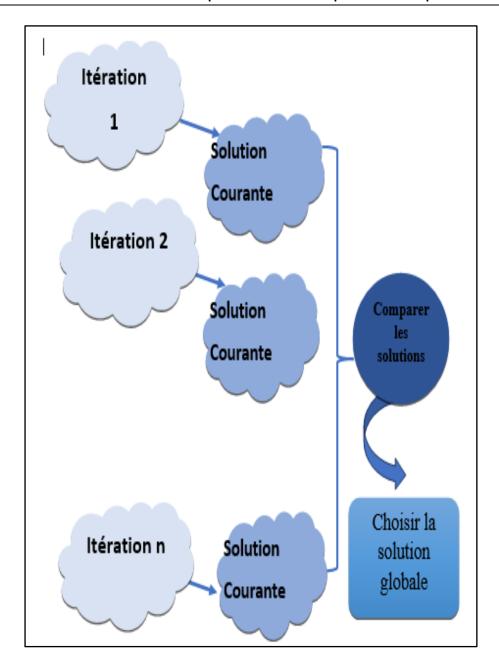

L'objectif principal de notre travail est le mapping sur les réseaux sur puce, Ce problème peut être classifié parmi les problèmes d'optimisation, car il consiste à minimiser le coût de communication, Nous avons proposé de résoudre ce problème avec l'un des algorithmes méta-heuristique, l'algorithme de chauves-souris (Bat algorithme).

Ce chapitre présente la partie de conception de notre mémoire, nous allons donc d'abord définit les problèmes d'optimisation et les méta- heuristique, ensuite nous allons présenter l'algorithme proposé et son adaptation sur notre problème, ainsi la modélisation de l'algorithme, et à la fin nous conclurons le chapitre par une conclusion.

# 3.2 Contexte de projet

Les problèmes d'optimisation parmi les concepts les plus reconnu au domaine informatique, ils servent à minimiser ou maximiser une fonction qui s'appelle la fonction d'objectif, Mais certain de ces derniers sont impossible a résolu d'une façon exacte au temps raisonnable, Pour cette raison, les chercheurs souvent utilise des méthode approche, qui sont les heuristiques ou les méta-heuristiques, Malgré ils ne donnent pas des résultat exacte et optimale, mais ils nous aider de trouver des solution approximative.

## 3.2.1 Problème d'optimisation

Un problème d'optimisation se définit comme la recherche du minimum ou du maximum (donc de l'optimum) d'une fonction donnée par rapport à tous les paramètres concernés.(Luis & Moncayo, 2002) Par exemple, dans notre problématique de mapping des composants logiciels ou des tâches d'une application, nous cherchons à minimiser le coût de communication en termes d'énergie et de latence.

La définition du problème d'optimisation est souvent complétée par la donnée des contraintes : tous les paramètres (ou variables de décision) de la solution proposée doivent respecter ces contraintes, sinon la solution n'est pas réalisable. (Luis & Moncayo, 2002)Dans notre cas, pour mapper une application qui est représentée par un graphe des tâches, il faut vérifier que la taille de ce graphe est inférieure ou égale à la taille de Noc.

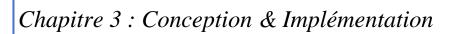

Les méthodes d'optimisation se divers selon les nombres des contraintes et le problème en plusieurs classes, Nous citons dans la *figure 3.1* les plus important et proche de notre domaine de recherche.

### Ajouter des détaille sur le graphe

Les méthodes exactes: L'intérêt de ces méthodes est qu'elles garantissent la meilleure solution au problème traité. Ces méthodes énumèrent toutes les solutions possibles et choisissent la meilleure d'entre elles. En effet, ils permettent de parcourir tout l'espace de recherche pour s'assurer d'obtenir toutes les solutions possibles meilleures que la solution optimale trouvée lors de la recherche. Cependant, si le problème est important, la méthode exacte prend trop de temps et coûte souvent trop cher en termes de ressources requises(MEHAMDIA & TIGRE, 2018).

Les méthodes approchées: Pour pallier les problèmes liés aux méthodes exactes, à savoir un temps et un coût excessifs, des méthodes approchées sont apparues. Ces méthodes sont plus

pratiques pour résoudre des problèmes difficiles, et à grande tailles, visant à trouver des solutions dans un délai raisonnable. Ils ont donné de bons résultats dans un temps acceptable. Ces méthodes se divisent en deux catégories (MEHAMDIA & TIGRE, 2018): Les heuristique et les méta-heuristique.

### 3.2.2 Méta-heuristique & Heuristique

Les heuristiques sont des solutions développées pour résoudre un problème spécifique. Ils sont performants et peuvent trouver efficacement des valeurs optimales dans un petit espace de recherche de manière précise, mais cela nécessite beaucoup d'expertise et d'expérience. Quant aux métaheuristiques, ce sont des méthodes générales qui peuvent être appliquées à un ensemble de problèmes. Ces méthodes sont souvent des algorithmes inespérés de la nature (physique, évolution biologique, éthologie...) et elles sont applicables à tout problème d'optimisation.(Karima, 2003) Dans ce projet, nous proposons d'utiliser une technique basée sur l'algorithme de chauves-souris (Bat), inspiré du comportement des chauves-souris.

Le nombre d'objectifs d'optimisation permet de distinguer les problèmes monoobjectifs des problèmes à objectifs multiples. Résoudre un problème d'optimisation mono-objectif consiste à trouver une solution qui optimise une seule fonction objective. Cependant, les problèmes de type multi-objectifs cherchent à optimiser plusieurs objectifs simultanément (Karima, 2003). Notre recherche vise à minimiser l'énergie de communication, la latence et le coût de communication dans le cas des architectures homogène où tous les PE fonctionne de manière identique, Pour cela ces objective peuvent être résumé dans une fonction d'objectif unique qui minimise le nombre de sauts entre la source et la destination, où plus la distance est petite, plus le coût global de communication est faible. Par conséquent, nous pouvons conclure que notre étude s'inscrit dans le cadre de l'optimisation mono objectif.

# 3.3 Architecture de la solution proposée

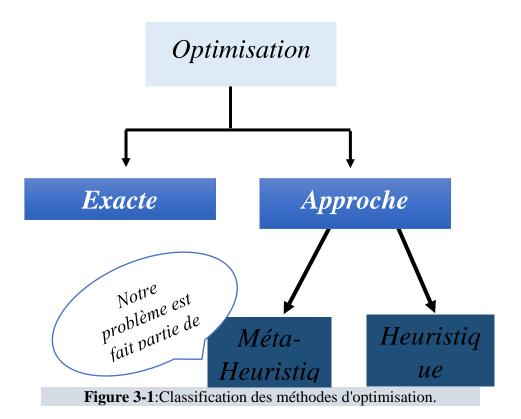

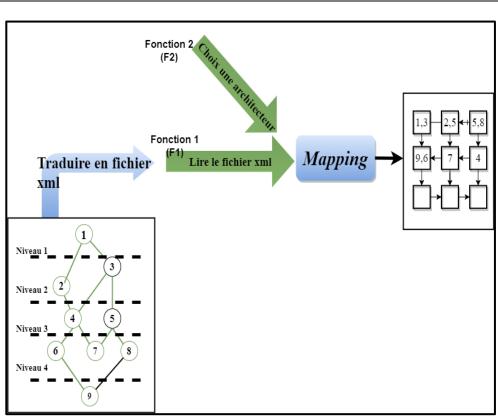

Notre application base sur un système qui nécessite des entrées pour produire des sorties. Nous avons modélisé notre architecture avec trois principaux modules relient entre eux par des fonctions comme suit :

#### 1. Les Modules :

- ✓ **Module1** : les applications qui sont sous forme des graphes des tâches.

- ✓ **Module** 2 : les architectures Noc qui constitue un ensemble des PE relie entre eux par des liens.

- ✓ **Module 3 :** l'algorithme de chauves-souris et son adaptation sur notre problème.

#### 2. Les fonctions :

- ✓ **F1** (**Lire un fichier xml**) : une fonction permet de lire un fichier xml qui décrit une application.

- ✓ **F2 :**( Choix une topologie) : une fonction permet de choisir une topologie Noc parmi les topologies proposées.

- ✓ F3(Sauvegarder le résultat final) : permet de sauvegarder la solution finale obtenue par le bat.

- ✓ F4(Ajouter le résultat à l'historique) : ajouter la solution finale dans le fichier historique.

La figure 3.2 illustre un schéma qui détaille notre architecture.

Figure 3-2: Schéma de travail

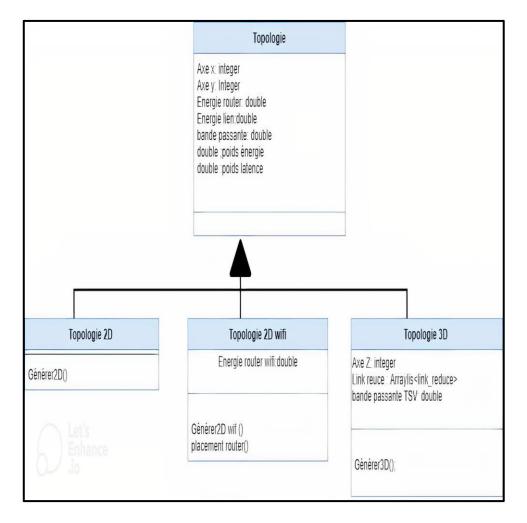

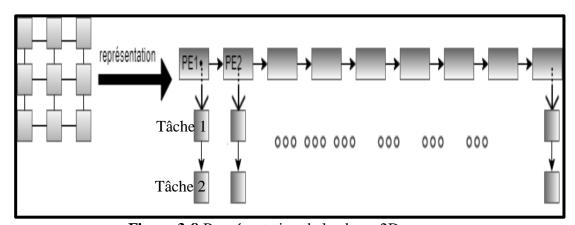

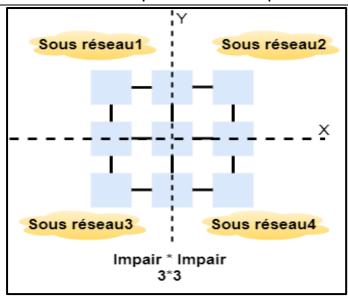

### 3.3.1 Module 1 : Applications

Le **Module 1** sur le schéma précédant décrit les premiers entrés de notre système. Pratiquement une application ou un logiciel représenté par un graphe des tâches.

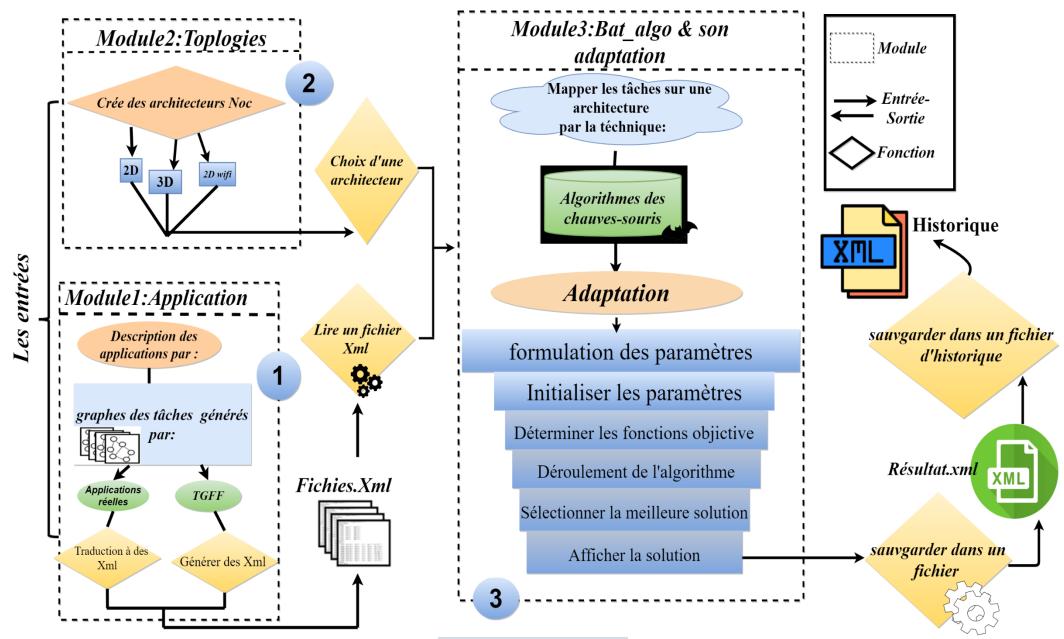

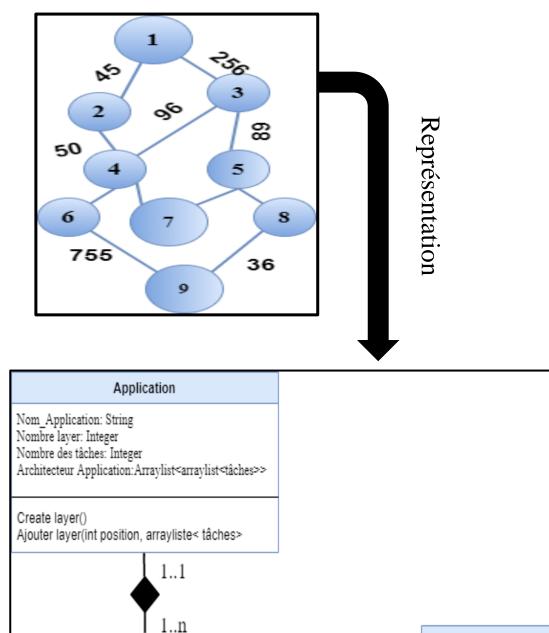

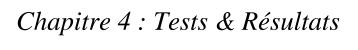

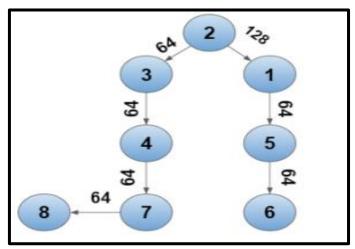

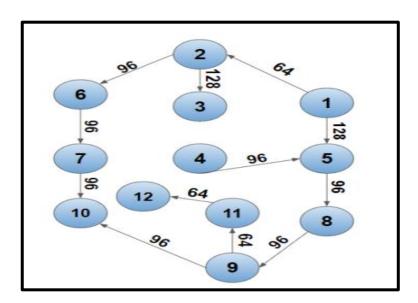

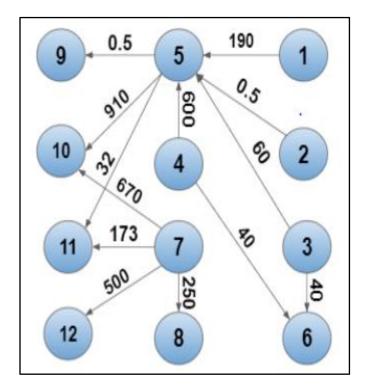

Un graphe des tâches ou graphe d'application G (T, C) est un graphe oriente (Figure 3.3), dont les nœuds  $(t_i \in T)$  représentent les tâches caractérise par des numéros (ID), et les arcs  $(c_i \in C)$  représentent les liens entre les différentes tâches, ils sont caractérisés par un coût de communication qui désigne le nombre de paquets envoyée d'une source à une destination.

Figure 3-3: Graphe des tâches.

Nous avons utilisé deux types de graphe des tâches, des graphes générées aléatoirement par l'outil TGFF qui permet de générer des fichiers xml automatiquement, et des graphes des applications réelles existant aux littératures (VODP, PIP, MDW, MPEG4).