الجمهورية الجزائرية الديمقراطية الشعبية People's Democratic Republic of Algeria

وزارة التعليم السعالي والبحث العلمي Ministry of Higher Education and Scientific Research

> جامعة سعد دحلب البليدة SAAD DAHLAB University - BLIDA

> > كلية التكنولوجيا Faculty of Technology

فسم الإلكترونيك Department of Electronics

#### **Final Thesis**

Domain: Science and Technology Field: Electronics Specialization: Embedded Systems

Presented by

Laid Abderrahmane & Ouffa Wissal

Thesis Title

# Design and Implementation of a custom PCB-Based Edge AI System Using STM32 for Real-Time State Detection and Condition Monitoring

Supervisor: Mme D.Naceur

## Acknowledgment

First and foremost, we are profoundly grateful to Allah for His countless blessings and guidance throughout our journey. Without His wisdom and grace, this work would not have been possible. We would like to express our heartfelt gratitude to our supervisor Madame Naceur, whose continuous support, dedication, and enthusiasm have been a true source of motivation throughout this journey. Over the past two years, she has not only guided us academically but also created a positive and encouraging environment that made learning genuinely enjoyable. Her trust, patience, and insightful feedback have pushed us to grow, both personally and professionally.

We are also deeply thankful to our families for their constant support, understanding, and love, which have been fundamental to our progress and perseverance.

Finally, we would like to thank the jury members for their time, valuable feedback, and constructive remarks which have contributed to the enrichment of this work.

## **Dedication:**

#### Abderrahmane Laid

All praise and thanks to Allah, whose guidance and mercy made this possible.

To my parents, thank you for your endless support, love, and prayers. I wouldn't be here without you.

To my beloved fiancée, your unwavering belief in me, your patience, and your constant encouragement have been a source of strength throughout this journey.

Your love and support mean the world to me, and I am endlessly grateful to have you by my side.

To my late grandfather, your memory lives in every step I take. Your wisdom, kindness, and the bond we shared continue to guide and inspire me. This achievement is dedicated to you,I hope I've made you proud.

To Madame Naceur, thank you for your dedicated teaching, your generous guidance, and the invaluable wisdom you've shared. Your encouragement and commitment have left a lasting impact on my path, and I am truly thankful for all you've done.

Finally, I would like to sincerely thank the jury members for their time, valuable feedback, and constructive remarks which have contributed to the enrichment of this work.

#### **Ouffa Wissal**

All praise and thanks to Allah for granting me the strength, patience, and guidance throughout this work.

First and foremost, I would like to express my deepest gratitude to my dear mother, who has been my rock throughout this journey. I am forever grateful for the way she has always surrounded me with love and encouragement, offering unwavering support that made every step of this path lighter.

To my father, thank you for your strength, wisdom, and constant encouragement.

A heartfelt thank you as well to my beloved sister Majida and brother Athman your love, humor, and support have brought light to difficult moments, and I'm truly grateful to have you both by my side.

I am also deeply thankful to my precious fiancé for his continuous support, patience, and motivation during this entire journey. your understanding and belief in me have made even the most challenging moments easier to overcome, and your presence has been a constant source of comfort and inspiration.

I would like to sincerely thank my supervisor, Madame Naceur, for her valuable guidance, expertise, and continuous support. Her insightful advice and encouragement have greatly contributed to my academic and personal growth, and have made this journey both enriching and enjoyable.

Finally, I extend my sincere thanks to the jury members for taking the time to evaluate my work, and for their valuable feedback and contributions.

.

ملخص:

تقدّم هذه الرسالة نظام حوسبة طرفية لمراقبة الآلات الصناعية في الزمن الحقيقي، حيث يتم دمج المتحكم الدقيق إس تي إم 32 إف 103 آر بي مع نانو إدج إيه آي ستوديو لمراقبة حالة الآلة على الجهاز نفسه دون الاعتماد على السحابة. يتم التقاط بيانات الاهتزاز من المستشعر إم بي يو 6050 عبر دي إم إيه، وتحليلها باستخدام الذكاء الاصطناعي المدمج، ثم عرضها محلياً على شاشة أو إل إي دي، بالإضافة إلى إرسالها إلى لوحة تحكم ويب عبر ناقل كان ووحدة إي إس بي 32. تضمن لوحة إلكترونية مخصصة ذات 6 طبقات (بي سي بي) وهيكل برمجي معياري معالجة منخفضة التأخير وقابلية للتوسّع. توضح هذه الحلول كيف يمكن للذكاء الاصطناعي المدمج والخفيف أن يمكّن من الصيانة التنبؤية بتكلفة منخفضة

الكلمات المفتاحية:

الحوسبة الطرفية، إس تى إم 32، نانو إدج، دي إم إيه، بي سي بي

Résumé:

Ce mémoire présente un système d'edge computing pour la surveillance industrielle en temps réel, combinant le microcontrôleur STM32F103RB et l'outil NanoEdge AI Studio pour analyser l'état des machines en local, sans dépendance du cloud. Les données vibratoires d'un capteur MPU6050 sont acquises via DMA, analysées par une IA embarquée, puis affichées sur un écran OLED tout en étant transmises à un tableau de bord web (via le bus CAN et un ESP32). Une carte PCB personnalisée à 6 couches et une architecture firmware modulaire garantissent un traitement à faible latence ainsi qu'une évolutivité optimale. Cette solution illustre comment l'IA embarquée permet de mettre en œuvre une maintenance prédictive économique.

Mots-clés: Edge computing, STM32, NanoEdge, DMA, PCB

**Abstract:**

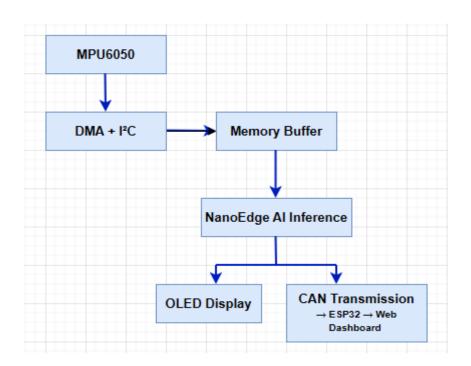

This thesis presents an edge-computing system for real-time industrial machine monitoring, combining an STM32F103RB microcontroller with NanoEdge AI Studio to Monitor Machine state on-device without cloud dependency. Vibration data from an MPU6050 sensor is captured via DMA, analyzed by embedded AI, and displayed locally on an OLED while being relayed to a web dashboard (via CAN bus and ESP32). A custom **6**-layer PCB and modular firmware architecture ensure low-latency processing and scalability. The solution demonstrates how lightweight embedded AI can enable cost-effective predictive maintenance.

Keywords: Edge-computing, STM32, NanoEdge, DMA, PCB

## List of acronyms and abbreviations

Al Artificial Intelligence

CAN Control Area Network

DMA Direct Memory Access

EAI Embedded Artificial intelligence

FFT Fast Fourier Transform

FPS Frame Per Second

GPIO General-Purpose Input/Output

HAL Hardware Abstraction Layer

HSE High-Speed External

I2C Inter Integrated Circuit

ICM Isolation Covariance Matrix

IPCA Incremental Principal Component Analysis

MCU Microcontroller Unit

MML Miniaturized Machine Learning

MPU6050 Motion Processing Unit 6050

OLED Organic Light Emitting

PCB Printed Circuit Board

PLL Phase-Locked Loop

RGB LED Red-Green-Blue Light Emitting Diode

USB Universal Serial Bus

ZSM Zero-Shot Model

# **Table of Contents**

| Gen  | General introduction1                                   |    |  |  |  |

|------|---------------------------------------------------------|----|--|--|--|

| Cha  | Chapter 13                                              |    |  |  |  |

|      |                                                         |    |  |  |  |

| 1.1. | Introduction                                            | 4  |  |  |  |

| 1.2. | Edge Computing and Embedded AI in Industrial Systems    |    |  |  |  |

|      | 1.1.1. Edge Computing definition                        |    |  |  |  |

|      | 1.1.2. Cloud and Edge Computing Paradigms               | 5  |  |  |  |

|      | 1.1.3. Embedded Artificial Intelligence                 | 7  |  |  |  |

|      | 1.1.4. Tiny ML                                          | 8  |  |  |  |

| 1.3. | Condition Monitoring                                    | 11 |  |  |  |

|      | 1.3.1. Predictive Maintenance and Condition Monitoring  |    |  |  |  |

|      | 1.3.2. Benefits of condition monitoring                 | 12 |  |  |  |

|      | 1.3.3. Types of Condition Monitoring                    |    |  |  |  |

| 1.4. | NanoEdge Al Overview                                    |    |  |  |  |

|      | 1.4.1. Definition                                       |    |  |  |  |

|      | 1.4.2. NanoEdge Al Library                              |    |  |  |  |

|      | 1.4.3. NanoEdge Al Studio capabilities                  |    |  |  |  |

|      | 1.4.4. NanoEdge Al Studio limitations                   |    |  |  |  |

| 1.5. | NanoEdge AI data format and Use Cases                   |    |  |  |  |

|      | 1.5.1. Time series versus cross sectional               |    |  |  |  |

|      | 1.5.2. Defining important concepts                      |    |  |  |  |

|      | 1.5.3. Designing a relevant sampling methodology        |    |  |  |  |

| 1.6. | STM32 Microcontroller Technology                        |    |  |  |  |

|      | 1.6.1. STM32 Overview                                   |    |  |  |  |

|      | 1.6.2. STM32F103RB                                      |    |  |  |  |

| 1.7. | Motion Sensors and Vibration Monitoring                 |    |  |  |  |

|      | 1.7.1. Motion sensors                                   |    |  |  |  |

|      | 1.7.2. Vibration monitoring                             |    |  |  |  |

|      | 1.7.3. Focus on Accelerometers for Vibration Monitoring | 25 |  |  |  |

| 1.8. | Hun    | nan-Machine Interfaces in Embedded Systems                        | .25 |

|------|--------|-------------------------------------------------------------------|-----|

|      | 1.8.1  | . The functionality of Human-Machine Interfaces (HMIs)            | 26  |

|      | 1.8.2  | . The Link Between HMI and Internet of Things (IoT)               | .26 |

| 1.9. | Con    | clusion                                                           | .27 |

|      |        |                                                                   |     |

|      | Cha    | pter 2                                                            | 29  |

|      |        |                                                                   |     |

| 2.1. | Inti   | oduction                                                          | .30 |

| 2.2. | Sys    | stem overview                                                     | 30  |

| 2.3. | Hai    | dware Design and Prototyping Process                              | 32  |

| 2    | 2.3.1. | Initial Microcontroller Testing                                   | 33  |

| 2    | 2.3.2. | Breadboard Functional Prototype                                   | 33  |

| 2    | 2.3.3. | Transition to a custom PCB                                        | .35 |

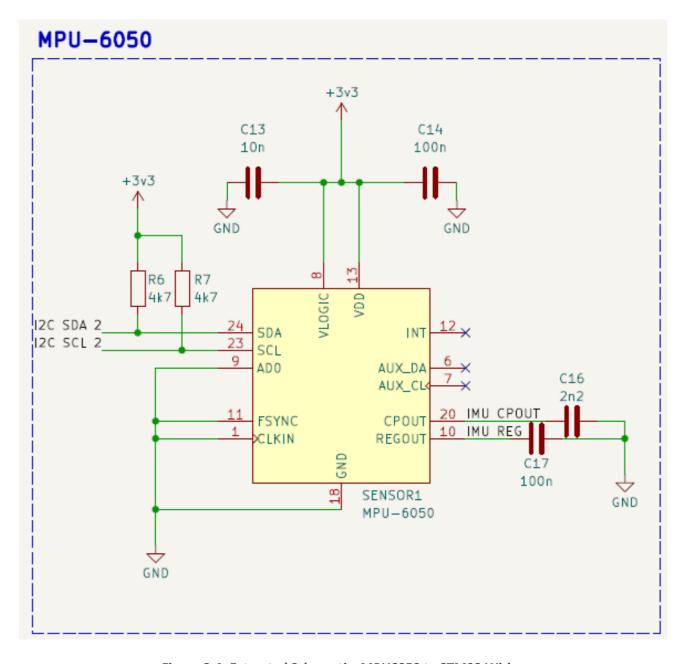

| 2.4. | Ser    | sor Integration: MPU6050                                          | 35  |

| 2    | 2.4.1. | Physical Connection via I <sup>2</sup> C                          | 35  |

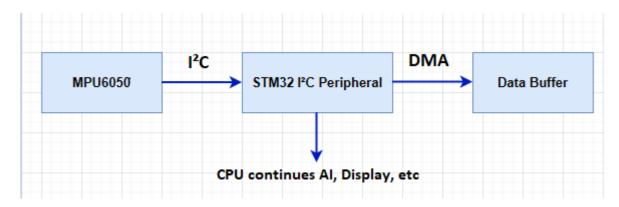

| 2    | 2.4.2. | I <sup>2</sup> C Communication and DMA Optimization               | .37 |

| 2    | 2.4.3. | Register Configuration and Initialization                         | 38  |

| 2    | 2.4.4. | Sampling Strategy with Interrupts                                 | 39  |

| 2    | 2.4.5. | Datasheet-Guided Design & Lessons Learned from Sensor Integration | .39 |

| 2.5. | Mic    | crocontroller Logic: STM32F103RB                                  | 41  |

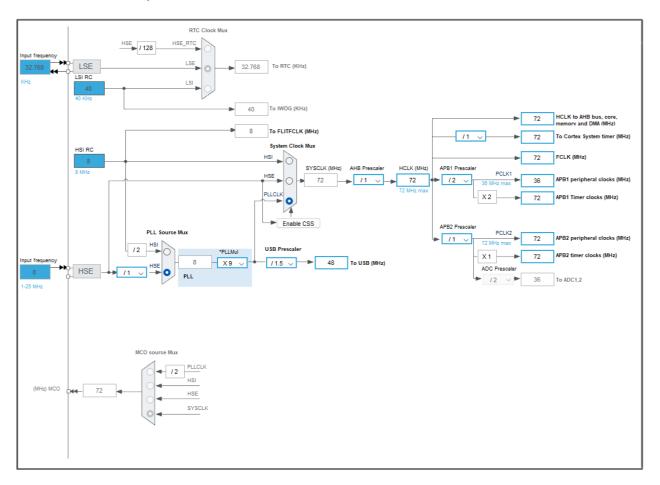

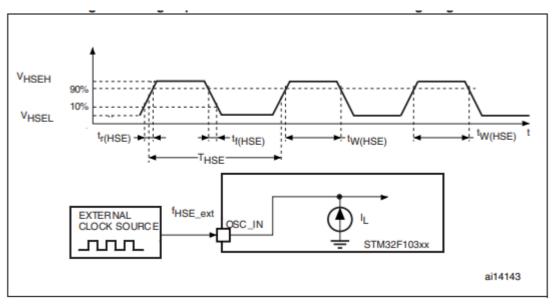

| 2    | 2.5.1. | Clock Configuration and Oscillator Selection                      | 41  |

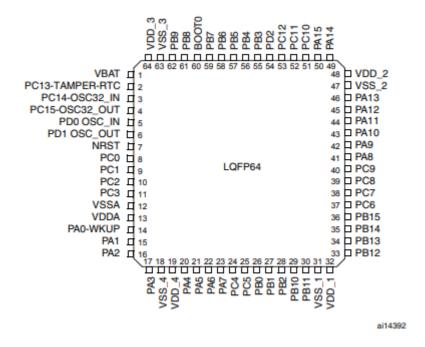

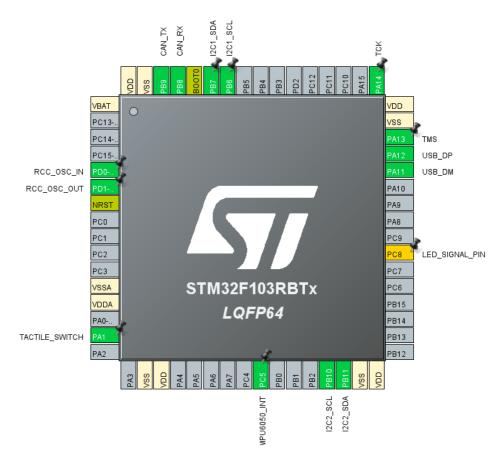

| 2    | 2.5.2. | Microcontroller Pin Configuration and Peripheral Mapping          | 43  |

| 2    | 2.5.3. | Peripheral Coordination and Simplifications                       | 46  |

| 2.6. | Naı    | noEdge AI Integration                                             | .47 |

| 2    | 2.6.1. | Sensor data collection and preparation                            | 47  |

| 2    | 2.6.2. | Time-Series Buffer Design for Edge Al                             | 47  |

| 2    | 2.6.3. | Other Algorithm Types Explored                                    | 52  |

| 2    | 2.6.4. | Model Deployment on STM32                                         | .53 |

| 2.7. | Dis    | play Layer: SSD1306 OLED                                          | .54 |

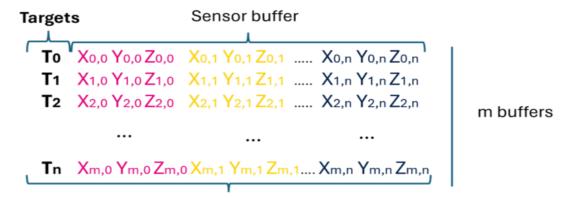

| 2    | 2.7.1. | Display Connection and Communication                              | .54 |

|        | 2.7.2.  | Display Modes: Eco vs Fast Refresh                     | 55  |

|--------|---------|--------------------------------------------------------|-----|

|        | 2.7.3.  | Visual Layout Design                                   | 55  |

| 2.8    | . Aux   | kiliary Components in the System Schematic             | 57  |

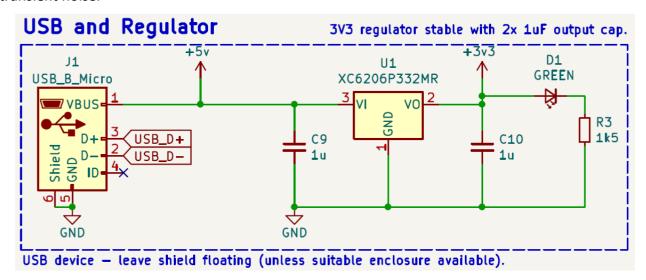

|        | 2.8.1.  | USB Interface and 3.3V LDO Regulator                   | 57  |

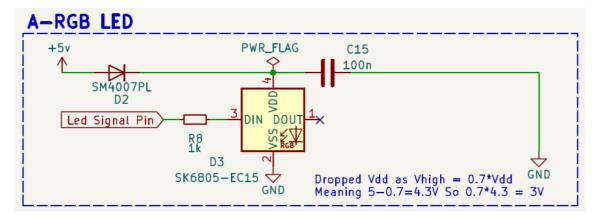

|        | 2.8.2.  | A-RGB LED                                              | 57  |

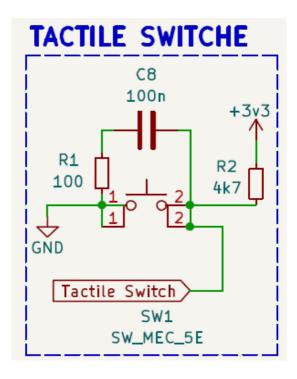

|        | 2.8.3.  | Tactile Switch (Boot/Reset)                            | .58 |

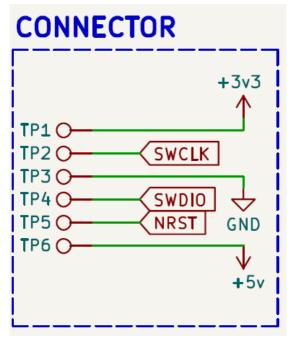

|        | 2.8.4.  | I/O Connectors and Expansion Headers                   | 59  |

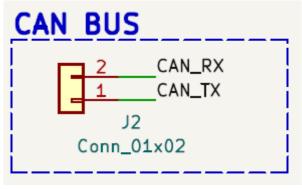

|        | 2.8.5.  | Can BUS                                                | 60  |

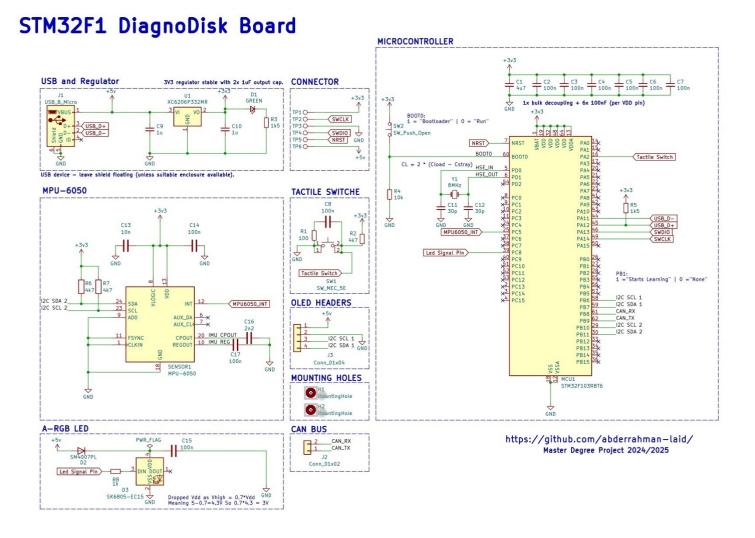

| 2.9    | . Full  | System Schematic                                       | 61  |

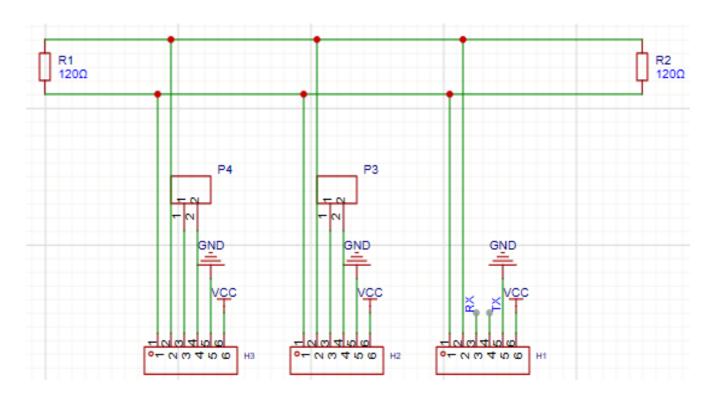

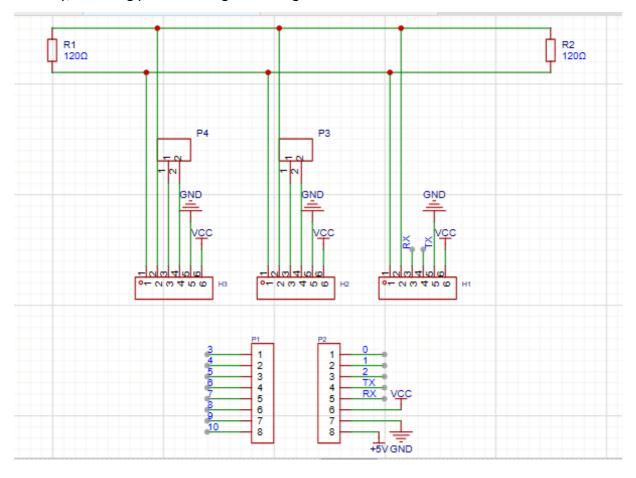

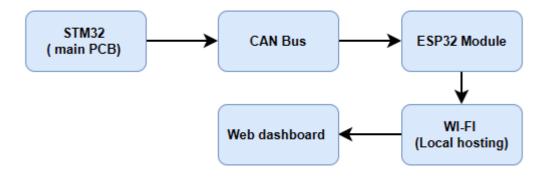

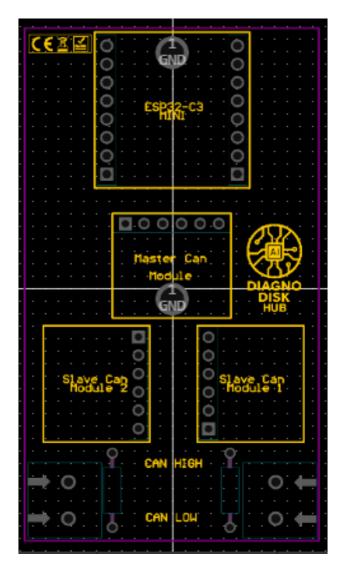

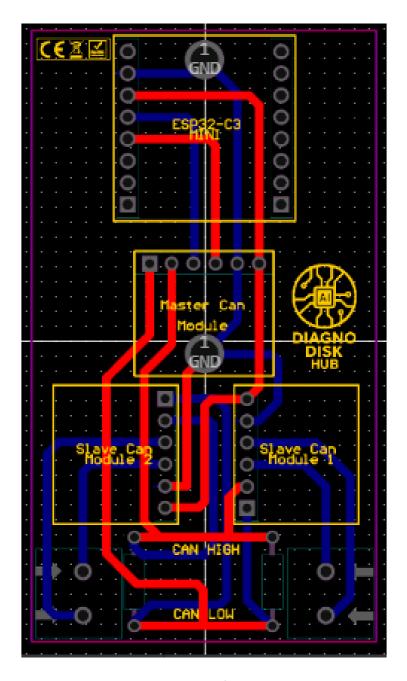

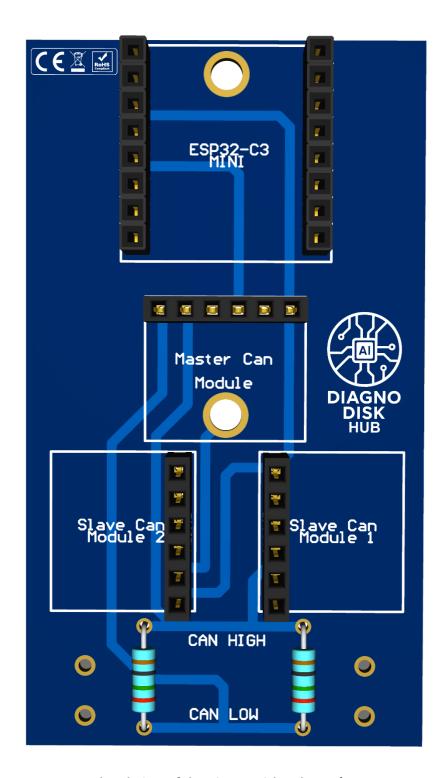

| 2.1    | 0. Out  | tput Interface Extension: ESP32 + CAN Bus Architecture | 62  |

|        | 2.10.1  | . Why a Remote Output Module Was Needed                | 63  |

|        | 2.10.2  | . Schematic Breakdown of the ESP32-CAN Module          | 63  |

|        | 2.10.3  | . Full Schematic of the ESP32-CAN Monitoring Board     | 66  |

|        | 2.10.4  | . System Role and Data Flow                            | .67 |

| 2 1    | 1 Cor   | nclusion                                               | 68  |

| 2.1.   | 1. CO.  |                                                        | 00  |

| Cha    | pter 3. |                                                        | 69  |

|        |         |                                                        |     |

| 3.1. I | ntrodu  | ction                                                  | 70  |

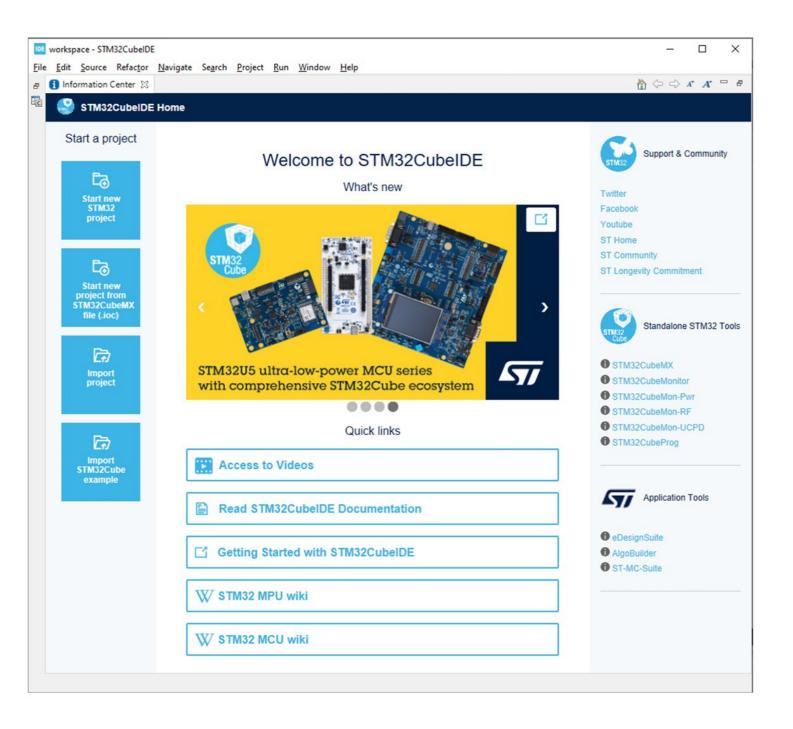

| 3.2.   | Develo  | pment Environment                                      | 70  |

|        | 3.2.1.  | STM32CubeIDE – Firmware Development & Debugging        | .71 |

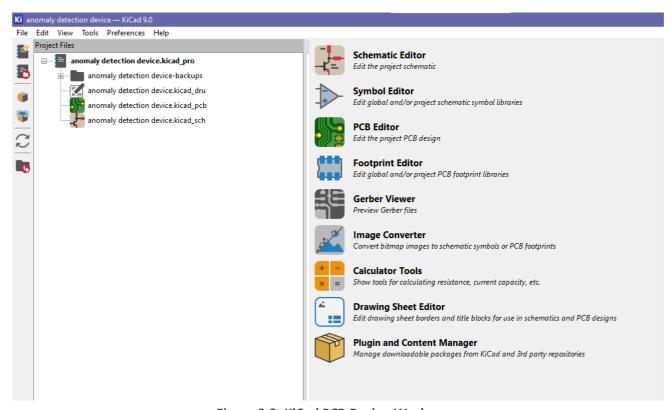

|        | 3.2.2.  | KiCad: Hardware Design from Schematic to Final Board   | 72  |

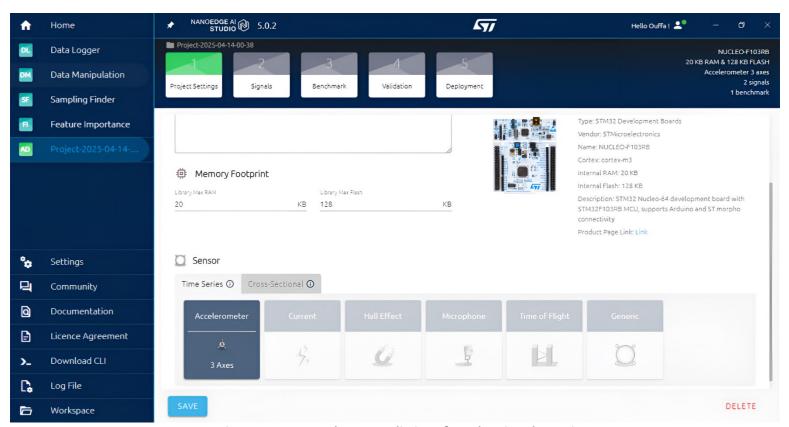

|        | 3.2.3.  | NanoEdge Al Studio: Embedded Al Training & Deployment  | 73  |

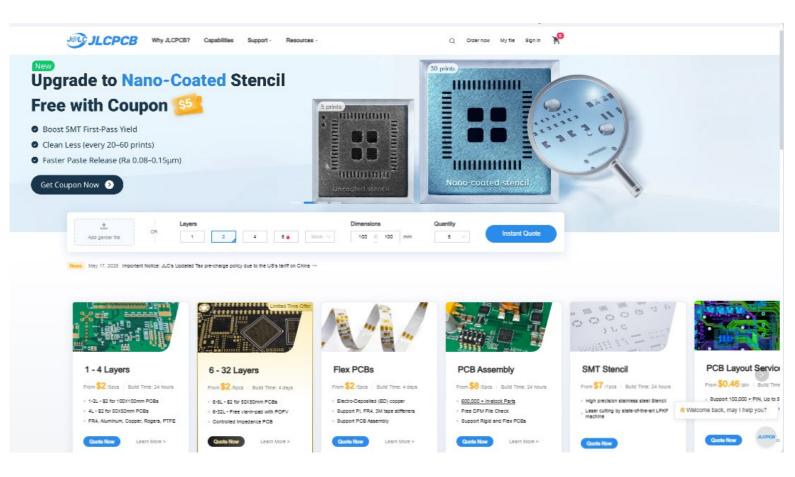

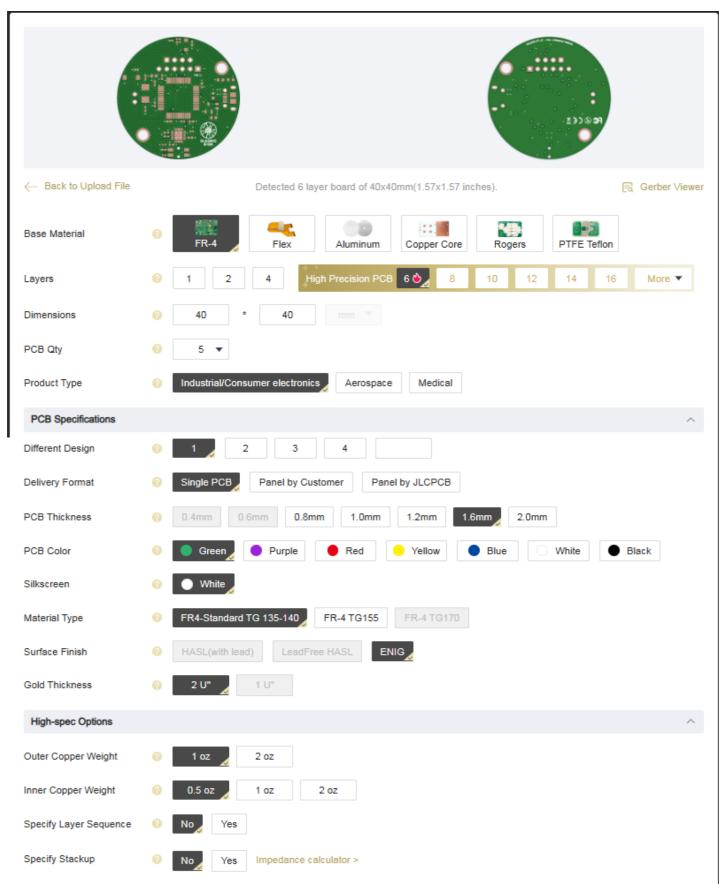

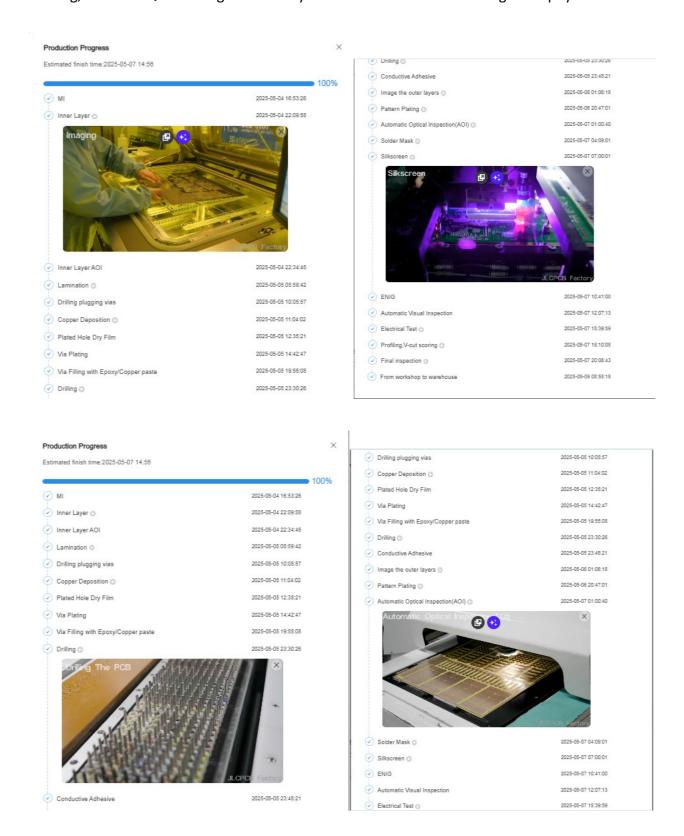

|        | 3.2.4.  | PCB Manufacturing and Assembly                         | 74  |

|        | 3.2.5.  | VS Code and PlatformIO Extension                       | 75  |

|        | 3.2.6.  | SNC ALMITECH: Manufacturing the second PCB             | 76  |

| 3.3.   | PCB I   | Fabrication and Assembly                               | 77  |

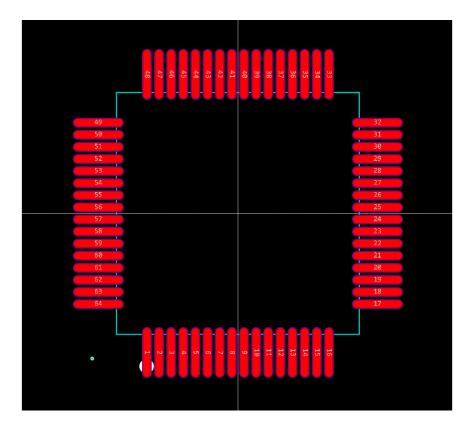

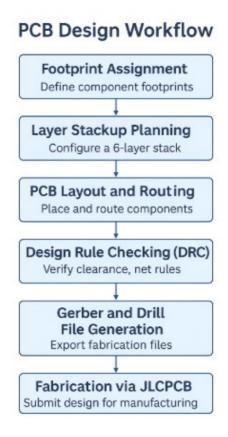

|        | 3.3.1.  | Design Workflow Overview                               | 78  |

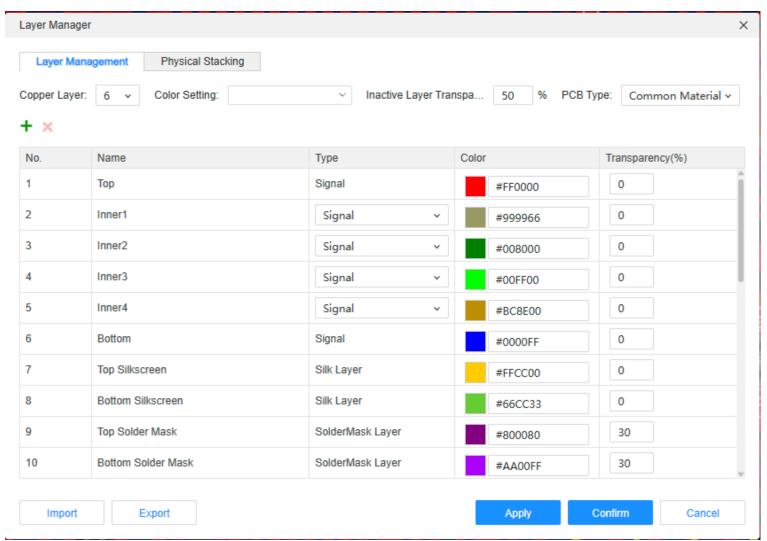

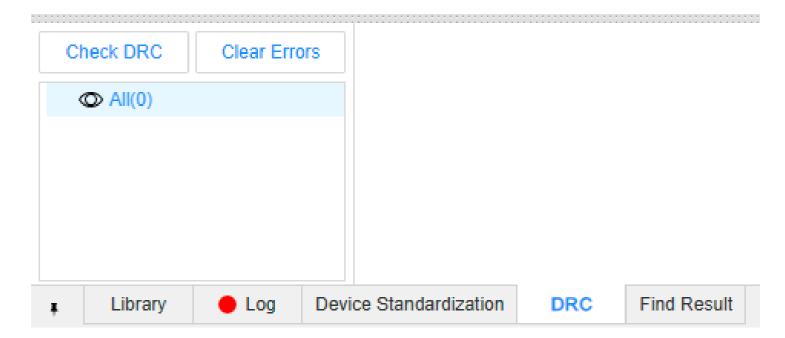

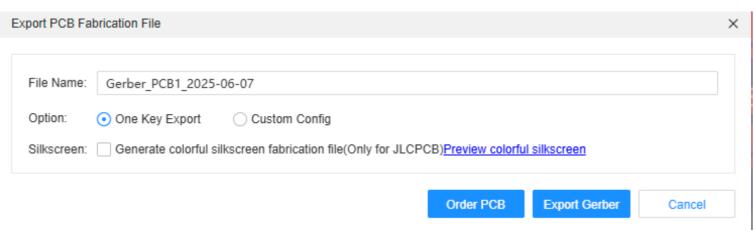

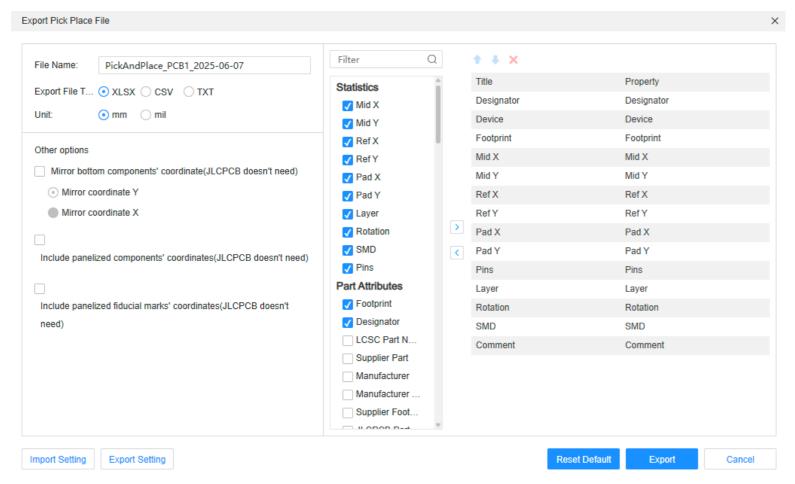

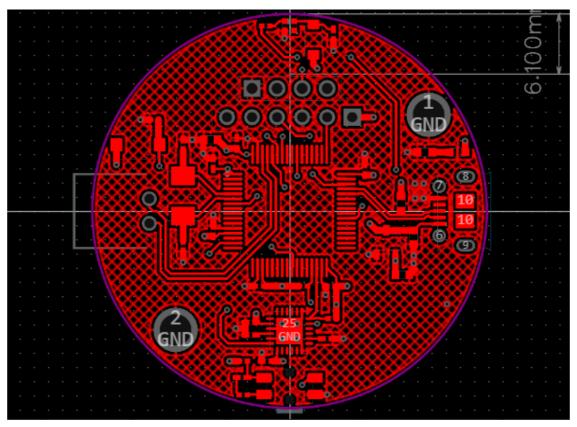

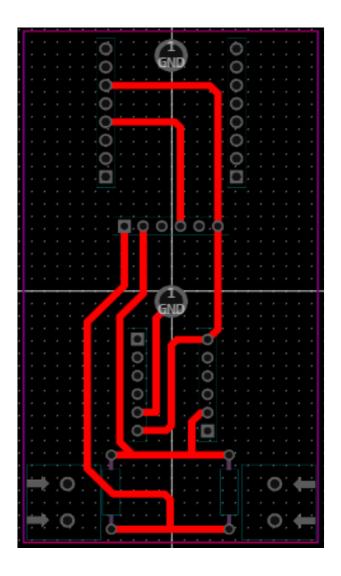

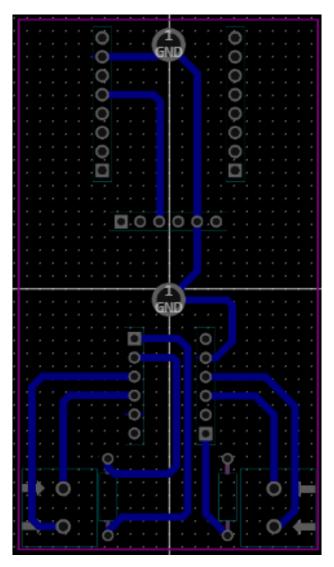

|        | 3.3.2.  | Layer-by-Layer PCB Breakdown                           | 85  |

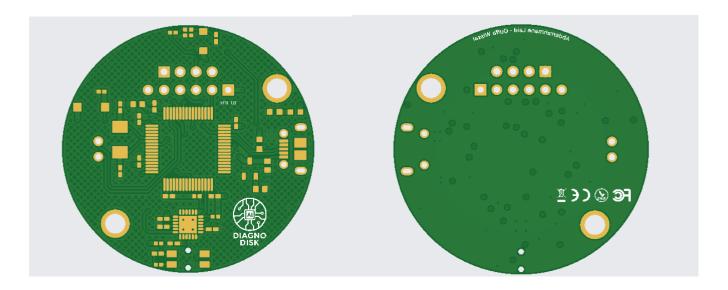

|        | 3.3.3.  | Final PCB Visualization & Assembly Overview            | 93  |

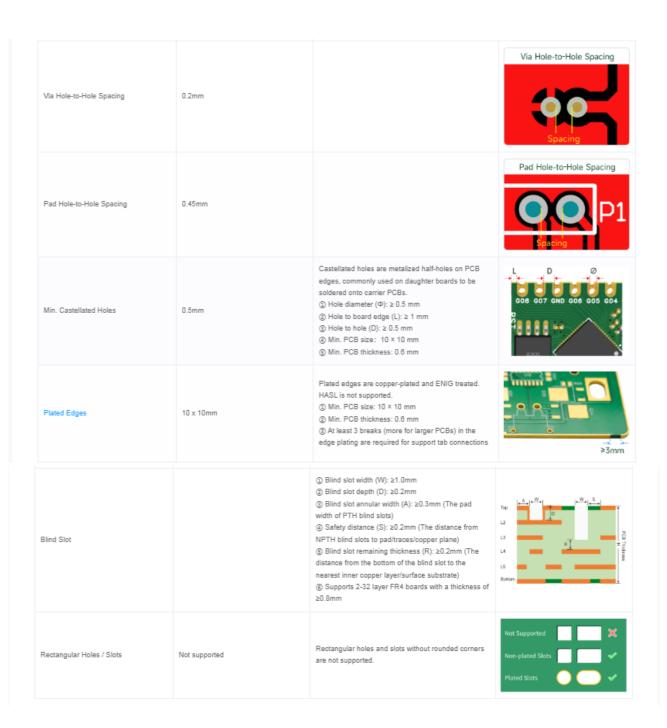

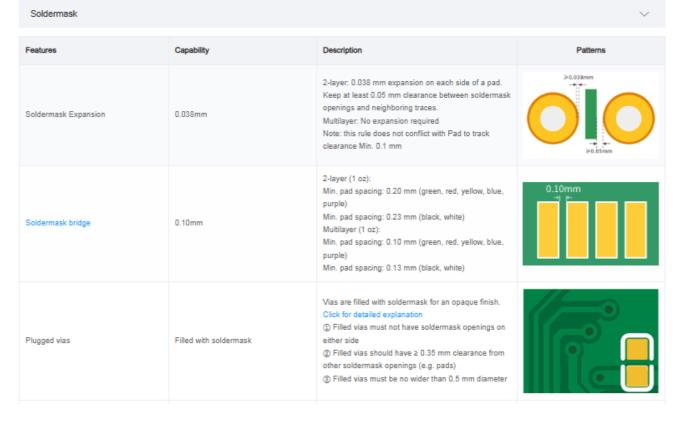

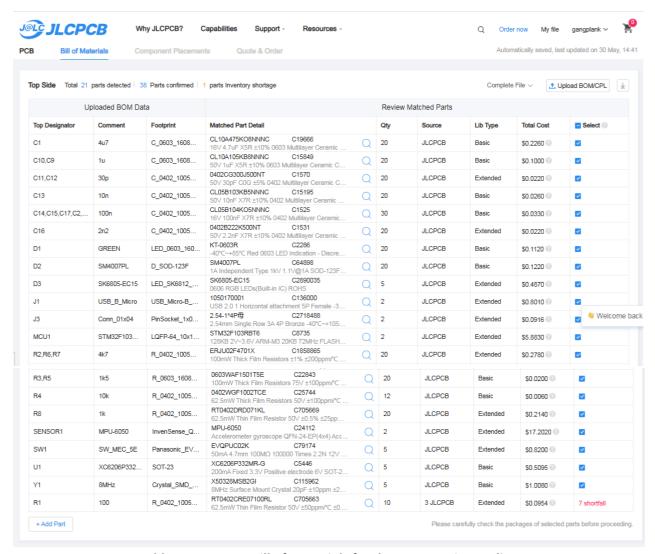

|        | 3.3.4.  | Capabilities of a 6-Layer Rigid PCB (via JLCPCB)       | 96  |

|        | 3.3.5.  | Final Bill of Materials (BOM)                          | 97  |

|       | 3.3.6.  | Lessons Learned and Manufacturing Tips                  | 97   |

|-------|---------|---------------------------------------------------------|------|

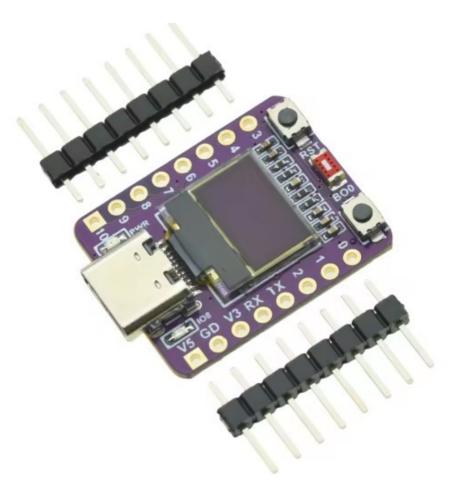

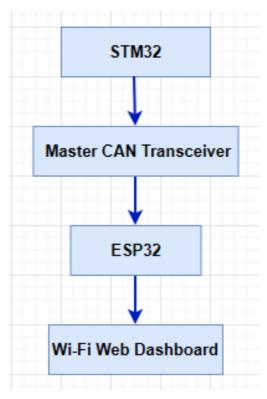

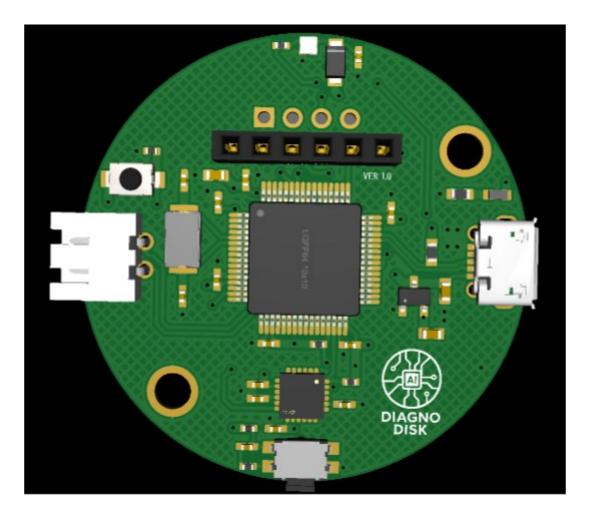

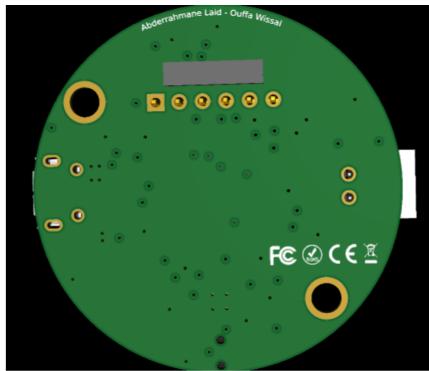

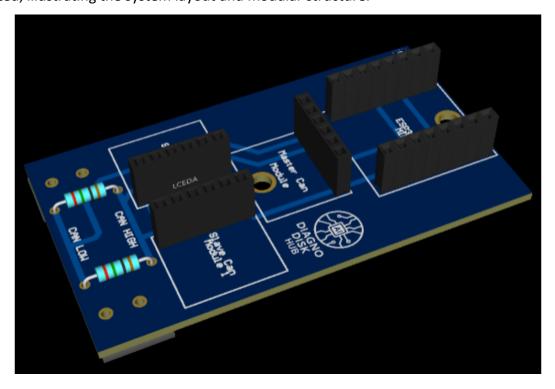

| 3.4.  | Wire    | less Result Transmission Module (ESP32 + CAN Interface) | 97   |

|       | 3.4.1.  | System Architecture Flow                                | 98   |

|       | 3.4.2.  | PCB Overview and 3D Rendering                           | 98   |

| 3.5.  | Firm    | ware Implementation and System Logic                    | 104  |

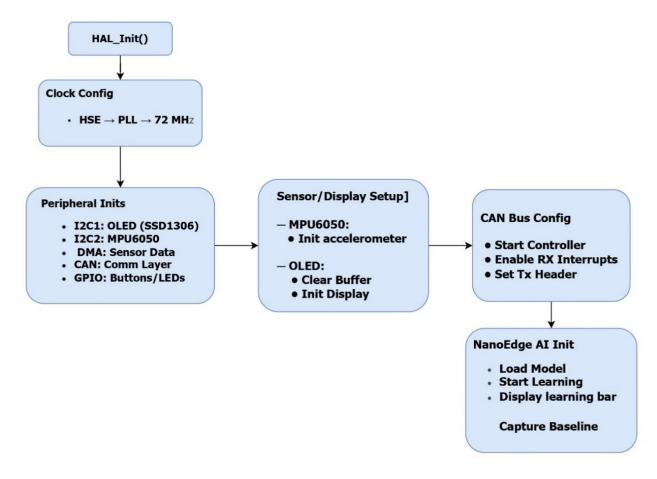

|       | 3.5.1.  | System Initialization Flow                              | 105  |

|       | 3.5.2.  | Peripheral Configuration                                | 106  |

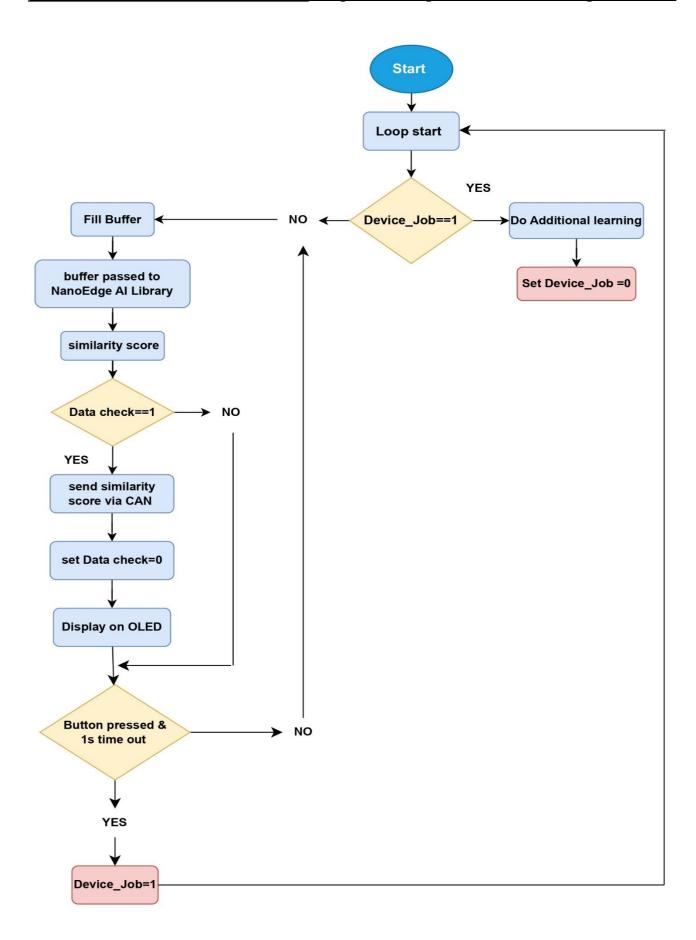

|       | 3.5.3.  | Task Flow in Main Loop                                  | .106 |

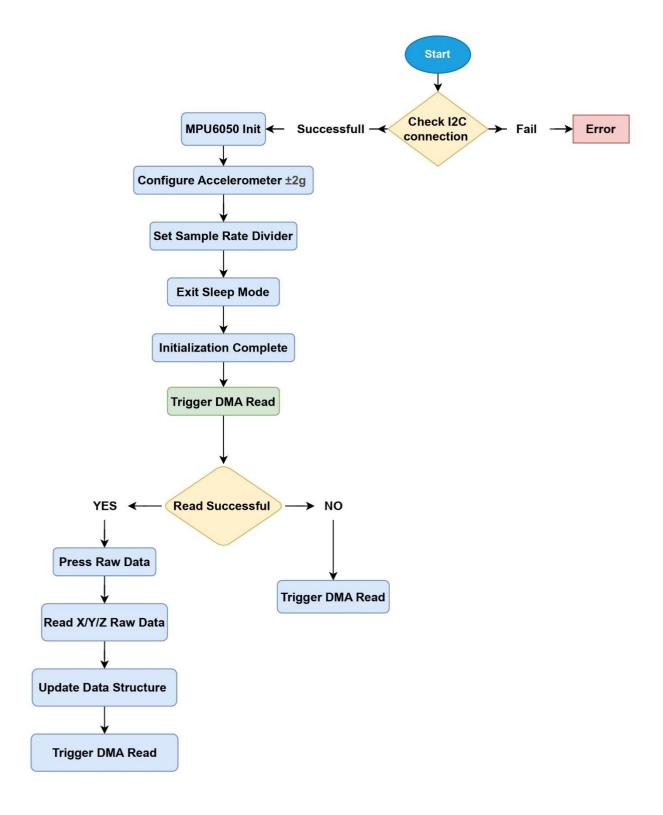

|       | 3.5.4.  | Sensor Interface with DMA: MPU6050 Data Handling        | 109  |

|       | 3.5.5.  | Embedded AI Integration: NanoEdge Inference Logic       | 110  |

|       | 3.5.6.  | Display Output: OLED Feedback                           | 111  |

|       | 3.5.7.  | CAN Transmission & ESP32 Web interface                  | 112  |

| 3.6.  | Nand    | DEdge AI Integration: Training and Evaluation           | .115 |

|       | 3.6.1.  | Signal import summary                                   | 115  |

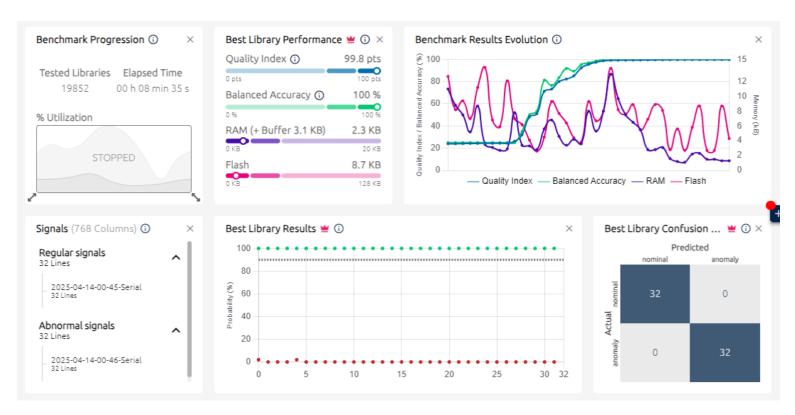

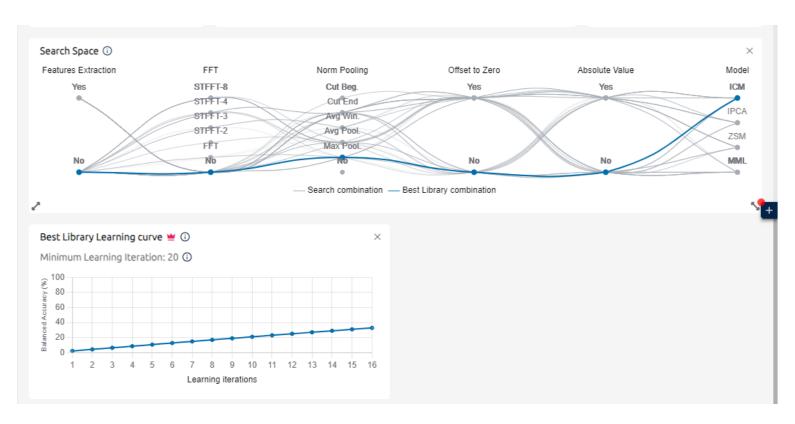

|       | 3.6.2.  | Benchmarking & Model Selection                          | 118  |

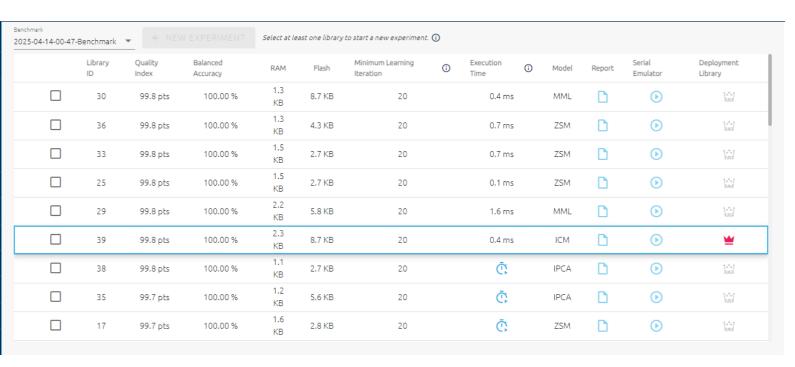

|       | 3.6.3.  | Model Validation and Library Selection                  | 120  |

| 3.7.  | Resu    | lts and System Evaluation                               | 125  |

|       | 3.7.1.  | State Visualization and OLED Feedback                   | 125  |

|       | 3.7.2.  | Inference Behavior and Response Time                    | 129  |

|       | 3.7.3.  | Score Consistency and Model Accuracy                    | 129  |

|       | 3.7.4.  | Result Transmission and Web Visualization               | 129  |

| 3.8.  | Conc    | lusion                                                  | 132  |

| Gen   | eral Co | onclusion                                               | 133  |

| Bibli | ographi | es                                                      | 135  |

| Арре  | endix   |                                                         | 137  |

# **List of figures**

| Figure 1.1: Conventional cloud computing structure                                                      | 5  |

|---------------------------------------------------------------------------------------------------------|----|

| Figure 1.2: Two-way computing streams in edge computing                                                 | 6  |

| Figure 1.3: NanoEdge AI Studio                                                                          | 13 |

| Figure 1.4: NanoEdge AI data format                                                                     | 16 |

| Figure1.5: STM32F103RB MCU                                                                              | 20 |

| Figure 1.6: Overview of STM32f103rb Internal Bus System and DMA Integration                             | 22 |

| Figure 1.7: MPU6050 Module                                                                              | 25 |

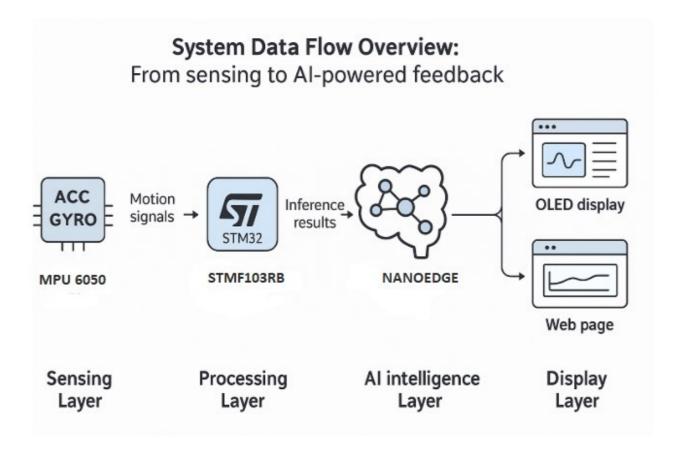

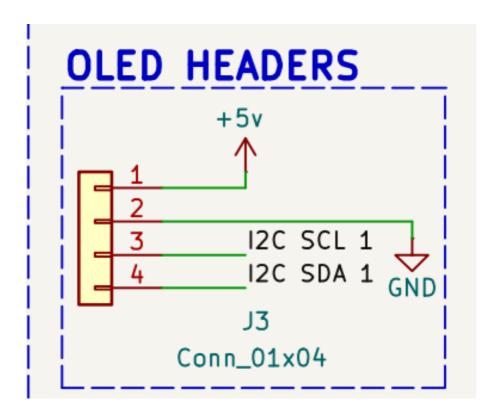

| Figure 2.1: System Data Flow Overview: From sensing to AI-powered feedback                              | 32 |

| Figure 2.2: LQFP64 support board for STM32F103RB                                                        | 33 |

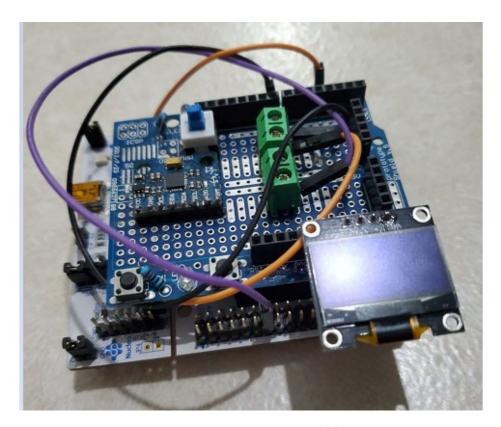

| Figure 2.3: Breadboard prototype of full system                                                         | 34 |

| Figure 2.4: Extracted Schematic: MPU6050 to STM32 Wiring                                                | 36 |

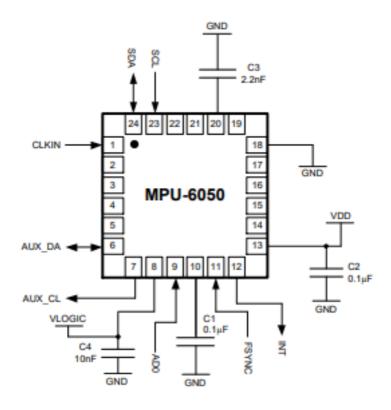

| Figure 2.5: MPU6050 Typical Operating Circuit                                                           | 37 |

| Figure 2.6: Efficient Data Path Using DMA and Interrupts                                                | 38 |

| Figure 2.7: Raw Signal Path from MPU6050 to AI Model                                                    | 39 |

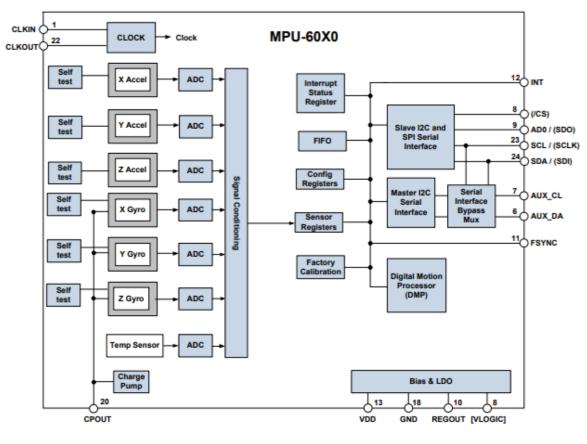

| Figure 2.8: MPU6050 Internal Architecture                                                               | 40 |

| Figure 2.9: Clock configuration with external HSE source and PLL for 72 MHz system clock                | 41 |

| Figure 2.10: High-speed external clock source AC timing diagram                                         | 42 |

| Figure 2.11: STM32F103xx performance line LQFP64 pinout                                                 | 43 |

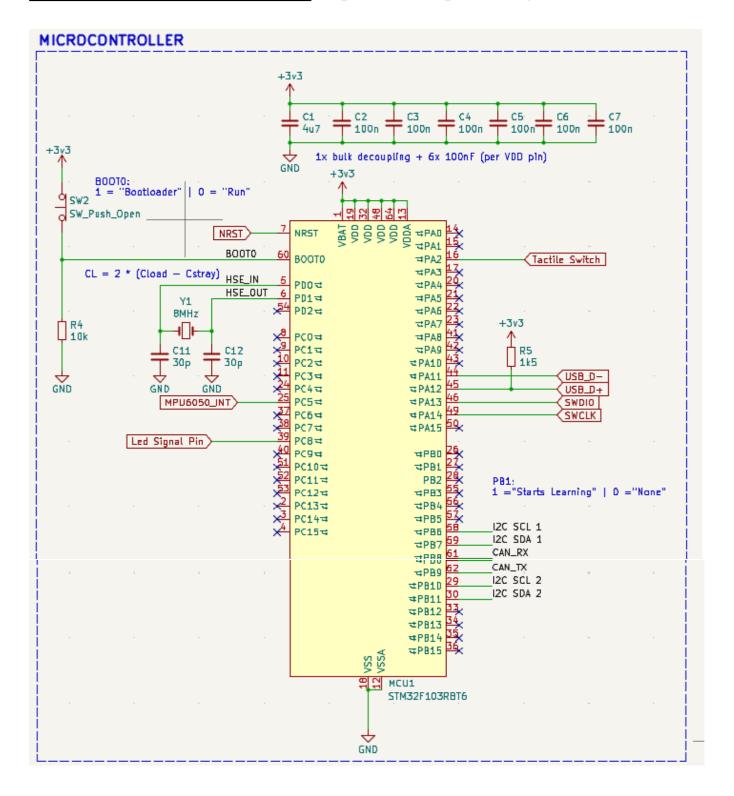

| Figure 2.12: STM32F103RB Extracted Schematic: Peripheral and Communication Mapping                      | 45 |

| Figure 2.13: Pin loading conditions                                                                     | 46 |

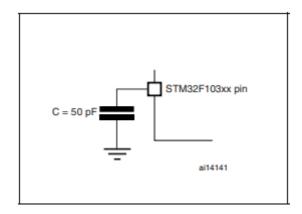

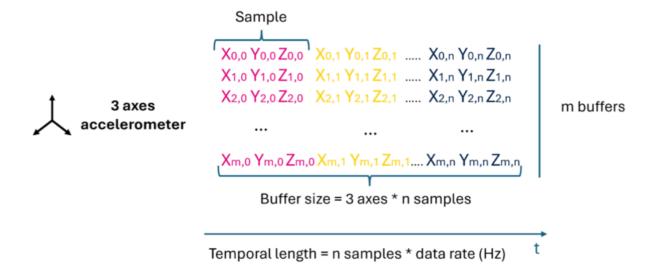

| Figure 2.14: sample vs buffer                                                                           | 48 |

| Figure 2.15: Difference between independent sample vs temporal buffer                                   | 49 |

| Figure 2.16: Basic format for (AD, NCC, 1CC)                                                            | 51 |

| Figure 2.17: Basic format for Extrapolation                                                             | 52 |

| Figure 2.18: Extracted view of the OLED to STM32 I <sup>2</sup> C wiring from the full system Schematic | 54 |

| Figure 2.19: Display Logic Flow                                                                         | 56 |

| figure 2.20: USB and Regulator Extracted Schematic                                                      | 57 |

| figure 2.21: A-RGB LED Extracted Schematic                                                              | 58 |

| figure 2.22: Tactile Switch Extracted Schematic                                                         | 59 |

| figure 2.23: Connector Extracted Schematic                                                              | 60 |

| figure 2.24: CAN BUS Extracted Schematic                                           | 60      |

|------------------------------------------------------------------------------------|---------|

| Figure 2.25: Full Schematic of the STM32 Main Board                                | 62      |

| figure 2.26: CAN bus transceivers Communication module                             | 64      |

| figure 2.27: The 3 CAN bus transceivers Extracted Schematic                        | 64      |

| figure 2.28: ESP32-C3                                                              | 65      |

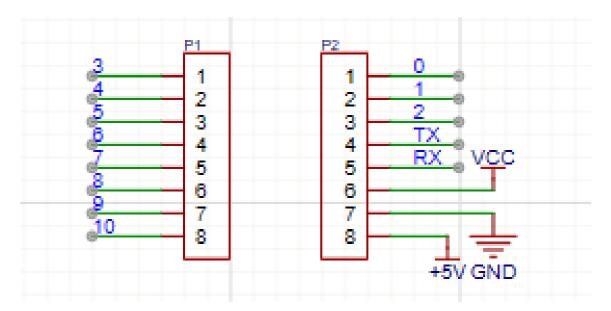

| Figure 2.29: Dual 8-pin connectors Extracted Schematic                             | 66      |

| Figure 2.30: ESP32-CAN Monitoring Board Schematic                                  | 66      |

| Figure 2.31: ESP32-CAN Monitoring Board Data Flow                                  | 67      |

| Figure 3.1: STM32Cube IDE Workspace                                                | 72      |

| Figure 3.2: KiCad PCB Design Workspace                                             | 73      |

| Figure 3.3: NanoEdge AI Studio interface showing the project                       | 74      |

| Figure 3. 4: JLCPCB Homepage                                                       | 75      |

| Figure 3.5: Platform IO extension in VS code                                       | 76      |

| Figure 3.6: ALMITECH Homepage                                                      | 77      |

| Figure 3.7: an example of the MCU footprint                                        | 79      |

| Figure 3.8: PCB Layers                                                             | 80      |

| Figure 3.9: checking Errors                                                        | 81      |

| Figure 3.10: Exporting PCB Gerber File                                             | 81      |

| Figure 3.11: Exporting Pick Place File                                             | 82      |

| Figure 3.12: PCB Manufacturing Order on JLCPCB                                     | 83      |

| Figure 3.13: PCB Production and Process in JLCPCB Factory                          | 84      |

| Figure 3.14: PCB Design Workflow from Schematic to Fabrication                     | 85      |

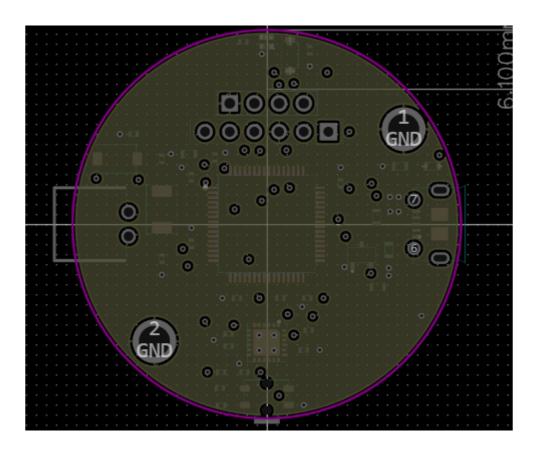

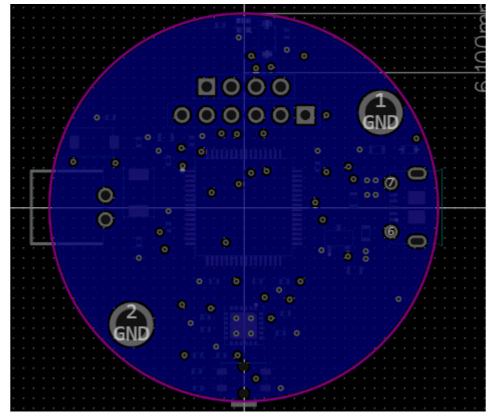

| Figure 3.15: Top Layer Primary Component and Signal Routing                        | 86      |

| Figure 3.16: Inner Layer 1 Solid Ground Plane (GND)                                | 87      |

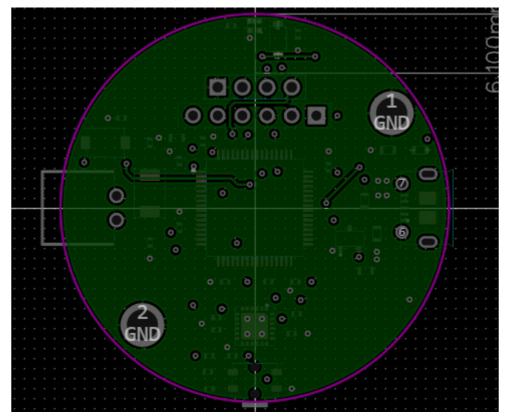

| Figure 3.17: Inner Layer 2 Mixed Signal and Ground Layer                           | 88      |

| Figure 3.18: Inner Layer 3 Secondary Signal and 5V Power Routing                   | 89      |

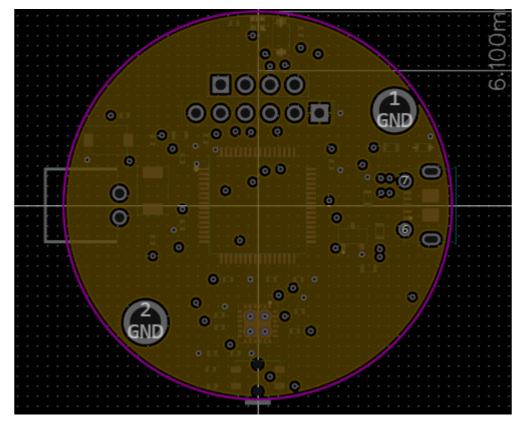

| Figure 3.19: Inner Layer 4: Dedicated 3.3V Power Plane                             | 90      |

| Figure 3.20: Bottom Layer: Secondary Ground Plane and Auxiliary Routing            | 91      |

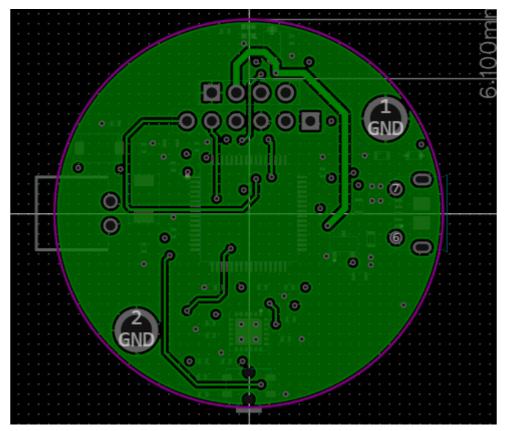

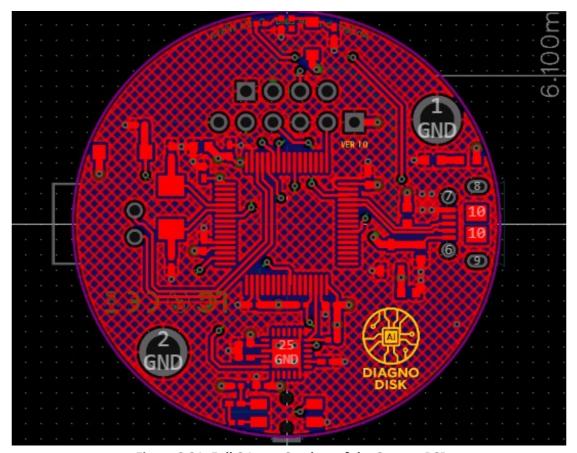

| Figure 3.21: Full 6-Layer Stackup of the Custom PCB                                | 92      |

| Figure 3.22: 2D Visualization of Bare PCB Structure (No Components) from top and b | ottom93 |

| Figure 3.23: Assembled 3D view for Diagno Disk (Top View)                          | 94      |

| Figure 3.24: Assembled 3D view for Diagno Disk (Bottom View)                       | 95      |

| Figure 3.25: Assembled 3D view for Diagno Disk (different angles)               | 95  |

|---------------------------------------------------------------------------------|-----|

| Figure 3.26: Final Fabricated Board (Real Image)                                | 96  |

| Figure 3.27: data flow of the system                                            | 98  |

| Figure 3.28: Top Copper Layer                                                   | 99  |

| Figure 3.29: Bottom Copper Layer                                                | 100 |

| Figure 3.30: Top Silkscreen                                                     | 101 |

| Figure 3.31 All Layers Routing of the Diagno Disk Hub PCB                       | 102 |

| Figure 3.32: 3D Rendered View of the Diagno Disk Hub PCB from the side          | 103 |

| Figure 3.33: 3D Rendered View of the Diagno Disk Hub PCB (ESP32 + CAN Interface | 104 |

| Figure 3.34: Firmware Initialization Flow                                       | 105 |

| Figure 3.35: STM32F103RB pin configuration in Cube IDE                          | 106 |

| Figure 3.36: Main loop Flowchart                                                | 107 |

| Figure 3.37: MPU6050 Initialization and Data Acquisition Workflow               | 109 |

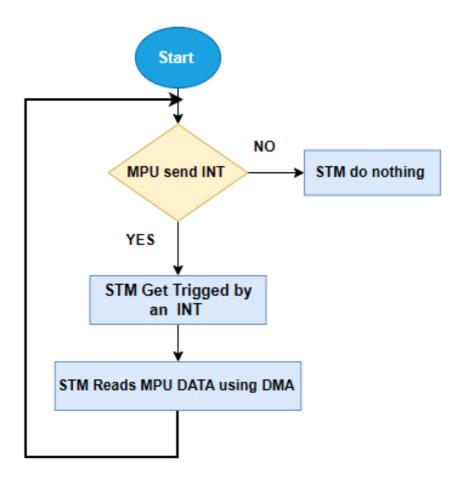

| Figure 3.38: Interruption workflow                                              | 110 |

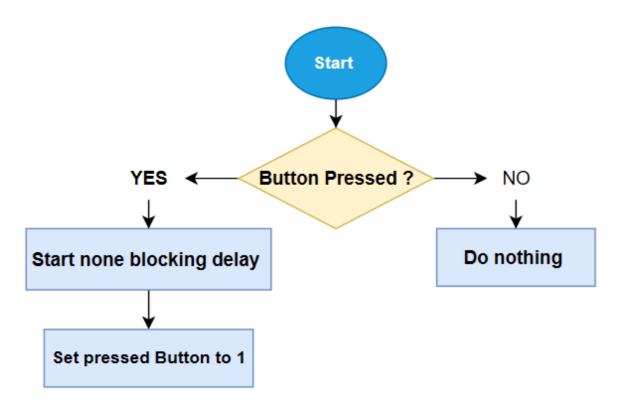

| Figure 3.39: Button Control Workflow                                            | 111 |

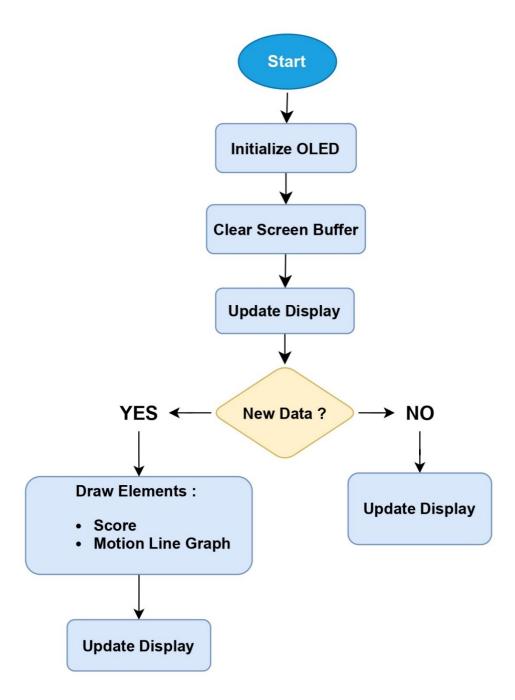

| Figure 3.40: Display Output Workflow                                            | 112 |

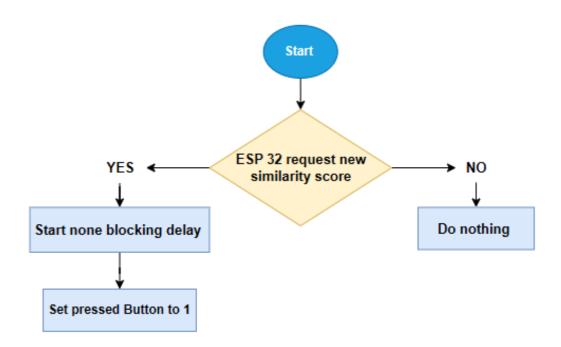

| Figure 3.41: The similarity request                                             | 113 |

| Figure 3.42: CAN Transmission Workflow                                          | 113 |

| Figure 3.43: ESP32 Continuous Data Acquisition and WebSocket Process            | 114 |

| Figure 3.44: Initial regular Signal Import Interface in NanoEdge AI Studio      | 115 |

| Figure 3.45: Initial abnormal Signal Import Interface in NanoEdge AI Studio     | 116 |

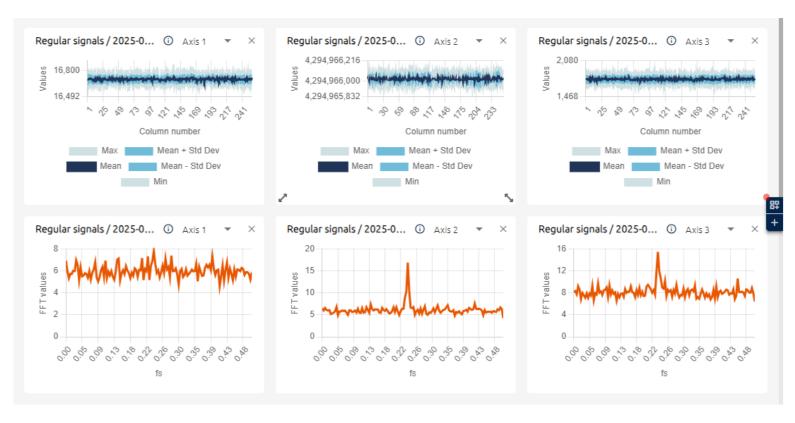

| Figure 3.46: Regular signal overview in NanoEdge AI Studio                      | 117 |

| Figure 3.47: Abnormal signal overview in NanoEdge AI Studio                     | 118 |

| Figure 3.48: Benchmark Progression overview in NanoEdge AI Studio               | 119 |

| Figure 3.49: Search Space overview in NanoEdge AI Studio                        | 120 |

| Figure 3.50: Validation overview in NanoEdge AI Studio                          | 121 |

| Figure 3.51: Failed Real-Time Classification by ZSM Model                       | 122 |

| Figure 3.52: ICM Model Validation Showing Accurate State Separation             | 123 |

| Figure 3.53: Final Library Report (ICM) Generated by NanoEdge AI Studio         | 124 |

| Figure 3.54: OLED Display Frames Under Various Conditions: idleidle             | 126 |

| Figure 3.55: OLED Display Frames Under Various Conditions: Transient anomaly    | 127 |

| Figure 3.56: OLED Display Frames Under Various Conditions: Severe anomaly | 128  |

|---------------------------------------------------------------------------|------|

| Figure 3.57: Web Dashboard Displaying Live Anomaly Score via ESP32 Module | .130 |

# List of tables

| Table 1.1: Comparison of STM32 Microcontroller Families            | 19  |

|--------------------------------------------------------------------|-----|

| Table 1.2: peripheral of STM32F103                                 | 21  |

| Table 1.3: Comparison table of motion sensors                      | 23  |

| Table 2.1: I <sup>2</sup> C Connections                            | 36  |

| Table 2.2: MPU6050 Register Initialization Summary                 | 38  |

| Table 2.3: I <sup>2</sup> C Timing Specification Table             | 14  |

| Table 2.4: I <sup>2</sup> C Connections for OLED                   | 54  |

| Table 2.5: pin configuration of the LED                            | 58  |

| Table 2.6: pin configuration for the Tactile Switch                | 59  |

| Table 3.1: Summary Comparison of ICM, IPCA, ZSM, MML               | 119 |

| Table 1: Core PCB Manufacturing Specifications                     | 138 |

| Table 2: Drill Capabilities and Hole Parameters                    | 139 |

| Table 3: Trace and Spacing Constraints                             | 140 |

| Table 4: Solder Mask Capabilities                                  | 141 |

| Table 5: Summary Bill of Materials for the 6-Layer Diagno disc PCB | 142 |

## **General introduction**

Machines are no longer just mechanical systems driven by simple commands they're becoming intelligent, adaptive, and connected. In today's industrial and research environments, the ability to sense, interpret, and act upon real-world data in real time is at the heart of *condition monitoring*, predictive maintenance, automation, and human-machine collaboration. As the pace of digitization accelerates, embedded systems are being tasked with more complex responsibilities, including running AI algorithms directly at the edge.

This thesis presents the complete development of a real-time, Al-powered embedded system designed for condition monitoring through detecting subtle changes in machine motion and reporting them through both local displays and remote dashboards. The goal was to create a small, self-contained unit that could sense motion, recognize machine behavior states, and communicate results, all using low-power hardware and no external processing.

We chose the STM32F103RB microcontroller as the core processor, known for its balance of performance and affordability, and built a 6-layer custom PCB that integrates key peripherals such as a motion sensor (MPU6050), OLED display, push button, CAN transceiver, and RGB indicator. The system was trained using NanoEdge AI Studio, a tool that enabled the generation of lightweight AI models capable of detecting machine behavior states in real time. To expand visibility beyond the local screen, we developed a secondary board based on ESP32, which received state results over CAN bus and hosted a live dashboard accessible via Wi-Fi.

This journey was not only technical, but also conceptual: how do you bring meaningful intelligence to microcontrollers? And how do you make that intelligence visible and practical in real-world use? To make this project both technically rich and clear to understand, the thesis is organized into three chapters:

- Chapter 1 lays the groundwork. It explores the evolution of embedded AI and edge computing, the challenges of machine state monitoring, and why tools like NanoEdge AI are essential for enabling intelligence on small devices.

- **Chapter 2** describes the design process, from early breadboard prototyping to hardware architecture and software conception. Here, each component is introduced with its role in sensing, processing, displaying, and transmitting machine behavior.

- Chapter 3 brings everything to life. It covers the firmware implementation, PCB fabrication,

model evaluation using NanoEdge Al Studio, and final results. This chapter includes testing scenarios, visualization strategies, and the full deployment setup both on-screen and wirelessly.

By integrating embedded intelligence, compact hardware, and dual visualization layers, this thesis demonstrates how real-time state detection can be achieved on microcontrollers and how these systems can be made robust, scalable, and ready for real-world deployment.

# Chapter 1

General Concepts

#### 1.1. Introduction

Machines are becoming smarter, faster, and more independent. As technology moves forward, the ability to monitor what machines are doing and how they're behaving what's commonly called *condition monitoring*—has become more important than ever. Thanks to edge computing and embedded AI, it's now possible to bring intelligence directly into small devices, allowing real-time decisions without always relying on the cloud.

This first chapter sets the stage for everything that follows. It looks at the big ideas behind embedded monitoring systems and condition monitoring, starting with what edge computing and embedded AI really mean, and how movements like TinyML are shaping this new generation of technology.

Because of how central it is to the project, special attention is given to NanoEdge Al Studio, the tool we used to create machine learning models that work directly on our microcontroller.

Finally, we introduce the STM32F103RB microcontroller, the heart of the system, and explain why it was chosen to power the real-time monitoring, decision-making, and condition monitoring capabilities we needed.

By building a solid understanding of these technologies and concepts, we can better appreciate the design and choices that come together in the system described in the next chapters.

### 1.2. Edge Computing and Embedded AI in Industrial Systems

#### 1.2.1. Edge Computing definition

Edge computing refers to processing, analyzing, and storing data closer to where it is generated to enable rapid, near real-time analysis and response. In recent years, some companies have consolidated operations by centralizing data storage and computing in the cloud. But the demands of new use cases enabled by billions of distributed devices from advanced warehouse and inventory management solutions to vision-enhanced robotic manufacturing lines to advanced smart cities traffic control systems have made this model unsustainable.

Additionally, the increased use of edge devices from Internet of Things (IoT) devices, such as smart cameras, mobile point-of-sale kiosks, medical sensors, and industrial PCs to gateways and computing infrastructure for faster, near real-time actionable insights at the data source is driving exponential growth in the amount of data generated and collected. Edge computing provides a

path to reap the benefits of data collected from devices through high-performance processing, lowlatency connectivity, and secure platforms. [1]

#### 1.2.2. Cloud and Edge Computing Paradigms

Massive amounts of data are generated every second by power transmission networks. In 2023, the world generated approximately 123 zettabytes of data, according to International Data Corporation. Advanced data analytic algorithms are used to transform such data into information and knowledge, which can be then used for network operations and/or parent energy services. Such data analytics rely upon information and communication technologies (ICTs): they have a critical role in data collection, transfer and processing. Computing is a critical function of ICTs: it determines how data analytics typical of transmission networks are performed, and thus becomes the foundation for transmission network operations and services.

Cloud Computing, geo-distributed devices and equipment are connected to cloud data centers, supporting centralized decisions and issuing control orders. The cloud is an abstraction which separates the actions of storing, retrieving and computing on data from the physical constraints of doing so.[2]

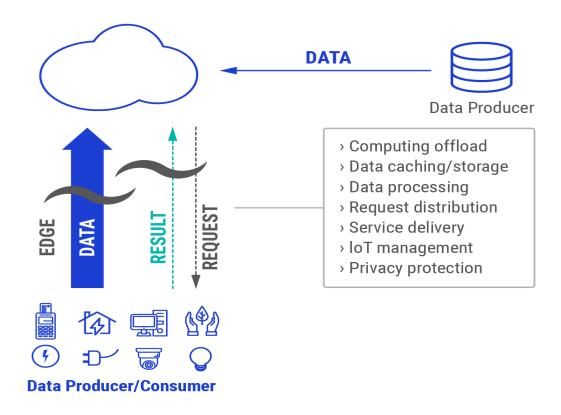

The schematics below (figure 1.1 [2]) illustrate the conventional cloud computing structure.

Figure 1.1: Conventional cloud computing structure.

- Data producers generate raw data and transfer it to a cloud.

- Data consumers send requests for consuming data to this cloud.

However, the cloud is no longer just a storage shed. Its users demand that it contributes a lot more to computing tasks and more quickly than ever before. This is the case of Internet of Things IoT solutions, which will empower Transmission System Operators (TSOs). The quantity of raw data produced by TSOs will be huge: it will make conventional cloud computing not efficient enough to

handle the computing demand. This means that most of the data produced by IoT will be consumed at the "edge of the telecommunication networks".

The schematics below (figure 1.2 [2]) illustrates the two-way computing streams in edge computing: the "things" are not only data consumers but also play as data producers. At the edge, the things can not only request service and content from the cloud but also perform the computing tasks from the cloud. Edge performs computing offloading, data storage, caching, and processing. It also distributes request and delivery service from cloud to users.

Figure 1.2: Two-way computing streams in edge computing.

Three types of architecture are described for practical **Cloud Computing (CC)** and **Edge Computing (EC)** implementations in power transmission networks:

• "Thing" tier: This layer is widely addressed in the context of the IoT. The thing tier covers most of the electrical equipment and the communication access in the so-called Smart Grids (SG). This tier oversees the operations of SG and realizing operation/control orders. Communication connections need to be established to transfer data to high layers.

- "Edge" tier: The edge tier contains the intermediate storing; communication "edge" is a relative concept. For instance, "smart metering" belongs:

- to the thing tier when it performs sensing and transferring data

- to the edge layer when it becomes a platform for home energy analytics (computation).

- "Cloud" tier: This tier consists of control, storing and computing centers. Compared with the

edge tier, the clouds are designated with high- performance storage and computing elements.

These powerful resources are deployed to perform complex analyses with a long-term time

scale and a grid-wide geographical scope. [2]

#### A) Challenges in exploiting the full potential of CC and EC

- Limited bandwidth resources

- Heterogeneous working environments

- Naming The naming scheme for EC needs to handle the mobility of things, a highly dynamic network topology, and privacy and security protection, as well as the scalability targeting the extremely large amount of unreliability

- Data Abstraction

- Service Management

- Privacy and Security concerns

- Optimization Metrics In EC there are multiple layers with different computation capabilities.

Workload allocation becomes an issue i.e. which layer to handle the workload or how many tasks to assign at each part

- Dynamic workload allocation.[2]

#### 1.2.3. Embedded Artificial Intelligence

Embedded AI, or EAI, refers to integrating artificial intelligence into embedded systems, allowing devices to process data and make decisions autonomously. Unlike traditional AI models that rely on cloud-based infrastructure, embedded AI operates within edge devices, processing sensor data in real time. This leads to faster and more efficient operations without depending on constant connectivity.

At its core, embedded AI takes AI capabilities – such as neural networks and convolutional models – and embeds them into low-power, high-performance devices.

Whether in microcontrollers for industrial automation or AI-powered smartphones, embedded AI reduces the need for external servers, optimizes local data processing, and empowers devices to make independent, real-time decisions.[3]

#### Why Embedded AI Matters:

- Real-Time Intelligence: Devices can analyze and act on data instantly, such as detecting abnormal vibrations in machinery before a fault occurs.

- **Enhanced Data Privacy**: Sensitive information, like biometric or health data, can be processed locally, reducing security risks.

- **Reliability in Harsh Environments**: Edge devices remain functional even in remote or disconnected areas (e.g., offshore oil platforms or isolated manufacturing sites).

Industries including healthcare, industrial IoT, smart homes, autonomous vehicles, and energy infrastructure are increasingly adopting embedded AI to enable smarter, faster, and more secure decision-making at the edge.[3]

#### 1.2.4. Tiny ML

Tiny Machine Learning (TinyML) is a breakthrough in artificial intelligence (AI) that enables machine learning (ML) models to run on ultra-low-power microcontrollers instead of traditional cloud-based data centers. This advancement significantly reduces energy consumption, enhances data security, and allows real-time AI processing. With applications spanning across smart cities, precision agriculture, industrial automation, healthcare, and wearable AI, TinyML is trans- forming the way AI is deployed in constrained environments. Understanding TinyML Unlike traditional ML, which relies on large computing infrastructure with ample processing power, memory, and cloud storage, TinyML integrates three key components to function efficiently on constrained devices Hardware, Software, Optimized ML Algorithms. [4]

#### A) Application of TinyML

TinyML allows real-time edge machine learning using inference on low-power microcontrollers. This has created a wide range of applications in healthcare, agriculture, home automation, industry, and environmental monitoring. In healthcare, TinyML-based wearable devices can track vital signs like heart rate or oxygen saturation and detect anomalies locally without requiring cloud connectivity, ensuring privacy and having immediate alerts. Likewise, in farming, sensors based on TinyML can monitor soil composition, identify pests, and forecast plant disease—even in locations with sparse internet access.

Smart home solutions are enhanced by TinyML through always-on, low-power, edge devices capable of voice recognition, environmental audio detection, or control of lights and appliances as a function of occupancy—all of which are user-privacy-enabled through on-device processing of the data. In industrial settings, TinyML is used for predictive maintenance, where it detects equipment anomalies using real-time sensor data, avoiding failures and reducing downtime. Environmental applications include tracking air or water quality using battery-powered sensors that process and act on data locally, which is ideal for mass deployment in urban or rural environments. From wildlife conservation to smart traffic systems, TinyML is destined to be a cornerstone for smart edge computing, driving smarter, more efficient, and greener applications in daily environments. [5]

#### B) Key components of TinyML System

#### Development Platforms and Tools

**TensorFlow Lite Micro** is perhaps the most popular alternative to run ML models on microcontrollers. It offers a highly optimized runtime to execute TensorFlow models on devices with at least 16 KB of RAM. It includes integer-only models and is specially built to execute without an operating system.

**Edge Impulse** is an extremely popular platform for training, developing, and deploying TinyML models. It provides a simple-to-use interface for model development, data collection, and deployment on embedded hardware. It has an impressive number of supported development boards and sensors, which makes it a good choice for quick prototyping.

**Arduino IDE and PlatformIO** are used extensively in programming microcontrollers. Through libraries specific to TinyML like Arduino\_TensorFlowLite, programmers are able to integrate machine learning models directly into Arduino-based applications. [5]

#### > Frameworks for Optimization and Inference

**The ARM CMSIS-NN** library contains very optimized kernels for neural networks aimed at boosting performance on the Cortex-M microcontrollers. The inference performance on embedded systems is smooth due to the extremely limited memory usage and high performance it provides.

**uTensor** is an inference engine specifically designed for embedded systems, which makes it incredibly light. Because it is developed to fit seamlessly into TensorFlow models, deployment of ML on Cortex-M boards, which are considerably resource-limited, can be done without losing too much performance or accuracy. [5]

#### > Hardware Platforms

**ARM Cortex-M series** microcontrollers such as the M3, M4, and M7 are some of the most commonly used chips in TinyML solutions. These processors balance low power and sufficient computing to be able to execute elementary ML inference.

Arduino Nano 33 BLE Sense is a miniature board featuring an ARM Cortex-M4 processor and a set of onboard sensors (microphone, accelerometer, temperature) that allows it to be a good platform for TinyML exploration and teaching. ESP32's dual core processor and embedded Wi-Fi/Bluetooth offer additional processing and memory functions compared to the usual microcontrollers, which allow developers to run somewhat more advanced models at the edge.

**STM32** series microcontrollers by STMicroelectronics are widely utilized in industrial TinyML applications. The boards support various sizes of memory and peripherial options and are compatible with a lot of ML frameworks as well as toolchains [5]

#### C) Advantages of TinyML

There are a number of advantages with running tinyML machine learning models on embedded devices.

- Low Latency: Since the machine learning model runs on the edge, the data doesn't have to be sent to a server to run inference. This reduces the latency of the output.

- Low Power Consumption: Microcontrollers are ultra-low power which means that they

consume very little power. This enables them to run without being charged for a really long

time.

- Low Bandwidth: As the data doesn't have to be sent to the server constantly, less internet bandwidth is used.

- **Privacy:** Since the machine learning model is running on the edge, the data is not stored in the cloud. [6]

#### 1.3. Condition Monitoring

Condition monitoring is a systematic process that involves the continuous assessment of the health and performance of machines, equipment, and systems in an industrial setting. The primary objective of condition monitoring is to detect any deviations from normal operation and identify potential issues before they result in downtime or failures. This is a proactive method of maintenance that allows organizations to make educated decisions regarding repairs and replacements, optimizing various maintenance efforts and reducing overall operational costs. At the core of any effective condition monitoring system are specialized condition monitoring solutions and condition monitoring equipment. These tools collect and analyze data from various sensors and devices strategically placed throughout the factory or production facility.[7]

#### 1.3.1. Predictive Maintenance and Condition Monitoring

Predictive maintenance is a maintenance strategy that aims to predict when equipment is likely to fail so that maintenance can be performed in due time to prevent the failure. It contrasts with traditional reactive maintenance, which involves fixing equipment after it has already failed, and preventive maintenance, which follows a fixed schedule regardless of the actual condition of the equipment. Both these methods result in high costs, either due to failure-derived downtime, or unnecessary replacement of costly components and equipment.

Condition monitoring plays a vital role in predictive maintenance. By continuously monitoring the health and performance of equipment, condition monitoring systems identify early warning signs of potential issues. Such signs may be abnormal vibrations, temperature fluctuations, clamping force,

or changes in fluid flow patterns. These can be indicative of looming problems. The ability to detect these precautionary signs in real-time allows maintenance professionals to act on them before actual issues occur.[7]

#### 1.3.2. Benefits of condition monitoring

Condition monitoring offers several other advantages over traditional maintenance approaches, including:

**Improved maintenance planning:** Condition monitoring provides real-time data on the performance of a system or component, which can be used to optimize maintenance planning and scheduling. This data helps to reduce the frequency of maintenance activities, while ensuring that they are executed only when needed, based on actual system performance.

**Increased equipment lifespan:** By detecting and addressing problems preemptively, condition monitoring helps to extend the lifespan of equipment and components, reducing the need for costly replacements or repairs and maximizing the ROI of assets.

**Improved operational efficiency:** Condition monitoring can help to identify inefficiencies in a system or component, such as excessive energy consumption or unnecessary wear and tear. By addressing these issues, operational efficiency can be improved, leading to reduced costs and improved productivity.

**Enhanced safety:** Condition monitoring can help to identify potential safety hazards, such as worn or damaged components, before they cause harm to personnel or equipment. This approach helps to improve overall safety and reduce the risk of accidents and injuries.[8]

#### 1.3.3. Types of Condition Monitoring

Condition monitoring encompasses various techniques and parameters to access the health and performance of equipment. Here are some of the most commonly used types of condition monitoring:

- Vibration Monitoring: Vibration analysis is a widely employed technique for monitoring rotating machinery. By analyzing the vibration patterns, frequencies, and amplitudes, maintenance professionals can detect imbalances, misalignments, bearing defects, and other potential issues.

- Temperature Monitoring: Temperature is a crucial parameter to monitor in any application.

Abnormal temperature variations can indicate problems such as overheating, cooling system failures, or insulations issues.

- Pressure Analysis: Pressure variations can be indicative of issues in systems such as

hydraulic or pneumatic equipment. Continous pressure monitoring helps identify leaks,

blockages, valve malfunctions, or excessive load conditions.[9]

#### 1.4. NanoEdge AI Overview

#### 1.4.1. Definition

NanoEdge AI Studio is a free software provided by ST integrate AI into to any embedded machine learning project running on **any Arm® Cortex®-M MCU**. It acts like a search engine, finding the best AI libraries for given project. This software needs input datasets to figure out the optimal mix of data processing, model structure, and settings.

Once it finds the best setup for the given data, it creates AI libraries. These libraries make it easy to use the data processing and model into existing C based embedded systems. [10]

Figure 1.3: NanoEdge AI Studio

#### 1.4.2. NanoEdge AI Library

NanoEdge AI Libraries are the output of NanoEdge AI Studio. They are a static libraries for embedded C software on Arm® Cortex-M® microcontrollers (MCUs). Packaged as a precompiled. a file, it provides the building blocks to integrate smart features into C code without requiring expertise in mathematics, machine learning, or data science.

When embedded on microcontrollers, the NanoEdge AI Library enables them to automatically "understand" sensor patterns. Each library contains an AI model with implementable types of algorithms for tasks like:

- learning signal patterns: The system can observe normal behavior and build its own internal knowledge without needing pre-labeled data.

- ➤ **detecting anomalies:** It can recognize when incoming signals behave differently from the learned normal patterns, indicating possible faults or unexpected behavior.

- classifying signals: The library can identify which predefined state or condition the machine is currently in, based on live sensor data.

- extrapolating data: It can predict future sensor values or trends based on past and current observations, useful for forecasting behavior or early warnings.[10]

Each kind of project in NanoEdge has its own kind of AI library with their functions but they share the same characteristics:

- **Highly optimized:** Designed for MCUs (any Arm® Cortex®-M).

- **Memory efficient:** Requires only 1-20 Kbytes of RAM/flash memory.

- Fast inference: Executes in 1-20 ms on Cortex®-M4 at 80 MHz.

- **Cloud independent:** Runs directly within the microcontroller.

- **Easy integration:** Can be embedded into existing code/hardware.

- Energy efficient: Minimal power consumption.

- Static allocation: Preserves the stack.

- Data privacy: No data transmission or saving.

- **User-friendly:** No machine learning expertise required for deployment.

All NanoEdge AI Libraries are created using NanoEdge AI Studio.[10]

#### 1.4.3. NanoEdge AI Studio capabilities

NanoEdge AI Studio can:

- Search for optimal AI libraries (preprocessing + model) given user data.

- Simplify the development of machine learning features for embedded developers.

- Minimize the need for extensive machine learning and data science knowledge.

- Utilize minimal input data compared to traditional approaches.

Using project parameters (MCU type, RAM, sensor type) and signal examples, the Studio outputs the most relevant NanoEdge AI Library. This library can be either untrained (learning post embedding) or pretrained. The library performs inference directly on the microcontroller, involving:

- Signal preprocessing algorithms (for example, FFT, PCA, normalization).

- Machine learning models (for example, kNN, SVM, neural networks such as MLP, proprietary algorithms).

- Optimal hyperparameter settings.

The process is iterative: import signals, run a benchmark, test the library, adjust data, and repeat to improve results. [10]

#### 1.4.4. NanoEdge AI Studio limitations

NanoEdge AI Studio:

- Requires user-provided input data (sensor signals) for satisfactory results.

- Libraries' performances are heavily correlated to the quality of the data imported.

- Does not offer ready-to-use C code for final implementation. Users must write, compile, and integrate the code with the AI library.

In summary, NanoEdge AI Studio outputs a static library (.a file) based on user data, which must be linked and compiled with user-written C code for the target microcontroller.[10]

#### 1.5. NanoEdge AI data format and Use Cases

NanoEdge AI Studio and its generated NanoEdge AI Libraries are designed to be sensor-agnostic, offering compatibility with all sensor types including vibration, current, sound, and other measurement modalities. The platform automatically extracts meaningful patterns from input data regardless of the sensing technology.[10]

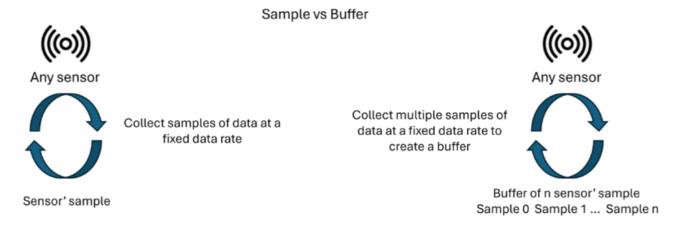

#### 1.5.1. Time series versus cross sectional

**Time series** refers to data that contains information of multiple points in time.

**Cross sectional** refers to data that contains information at a single point in time.

Figure 1.4: NanoEdge AI data format

In an embedded environment, in general, working with time series data is prioritized for analysis. Information about a motor at a single point in time is, most of the time, useless. Most of the useful information is contained in the evolution in time of the data, not in a single observation. in applications like real estate price prediction—where input features (e.g., square footage, room count) are static—temporal evolution is unnecessary.[10]

#### 1.5.2. Defining important concepts

Here are some clarifications regarding the important terms that are used in NanoEdge:

- **Axis/Axes**: In NanoEdge AI Studio, the axis/axes are the total number of variables outputted by the sensor used for a project. For example, a 3-axis accelerometer outputs a 3-variables

- **sample (x,y,z)** corresponding to the instantaneous acceleration measured in the 3 spatial directions. In case of using multiple sensors, the number of axes is the total number of axes of all sensors. For example, if using a 3-axis accelerometer and a 3-axis gyroscope, the number of axes is 6.

- **Signal**: A signal is the continuous representation in time of a physical phenomenon. We are sampling a signal with a sensor to collect samples (discrete values). Example: vibration, current, sound.

- Sample: This refers to the instantaneous output of a sensor, and contains as many

numerical values as the sensor has axes. For example, a 3-axis accelerometer outputs 3

numerical values per sample, while a current sensor (1-axis) outputs only 1 numerical value

per sample.

- Data rate: The data rate is the frequency at which we capture signal values (samples). The

data rate must be chosen according to the phenomenon studied. Also pay attention to

having a consistent data rate and number of samples to have buffers that represent a

meaningful time frame.

- **Buffer**: A buffer is a concatenation of consecutive samples collected by a sensor. A dataset contains multiples buffers. The term **Line** is also used when talking about buffers of a dataset. Buffers are the input for NanoEdge, being in the Studio or in the microcontroller.[10]

#### 1.5.3. Designing a relevant sampling methodology

Compared to traditional machine learning approaches that might need hundreds of thousands of signal examples, NanoEdge AI Studio requires significantly less data—typically around 100-1000 buffers per class, depending on the use case.

However, the data must be **qualified**, containing relevant information about the physical phenomena to be monitored. Designing a proper sampling methodology is crucial to ensure that all desired characteristics of the physical phenomena are accurately captured and translated into meaningful data.

#### **Key considerations:**

- **Study the right physical phenomenon:** Ensure that the data captures the correct physical events.

- **Define the environment:** Match the data collection environment to the real deployment environment.

- Work with buffers, not samples: Buffers provide more context and patterns than individual samples.

- Work with raw data: Use unprocessed data for better accuracy.

- Choose a relevant sampling rate and buffer size: Ensure these settings capture the

necessary details.

- Use a temporal window that makes sense: Select a time frame that covers the relevant events.

- Start small and iterate: Begin with a small dataset and refine as needed. [10]

#### 1.6. STM32 Microcontroller Technology

#### 1.6.1. STM32 Overview

STMicroelectronics is manufacturing the STM32 MCUs which are based on the Arm® Cortex®-M processor. They are 32-bit RISC Arm processor cores, optimized for cost and power sensitive MCUs. **RISC Arm (Reduced Instruction Set Computer)** is an instruction set that allows to divide the commands into several, simple and not complicated instructions that are meant to realize small objectives. The STM32 family offers a large range of devices combining [11]:

- Full integration

- Ease of development thanks to the large ecosystem and professional development tools including free ones

- Very high performance thanks to Arm® Cortex®-M core and ST ART Accelerator™ for some families

- Real-time capabilities

- Digital signal processing

- Low-power and low-voltage operation

Several applications rely on STM32:

- Industrial control systems

- Human interface devices

- Smart metering

- Motor control

- Medical instruments

- Buildings and security (alarms, access control, power meters...)

- Consumer products (PC peripherals, GPS, gaming...)

- Internet of Things

- Connectivity

#### A) Varieties of STM32 MCUs

There are already 16 Cortex-M based microcontroller families (or series).

The STM32 families are split into 4 groups divided as follows:

|                     | Family        | Core                   | Max Frequency     | Flash                   |

|---------------------|---------------|------------------------|-------------------|-------------------------|

|                     | STM32H7₽      | Cortex-M7 - Cortex-M4  | 480 MHz - 240 MHz | 1 to 2 Mbytes           |

| High Performance    | STM32F7₽      | Cortex-M7              | 216 MHz           | 256 Kbytes to 2 Mbytes  |

| rlight Fellothlance | STM32F4₽      | Cortex-M4              | 180 MHz           | 64 Kbytes to 2 Mbytes   |

|                     | STM32F2@ Cort | Cortex-M3              | 120 MHz           | 128 Kbytes to 1 Mbyte   |

|                     | STM32G4₽      | Cortex-M4              | 170 MHz           | 32 to 512 Kbytes        |

|                     | STM32F3₽      | Cortex-M4              | 72 MHz            | 16 to 512 Kbytes        |

| Mainstream          | STM32F1₽      | Cortex-M3              | 72 MHz            | 16 Kbytes to 1 Mbyte    |

|                     | STM32G0₽      | Cortex-M0+             | 64 MHz            | 16 to 512 Kbytes        |

|                     | STM32F0₽      | Cortex-M0              | 48 MHz            | 16 to 256 Kbytes        |

|                     | STM32U5₽      | Cortex-M33             | 160 MHz           | 1024 to 2048 Kbytes     |

|                     | STM32L5@      | Cortex-M33             | 110 MHz           | 256 to 512 Kbytes       |

| Ultra-low-power     | STM32L4+₽     | Cortex-M4              | 120 MHz           | 512 Kbytes to 2 Mbytes  |

| Oili a-low-powei    | STM32L4₽      | Cortex-M4              | 80 MHz            | 64 Kbytes to 1 Mbyte    |

|                     | STM32L1₽      | Cortex-M3              | 32 MHz            | 32 to 512 Kbytes        |

|                     | STM32L0₽      | Cortex-M0+             | 32 MHz            | 8 to 192 Kbytes         |

| Wireless            | STM32WB₽      | Cortex-M4 - Cortex-M0+ | 64 MHz - 32 MHz   | 256 Kbytes to 1 Mbyte   |

| VIII CICSS          | STM32WL₽      | Cortex-M4              | 48 MHz            | 64 Kbytes to 256 Kbytes |

Table 1.1: Comparison of STM32 Microcontroller Families [11]

The STM32 portfolio continues to be extended with more integration and performance and more complex peripherals. All ones with generic or dedicated application field.

The previous table helps to select the family of MCUs suitable depending on application needs, but it's required to review deeply the product characteristics and components to fine-tune the choice.[11]

#### 1.6.2. STM32F103RB

The STM32F103RB from STMicroelectronics belongs to the medium-density performance line of microcontrollers, featuring a 32-bit Arm® Cortex®-M3 RISC core. This microcontroller combines real-time control capabilities with advanced communication interfaces and low power consumption, making it ideal for high-performance embedded applications.

Selection of the STM32F103RB followed comprehensive benchmarking. Its architectural strengths - particularly in real-time processing and energy efficiency - perfectly match the project's core requirements for edge AI implementation.[12]

Figure 1.5: STM 32F 103RB MCU

The STM32F103RB microcontroller was selected for its balanced performance and peripheral integration. Table below summarizes its key specifications and their relevance to this project's edge computing requirements

|                        | Peripheral        | STM32F103RB                                                                                 |

|------------------------|-------------------|---------------------------------------------------------------------------------------------|

| Memory                 | Flash - Kbytes    | 128                                                                                         |

|                        | SRAM - Kbytes     | 20                                                                                          |

| Timers                 | General-purpose   | 3                                                                                           |

|                        | Advanced-control  | 1                                                                                           |

|                        | SPI               | 2                                                                                           |

|                        | I2C               | 2                                                                                           |

| Communication          | USART             | 3                                                                                           |

|                        | USB               | 1                                                                                           |

|                        | CAN               | 1                                                                                           |

| GPIOs                  |                   | 51                                                                                          |

| 12-bit synchronia      | zed ADC Number of | <b>2</b> 16 channels(1)                                                                     |

| channels               |                   |                                                                                             |

| CPU frequency          |                   | 72 MHz                                                                                      |

| Operating voltage      | ge                | 2.0 to 3.6 V                                                                                |

| Operating temperatures |                   | Ambient temperatures: -40 to +85 °C / -40 to +105 °C  Junction temperature: -40 to + 125 °C |

Table 1.2: peripheral of STM32F103 [12]

#### A) Selection Criteria and Merits of STM32F103RB

- Offers a good balance between performance and low power consumption, making it a solid choice for real-time, sensor-based systems — even in tough machine environments.

- Handles real-time state monitoring while helping to extend battery life thanks to its efficient power features.

- Comes with a wide range of communication options (I<sup>2</sup>C, SPI, UART, CAN), which makes it easy to connect with sensors and other components.

- Budget-friendly roughly 22% cheaper than similar ARM-based microcontrollers and well-supported through clear documentation, a large online community, and ST's own development tools like STM32CubeIDE.

#### B) Direct Memory Access (DMA)

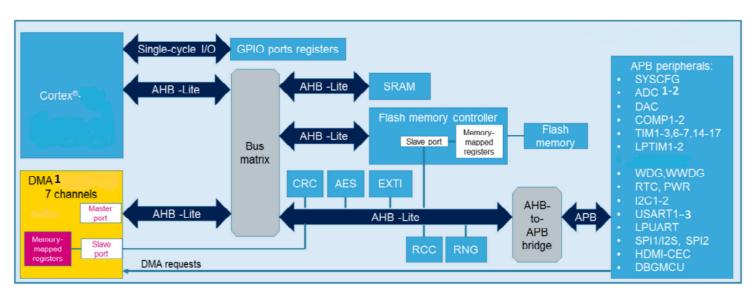

One of the key features of the STM32F103RB microcontroller is the presence of a Direct Memory Access (DMA) controller. The Direct memory access (DMA) embedded in the STM32F103RB microcontrollers is used to provide high-speed data transfers between peripherals and memory and between memory and memory. Data can be quickly moved by the DMA without any CPU action. This keeps CPU resources free for other operations The DMA channels can access any memory-mapped location, including: • AHB peripherals, for instance the CRC generator, • AHB memories, for instance the SRAM, • APB peripherals, for instance the USART peripheral [13]

Figure 1.6: Overview of STM32f103rb Internal Bus System and DMA Integration [13]

# 1.7. Motion Sensors and Vibration Monitoring

#### 1.7.1. Motion sensors

Motion sensors play an important role in a variety of industries and applications.

**Active motion sensors**, such as vibration sensors, tilt sensors, gesture sensors, accelerometers, ultrasonic sensors, microwave sensors and optoelectronic sensors, detect and analyses motion through different mechanisms.

**Passive motion sensors**, such as passive infrared sensors (PIR), detect motion by sensing energy changes.

Motion sensors enable precise motion detection and improve safety, efficiency, and automation in different areas.

The table below (table1.1) [14] will present the comparison between some motion sensors:

| Motion Sensor               | Types   | Working Principle                                                                                            | Applications                                                                  | Detecting Acts        |

|-----------------------------|---------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|

| Vibration sensors           |         | Convert vibration signals into electrical signals.                                                           | Mechanical equipment monitoring,<br>Earthquake monitoring,<br>Motion control. | Vibration or shaking. |

| Tilt Sensors                |         | Convert tilt signals into electrical signals.                                                                | Structural monitoring,<br>Mechanical equipment monitoring,<br>Motion control. | Tilt angle.           |

| Gesture sensors             |         | Convert gesture signals into electrical signals.                                                             | Game control,<br>Smart home,<br>Human-machine interaction.                    | Gesture               |

| Accelerometer               | Active  | Convert acceleration signals into electrical signals.                                                        | Motion control,<br>Smart watches,<br>Safety airbags.                          | Acceleration          |

| Ultrasonic Sensors          |         | Emit ultrasound and receive echoes, calculate the distance of an object based on the echo time.              | Distance measurement,<br>Motion control,<br>Smart home.                       | Distance and Motion   |

| Microwave Sensors           |         | Emit microwaves and receive echoes, calculate the distance and velocity of an object based on the echo time. | Motion control,<br>Smart home,<br>Security monitoring.                        | Distance and Motion   |

| Photoelectric sensors       |         | Emit rays of light and detect the reflection or obstruction of the light.                                    | Motion control,<br>Smart home,<br>Human detection                             | Distance and Motion   |

| Passive Infrared<br>Sensors | Passive | Detect the infrared radiation emitted by an object.                                                          | Security monitoring,<br>Smart home,<br>Human detection                        | Object Motion         |

Table 1.3: Comparison table of motion sensors

#### 1.7.2. Vibration monitoring

When managing and operating an industrial system, condition monitoring is critical. Proper condition monitoring, which maximizes the operative capacity of equipment while minimizing exposure risk, prolongs the life of assets, which, in turn, leads to less equipment downtime, fewer interruptions to operations, improved efficiency, and, ultimately, reduced asset life-cycle costs. For industrial equipment, vibration is one of the major variables for which proactive condition monitoring is essential.[15]

#### A) Root cause analysis

Vibration monitoring and analysis can help with root cause analysis; if there is damage to a piece of equipment, tracking down the root source of vibration can lead to an understanding of the cause of that damage and insight into how to avoid re-occurrence.[15]

#### **B) Predictive Maintenance**

While root cause analysis is an important benefit, vibration monitoring is perhaps most valuable when used in predictive maintenance – as a means of preventing the failure from occurring in the first place. Using a vibration sensor, vibration data can be tracked in real time. Early detection of increased vibration within a piece of equipment allows for maintenance actions to be cost-effectively planned ahead of time, preventing damage from occurring or developing.[15]

#### **C)** Primary Types of Vibration Sensors

There are three primary types of vibration sensors, each with their own advantages and disadvantages:

- Accelerometers: Measure absolute vibration acceleration directly

- Velocity Sensors: Measure absolute vibration velocity directly

- Displacement Sensors (Proximity Probes or Eddy Current Probes) Measure relative vibration in displacement directly (DC static displacement / AC variable displacement)

[15]

#### 1.7.3. Focus on Accelerometers for Vibration Monitoring

Among the different types of motion sensors, accelerometers stand out for their ability to capture even the smallest or fastest changes in movement. They can detect acceleration along one, two, or three axes, which makes them especially useful for monitoring vibration in machines that rotate or move.

In this project, we use a **3-axis accelerometer the MPU6050** to measure how a mechanical system moves and shakes in real time. This allows us to track:

Figure 1.7: MPU6050 Module

- Vibration patterns

- Directional changes in motion

- Sudden impacts or irregularities

Using accelerometers for vibration analysis is a **proven method in predictive maintenance**. It helps spot early signs of issues like imbalance, looseness, or misalignment each of which creates its own vibration "signature" that the system can learn to recognize.[16]

# 1.8. Human-Machine Interfaces in Embedded Systems

A Human Machine Interface (HMI) refers to the point of interaction between humans and machines. It encompasses the hardware and software components that enable users to control, monitor, and communicate with machines, systems, or processes. HMIs facilitate information exchange, providing users with a visual representation of the system's status and enabling them to

input commands or receive feedback. In essence, HMIs act as a bridge, translating complex technical data into a format that is easily understandable and usable by humans.

#### 1.8.1. The functionality of Human-Machine Interfaces (HMIs)

To understand how an HMI works, it is essential to familiarize ourselves with the basic elements of an HMI system:

- D) **Input Devices:** These devices allow users to input commands or information into the system. Examples include buttons, keyboards, touchscreens, voice recognition systems, and motion sensors.

- E) **Output Devices:** These devices present information or feedback to the user. Common output devices include displays, lights, alarms, speakers, and haptic feedback mechanisms.

- F) **Control System:** The control system processes user input and generates corresponding output signals to control the machine or system. It acts as the intermediary between the user and the underlying technology, ensuring the correct execution of commands and providing feedback.

- G) **Software:** HMI software plays a crucial role in creating an intuitive and user-friendly interface. It enables the customization of visual elements, data representation, and interaction capabilities, allowing developers to design interfaces that meet specific user requirements.

As embedded systems continue to evolve, HMIs are increasingly integrated with networked technologies, forming a key component of Internet of Things (IoT) ecosystems.

#### 1.8.2. The Link Between HMI and Internet of Things (IoT)

The Internet of Things (IoT) is revolutionizing the way devices and systems interact and communicate. HMIs play a crucial role in connecting IoT devices to humans, providing interfaces to monitor and control IoT-enabled systems. HMIs enable users to access IoT data, visualize sensor readings, and perform actions remotely. For example, in a smart home setting, an HMI could allow users to adjust temperature settings, control lighting, or manage security systems through a mobile app or voice-activated interface. The integration of HMIs and IoT expands the capabilities of both

technologies, creating a more interconnected and intelligent ecosystem. [16]

#### 1.9. Conclusion

In this first chapter, we explored the key ideas and technologies behind real-time embedded monitoring systems. We saw how edge computing and embedded AI are changing the way devices think and act, pushing intelligence closer to the source of data.

We also introduced the **STM32F103RB microcontroller**, showing how it plays a critical role in running local analysis directly inside the system. A big part of this work involved using **NanoEdge Al Studio**, which made it possible to bring machine learning to a low-power, small-memory device without needing to write complicated Al algorithms ourselves.

Along the way, we discussed why detecting multiple machine states not just anomalies matters when it comes to keeping systems healthy and reliable. We also touched on the importance of sensing motion and giving users simple ways to see what's happening, through local human-machine interfaces.

With all of this groundwork in place, we are now ready to dive into the next chapter, where the actual system design, hardware choices, and software integration will be explained in detai

# Chapter 2

Conceptual Design and Architecture

#### 2.1. Introduction

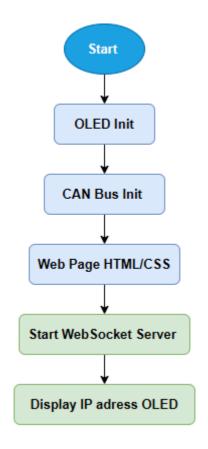

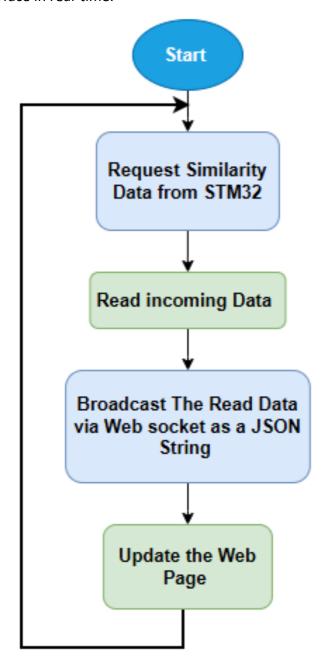

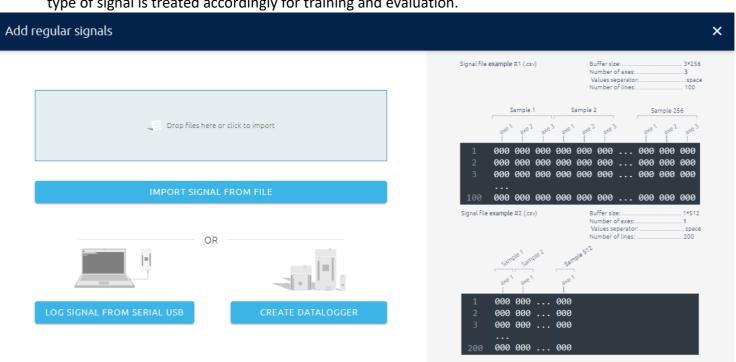

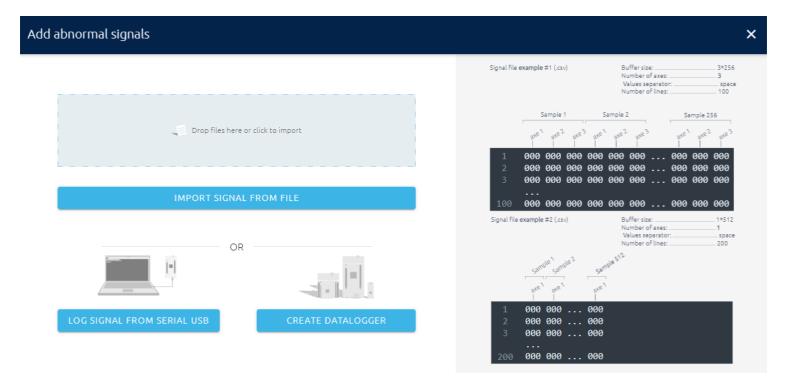

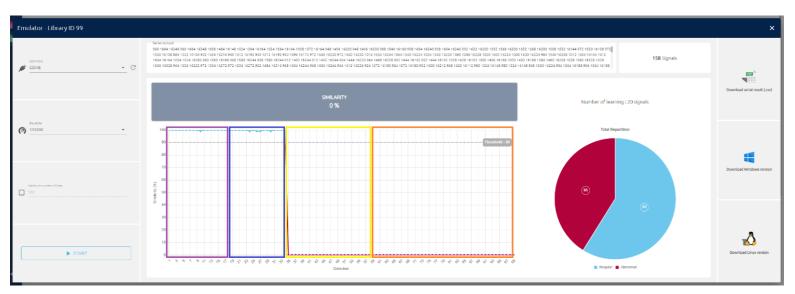

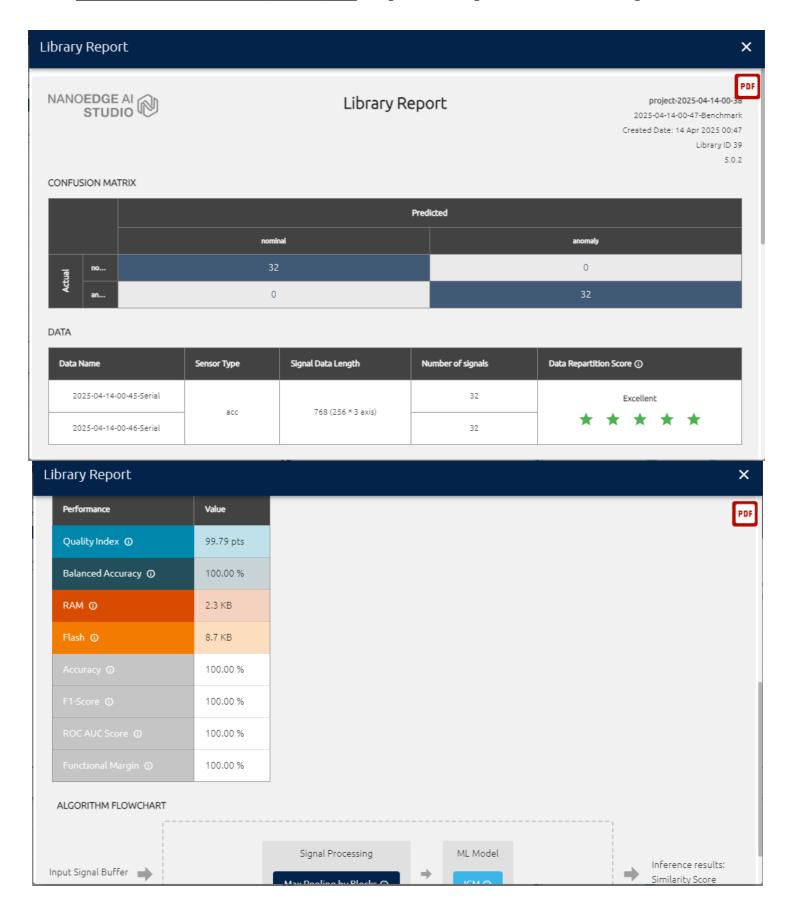

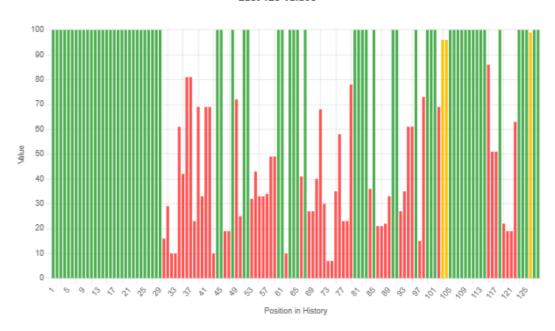

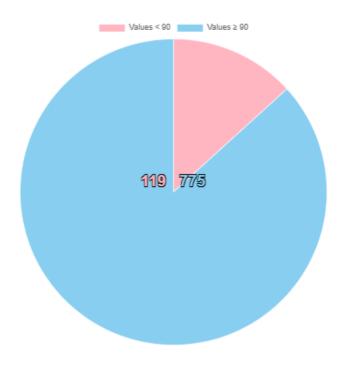

Building a reliable embedded AI system goes far beyond just selecting a microcontroller and writing some code, it requires deliberate architectural planning across both hardware and software layers. In this chapter, we walk through the conceptual and technical design decisions that shaped our system, starting from low-level sensor integration to the overall system structure.