## Ministère de l'enseignement supérieur et de la recherche scientifique

## UNIVERSITE SAAD DAHLEB DE BLIDA I

## Institut d'aéronautique et des études spatiales

Spécialité : Navigation aérienne

**Option: CNS / ATM**

## Thème:

Etude, comparaison et implémentation des détecteurs dédiés à l'acquisition d'un signal GNSS.

En vue d'obtention du diplôme de Master.

Présenté par : Promotrice : Dr. S. Dehouche

Lakel Bilal Nabil Co-Promoteur: Pr. M. Hamadouche

## Abstract

As part of this work, we have acquired a methodology for designing an SDR program and implementing it on an electronic map, in the field of satellite navigation of the constellation GNSS. The approaches used in this research allowed us to identify the different performance parameters of a software design and those of an implementation on an FPGA card, which can be generalized for several applications in communication and aeronautical navigation.

The example of application of the research focused on the analysis of the performance of the detection stage and the techniques of increases in the acquisition of a signal, a very important operation in the GNSS receiver, which determines reliability and availability of a system, key parameters for accuracy, safety and efficiency of a system in aeronautics.

## **RESUME**

Dans le cadre de ce travail, nous avons acquis une méthodologie de conception d'un programme en *SDR* et de son implémentation sur carte électronique, dans le domaine de la navigation par satellites de la constellation *GNSS*. Les démarches utilisées dans cette recherche nous ont permis d'identifier les différents paramètres de performance d'une conception logicielle et ceux d'une implémentation sur carte *FPGA*, pouvant se généraliser pour plusieurs applications en communication et navigation aéronautique.

L'exemple d'application des recherches s'est porté sur l'analyse des performances de l'étage de détection et techniques d'augmentations de l'acquisition d'un signal, une opération très importante dans le récepteur *GNSS*, qui détermine la fiabilité et la disponibilité d'un système, des paramètres clés pour la précision, la sécurité et l'efficacité d'un système en aéronautique.

#### ملخص

كجزء من هذا العمل قد اكتسبنا منهجية لتصميم برمجيات محددة و تنفيذه على خريطة الكترونية , في مجال الملاحة الساتلية في نظام المجموعة العالمية GNSS . سمحت لنا المناهج المستخدمة في هذا البحث بتحديد مختلف الأداء و تطوير البرامج و بارمترات تنفيذ خريطة صفيف البوابة القابلة للبرمجة التي يمكن تعميمها لعدة تطبيقات في مجال الإتصالات و الملاحة الجوية . ركز مثال تطبيق البحث على تحليل آداء مرحلة الكشف و تقنيات الزيادات في اكتساب اشارة , و هي عملية هامة جدا في مستقبل النظم العالمية لسواتل الملاحة التي تحدد الموثوقية و توافر النظام , بارامترات مفتاحية بدقة و سلامة و كفاءة نظام في مجال الطيران.

#### REMERCIEMENTS

Je remercie d'abord ALLAH le bon dieu pour la vie qui m'a offert et qui m'as permis d'accomplir ce travail. Mes remerciements du fond du cœur à mes promoteurs Dr. DEHOUCHE.S et Prof. HAMADOUCHE. M qui m'ont orienté et booster le long de mon travail, un encadrement de qualité et des plus professionnelles, je vous dois beaucoup de respect et gratitude.

J'adresse ma reconnaissance, ma gratitude et mon respect à celui sans lequel cette thèse n'aurait pas eu lieu d'être, au Professeur Monsieur KAMEL BENACHENHOU, grâce à vous et à vos qualités techniques et humaines singulières j'ai pu m'épanouir professionnellement et espérer un avenir meilleur, un grand merci pour votre dévouement et votre soutien.

J'adresse également mes remerciements à mes parents et à ma sœur qui m'ont chéries et ont voulu toujours le meilleur pour moi, et qui ont veillé à ce que je ne manque de rien en dépits de leurs vie entière, vous êtes une bénédiction pour moi.

Je tiens à exprimer ma gratitude envers mes enseignants qui m'ont soutenu et qui m'ont toujours encouragé à aller de l'avant. Une grande estime pour eux qui ont une grande responsabilité.

Merci aux membres de ma famille, particulièrement ma grand-mère Beloui Aicha et mon Oncle Azouz Abderrahim, Un exemple pour moi d'humanité et de sagesse, mes chaleureuses pensées à vous.

Un Immense respect pour toi Ryad Abdelaziz pour l'ami, le frère l'exemple de sagesse et de persévérance que tu es, tu étais l'épaule sur laquelle je me suis accroché par les temps difficiles, et tu étais toujours présent lors des moments de plaisirs. Je termine par remercier mes amis qui ont été présent et qui m'ont soutenu et aider à la construction de ce mémoire Sidahmed Madani, Menira Abdelhamid, Islem Khenifer, Djamila Oubaiche, Sami Khellaoui, , Fares Kaouadji....ainsi qu'à tout mes collègues Damia, Soheib, Meriem....

## TABLE DES MATIERES

| REMERCIEMENTS                                                         |    |

|-----------------------------------------------------------------------|----|

| TABLE DES MATIERES                                                    |    |

| LISTE DES FIGURES                                                     |    |

| LISTE DES TABLEAUX                                                    |    |

| LISTE DES ABREVIATIONS                                                |    |

| LISTE DES SYMBOLES & NOTATIONS                                        |    |

| INTRODUCTION GENERALE                                                 |    |

| Généralités sur la chaine de transmission GNSS dédiée à l'acquisition |    |

| I.1. INTRODUCTION                                                     | 18 |

| I.2. Constellation.                                                   | 19 |

| I.3. Principe de détermination de la position                         | 20 |

| I.4. SIGNAL GPS.                                                      | 23 |

| I.4.1 Le signal au niveau du satellite                                | 24 |

| I.4.4 Propagation du signal dans l'espace                             | 28 |

| I.5. Evolution du signal dans le récepteur                            | 33 |

| I.6 Conclusion                                                        | 43 |

|                                                                       |    |

| CHAPITRE II: L'ETAGE D'ACQUISITION D'UN SIGNAL GNSS                   |    |

| II. 1.INTRODUCTION                                                    | 46 |

| II. 2. Technologie FPGA du Xilinx                                    | 49  |

|----------------------------------------------------------------------|-----|

| II. 2.1. La famille FPGA XilinxVirtex-II.                            | 52  |

| II. 2.2. FPGA Virtex-II Pro                                          | 53  |

| II. 3. Flot de conception FPGA                                       | 56  |

| II. 4. Architecture d'un Circuit FPGA                                | 65  |

| II. 5. Architecture d'un Circuit FPGA                                | 66  |

| CHAPITRE III: Analyse de performance de l'étage de détection         |     |

| III. 1. INTRODUCTION                                                 | 73  |

| III. 2. Acquisition                                                  | 74  |

| III. 3. Analyse de la Corrélation                                    | 75  |

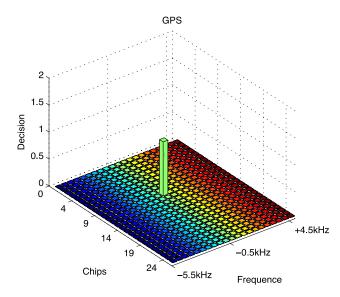

| III. 3.3 Espace de recherche                                         | 79  |

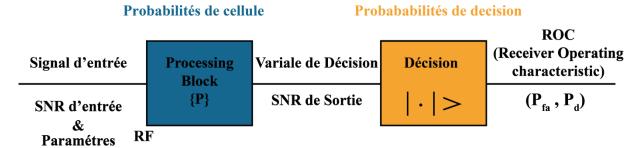

| III. 4. La détection du signal GPS                                   | 81  |

| III. 4.1 Strategies de détection                                     | 82  |

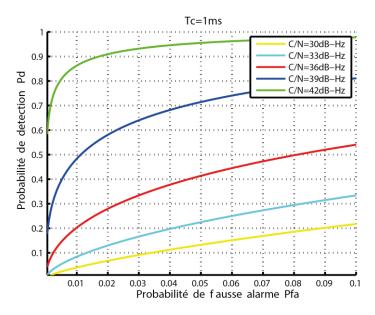

| III. 4.2 Les courbes ROC                                             | 82  |

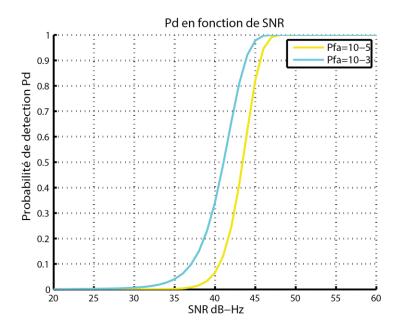

| III. 5. Détecteur et Probabilités                                    | 83  |

| III.6. Intégration                                                   | 90  |

| III.7. CONCLUSION                                                    | 98  |

| CHAPITRE IV: IMPLEMENTATION                                          |     |

| IV. 1. INTRODUCTION                                                  | 102 |

| IV. 2. Outils d'implémentation                                       | 102 |

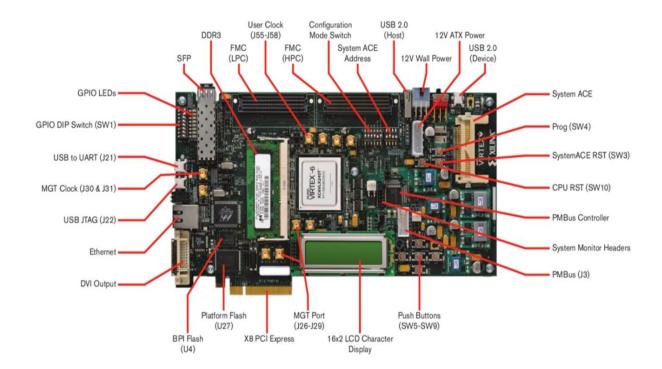

| IV. 3. DESCRIPTION DE LA CARTE Xilinx Virtex 6                       | 105 |

| IV. 4. IMPLEMENTATION SUR FPGA                                       | 107 |

| IV. 4. 1. Implémentation de l'acquisition avec détecteur quadratique | 107 |

| IV. 4. 2. Implémentation de l'acquisition avec intégration           | 103 |

| IV. 5. Comparaison                                                   | 119 |

| IV. 6. CONCLUSION                                                    | 120 |

## **CONCLUSION GENERALE**

## Annexe IV.1

## **Annexe IV.2**

## LISTE DES FIGURES

| Figure I.1:    | Illustration des principaux espaces de modélisations du signal          | 28 |

|----------------|-------------------------------------------------------------------------|----|

| Figure I.2 :   | Dispositions de satellites et la relation avec la précision de mesure   | 22 |

| Figure I.3:    | répartition des fréquences pour le système GNSS                         | 24 |

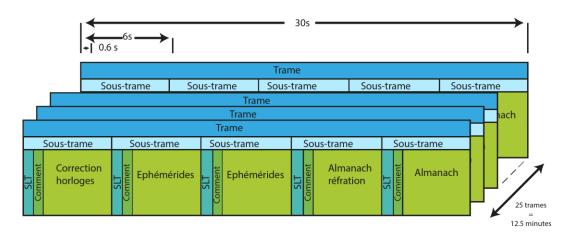

| Figure I.4:    | Message de navigation d'un signal GPS                                   | 25 |

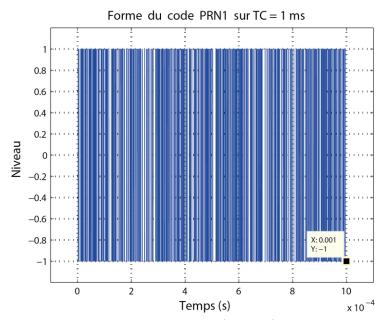

| Figure I.5:    | Forme d'un code PRN                                                     | 26 |

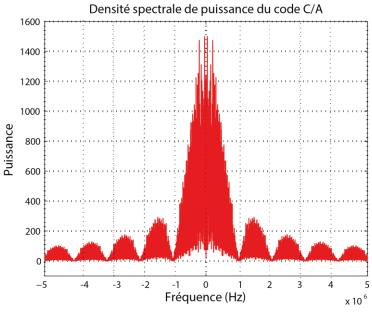

| Figure I.6:    | Spectre de fréquence du code PRN                                        | 26 |

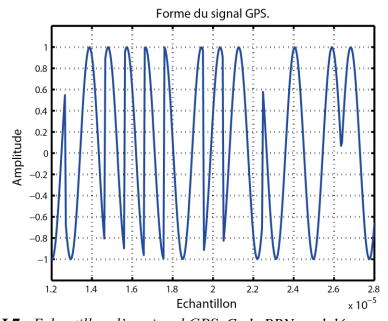

| Figure I.7 :   | Echantillon d'un signal GPS. Code PRN modulé par une porteuse.          | 27 |

| Figure I.8:    | Gain de l'antenne d'émission                                            | 29 |

| Figure I.9:    | Vitesse du satellite et effet doppler                                   | 31 |

| Figure I.10:   | Fréquence Doppler causée par le mouvement du satellite                  | 32 |

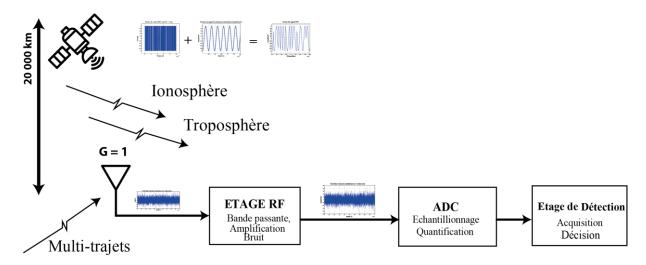

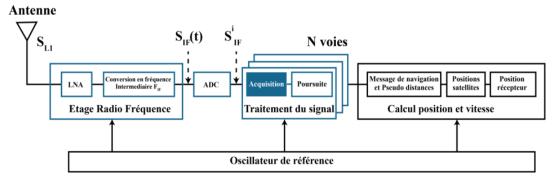

| Figure I.12:   | Composantes d'un récepteur GNSS et leurs rôles dans la chaine           | 33 |

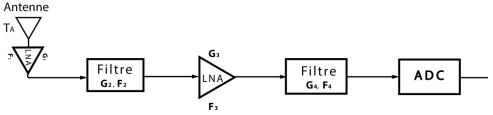

| Figure I.13:   | Architecture généralisée d'un étage radio fréquence d'un récepteur GNSS | 35 |

| Figure I.14:   | Rôle du mélangeur et du filtre passe bas                                | 35 |

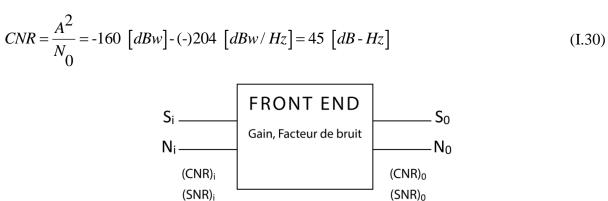

| Figure I.15.a: | Figure de bruit du « FRONT END »                                        | 41 |

| Figure I.15.b: | Figure de bruit du « FRONT END » avec une digitalisation direct         | 41 |

| Figure I.16:    | Paramètres du « Front end »                                   | 42 |

|-----------------|---------------------------------------------------------------|----|

| Figure II.1:    | Comparaison des temps de routage entre circuits configurables | 47 |

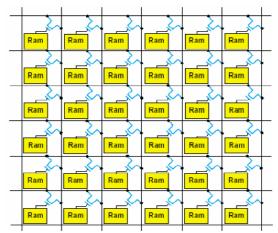

| Figure II.2 :   | Réseau d'aiguillage typique d'un FPGA                         | 48 |

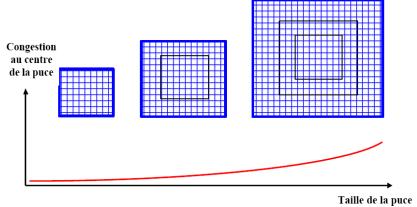

| Figure II.3:    | Zones de congestion dans le routage des FPGA                  | 49 |

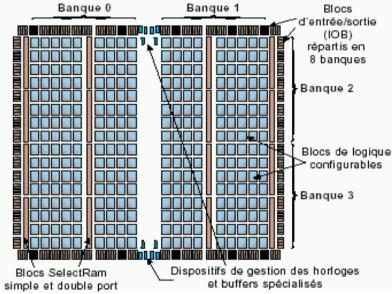

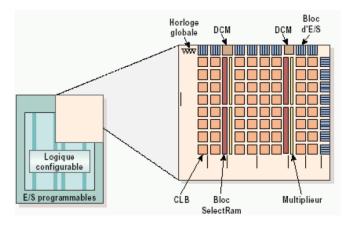

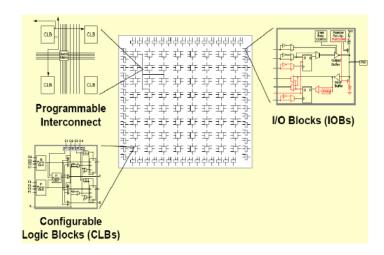

| Figure II.4:    | Organisation des FPGA de Xilinx                               | 50 |

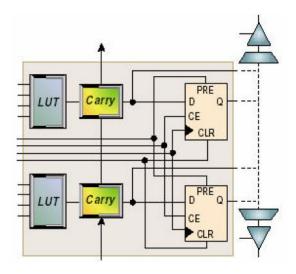

| Figure II.5:    | Architecture simplifiée d'un « Slice ».                       | 51 |

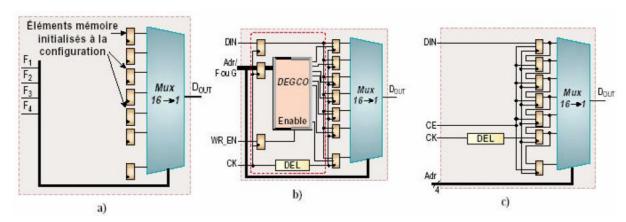

| Figure II.6:    | Les modes de configuration des LUT                            | 51 |

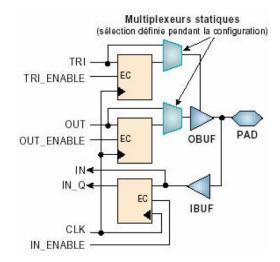

| Figure II.7:    | Configuration des blocs d'E/S                                 | 52 |

| Figure II.8:    | Détail de l'architecture d'un composant Virtex-II             | 53 |

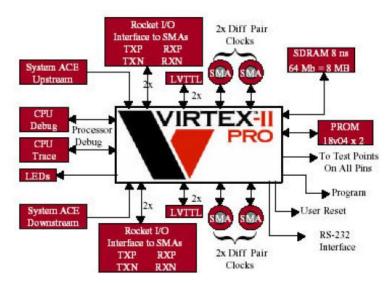

| Figure II.9:    | Vue Globale du VIRTEX-II PRO                                  | 54 |

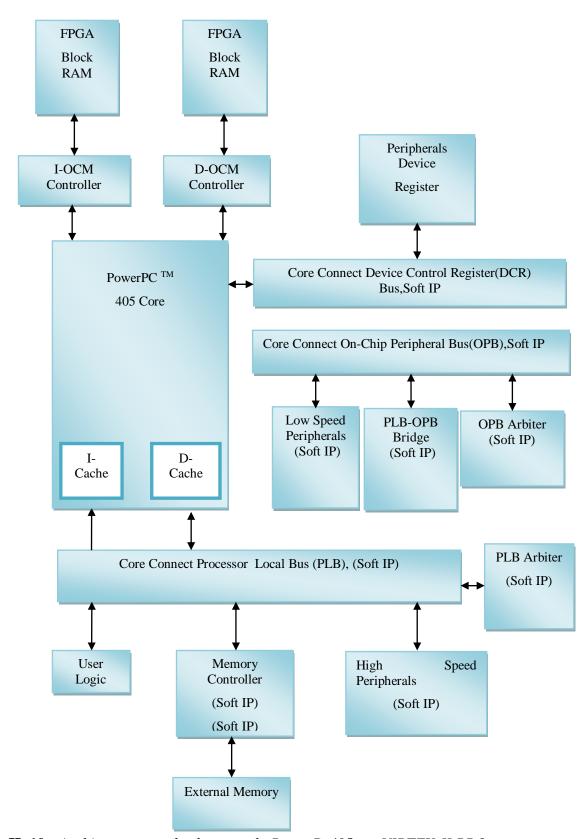

| Figure II. 10 : | Architecture standard autour du PowerPc405 sur VIRTEX-II PRO  | 55 |

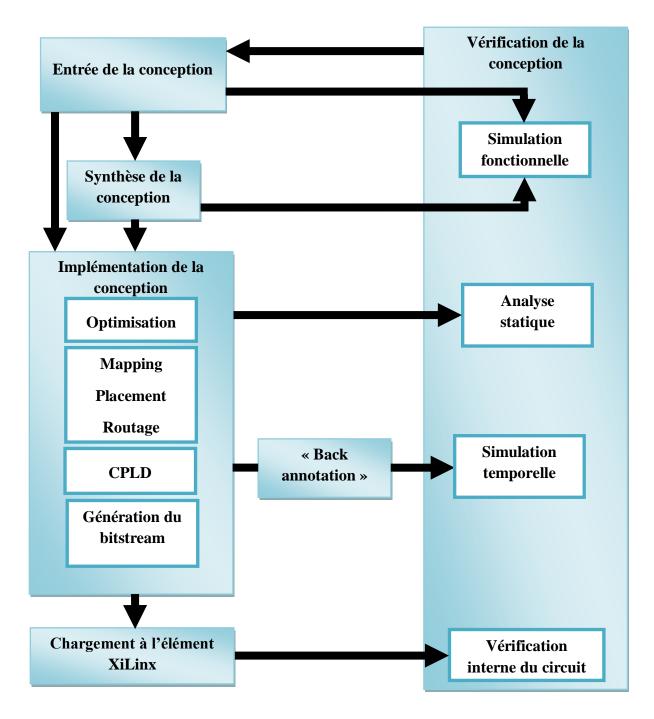

| Figure II.11:   | Flot de conception générique                                  | 57 |

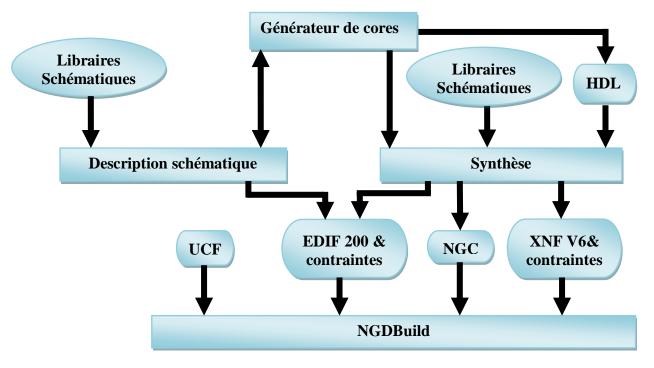

| Figure II.12:   | Flot de synthèse sous Xilinx                                  | 59 |

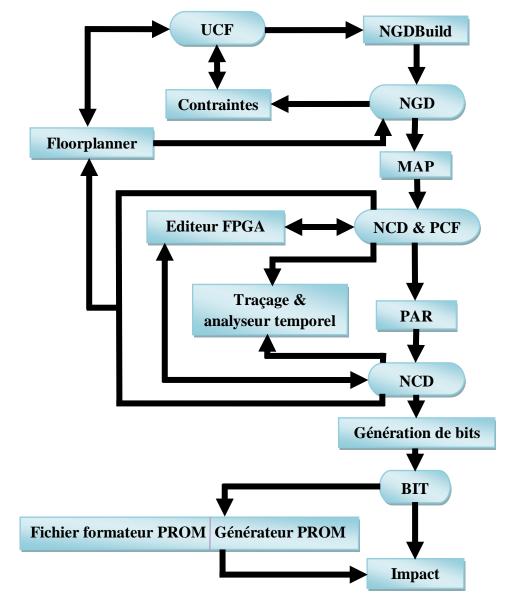

| Figure II.13:   | Implémentation sous Xilinx                                    | 60 |

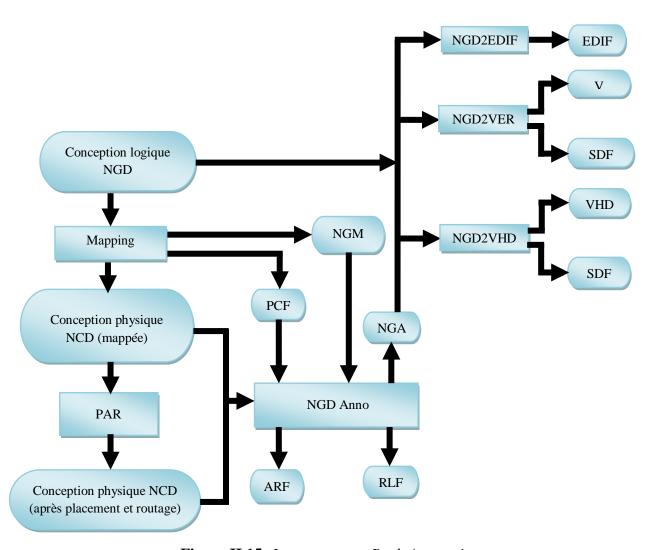

| Figure II.14:   | Le processus de vérification sous Xilinx.                     | 62 |

| Figure II.15:   | Le processus « Back-Annotation ».                             | 63 |

| Figure II.16 :  | Architecture interne du FPGA                                  | 66 |

|                 |                                                               |    |

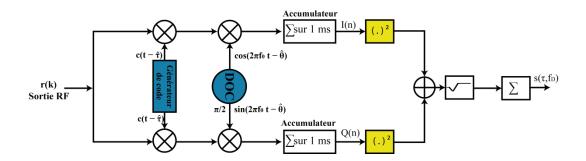

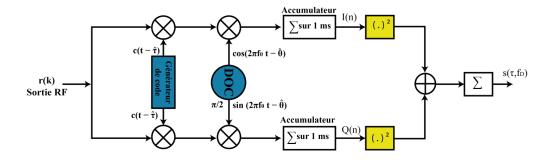

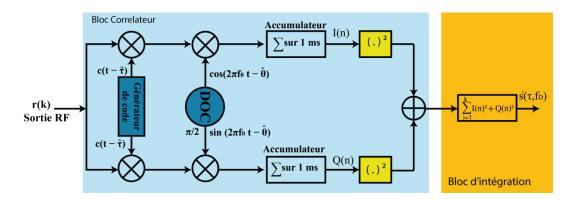

| Figure III.1 :  | Schéma bloque de l'étage de détection                         | 73 |

| Figure III.2:   | Schéma simplifié du bloque d'acquisition                      | 74 |

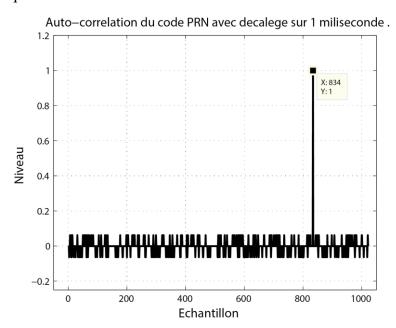

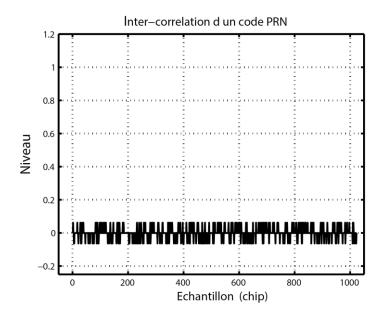

| Figure III.3:   | Auto corrélation de deux codes PRN similaires décalés         | 75 |

| Figure III.4:   | Inter corrélation de deux codes PRN différents                                                                         | 76  |

|-----------------|------------------------------------------------------------------------------------------------------------------------|-----|

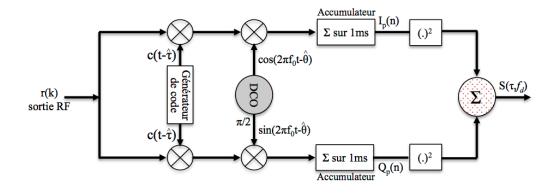

| Figure III.5:   | corrélateur.                                                                                                           | 76  |

| Figure III.6:   | Résultat obtenu en acquisition GPS                                                                                     | 80  |

| Figure III.7:   | Schéma bloc d'un détecteur linéaire                                                                                    | 83  |

| Figure III.9 :  | ROC pour détecteur linéaire et quadratique (probabilité de détection en fonction de Pfa pour plusieurs SNR)            | 88  |

| Figure III.10 : | Probabilité de détection en fonction de SNR pour plusieurs Pfa                                                         | 89  |

| Figure III.11 : | Schéma d'un récepteur avec une intégration non cohérente                                                               | 93  |

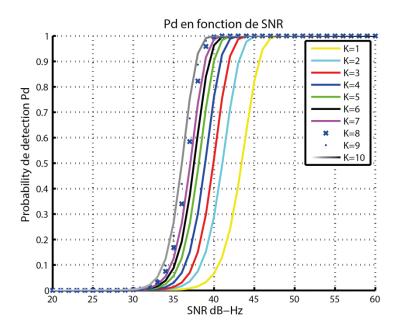

| Figure III.12 : | Probabilité de détection en fonction de SNR pour Pfa=10 <sup>-5</sup> pour un détecteur avec intégration non cohérente | 94  |

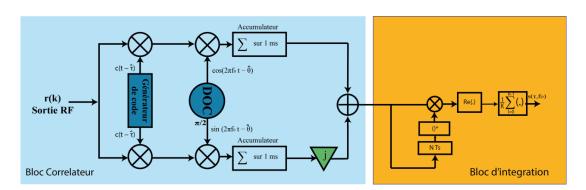

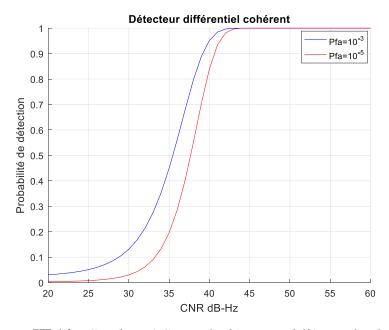

| Figure III.14:  | Détecteur différentiel cohérent                                                                                        | 95  |

| Figure III.15:  | Courbe ROC pour le détecteur différentiel cohérent.                                                                    | 97  |

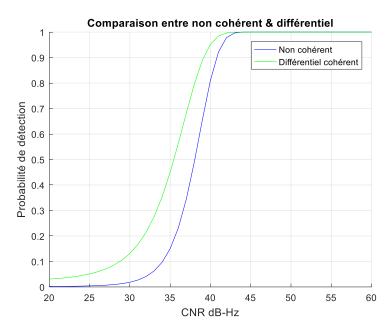

| Figure III.16 : | Comparaison entre le détecteur non cohérent et le détecteur différentiel.                                              | 98  |

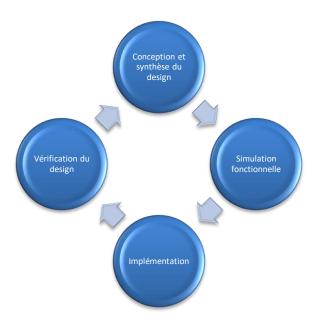

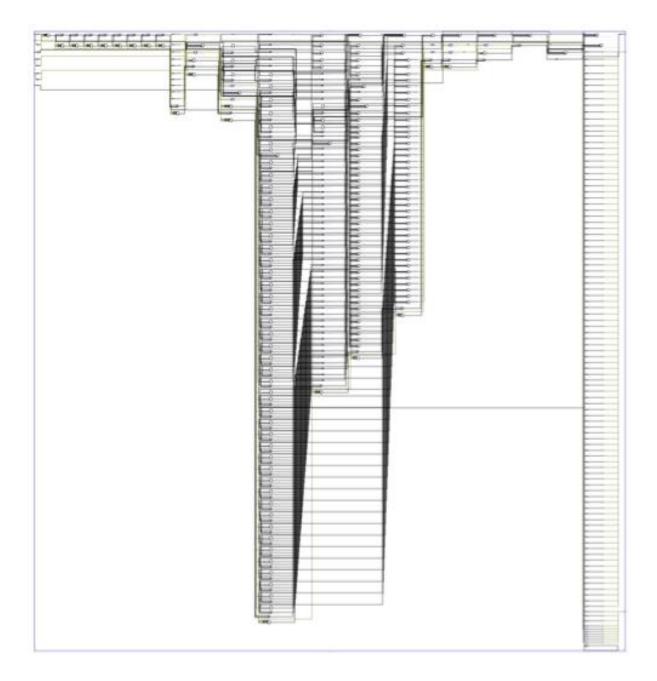

| Figure IV.1:    | Flot de conception                                                                                                     | 103 |

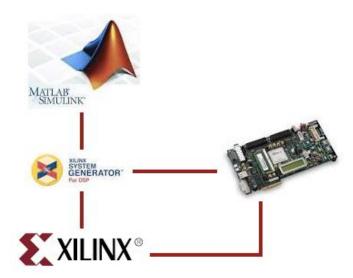

| Figure IV.2:    | Co-design Co-design                                                                                                    | 103 |

| Figure IV.3:    | FPGA Virtex-VI ML605                                                                                                   | 106 |

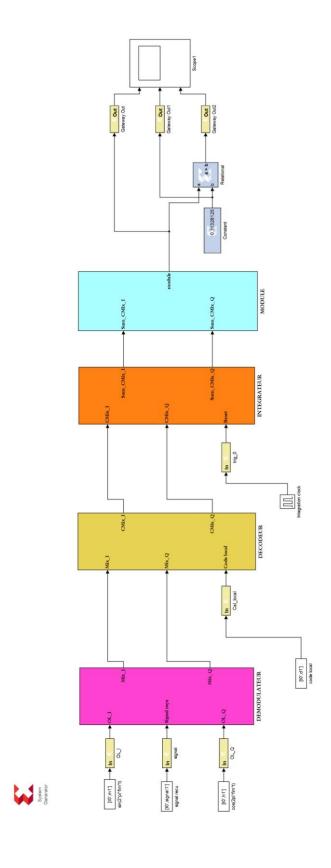

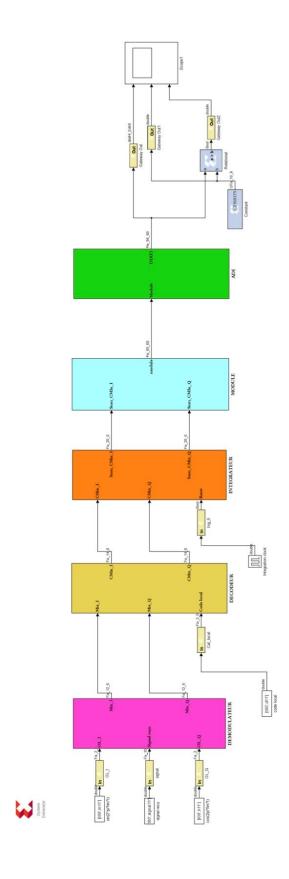

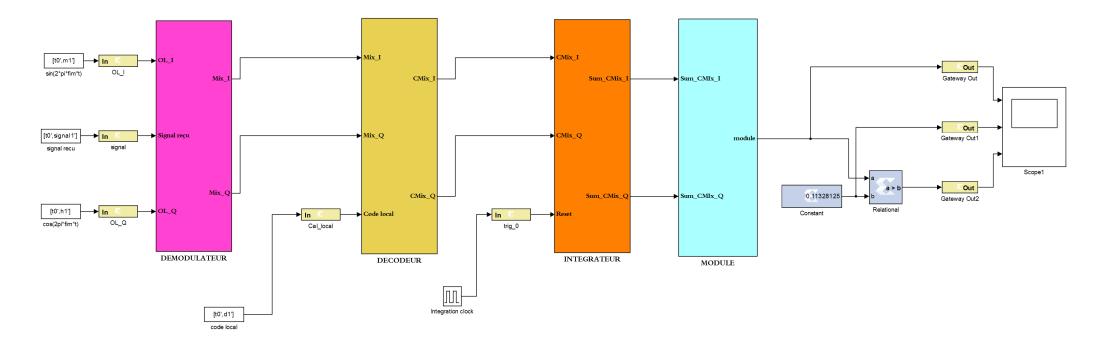

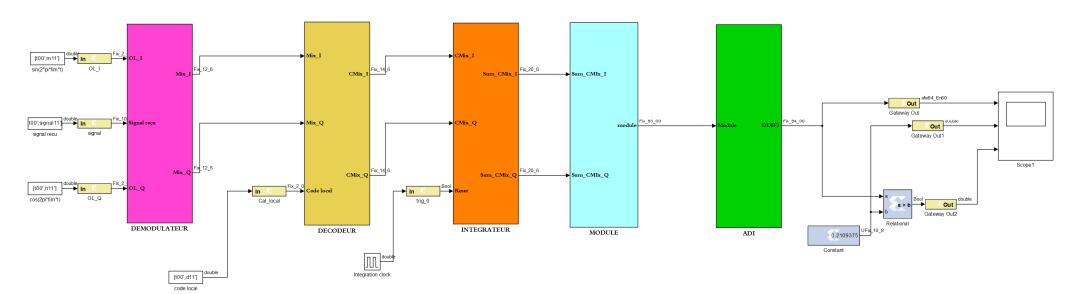

| Figure IV.4:    | Schéma modulaire du détecteur quadratique                                                                              | 109 |

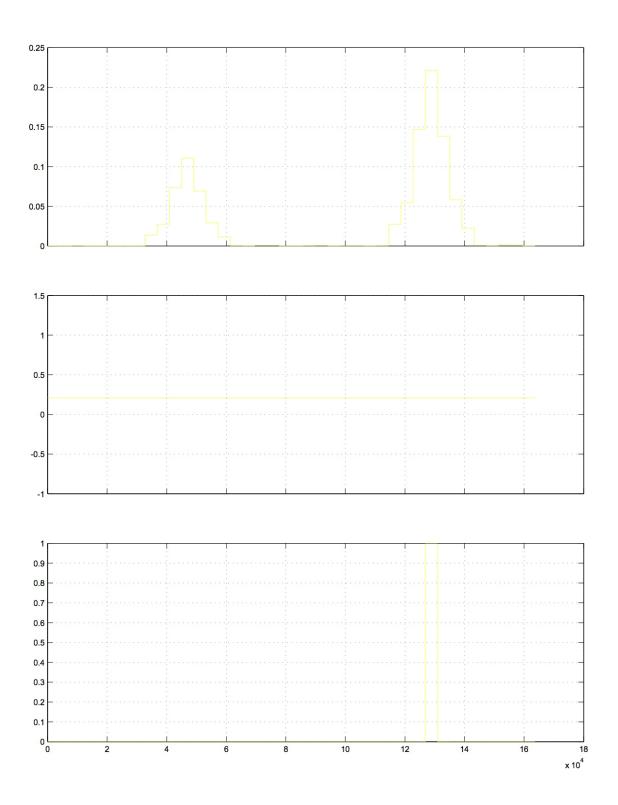

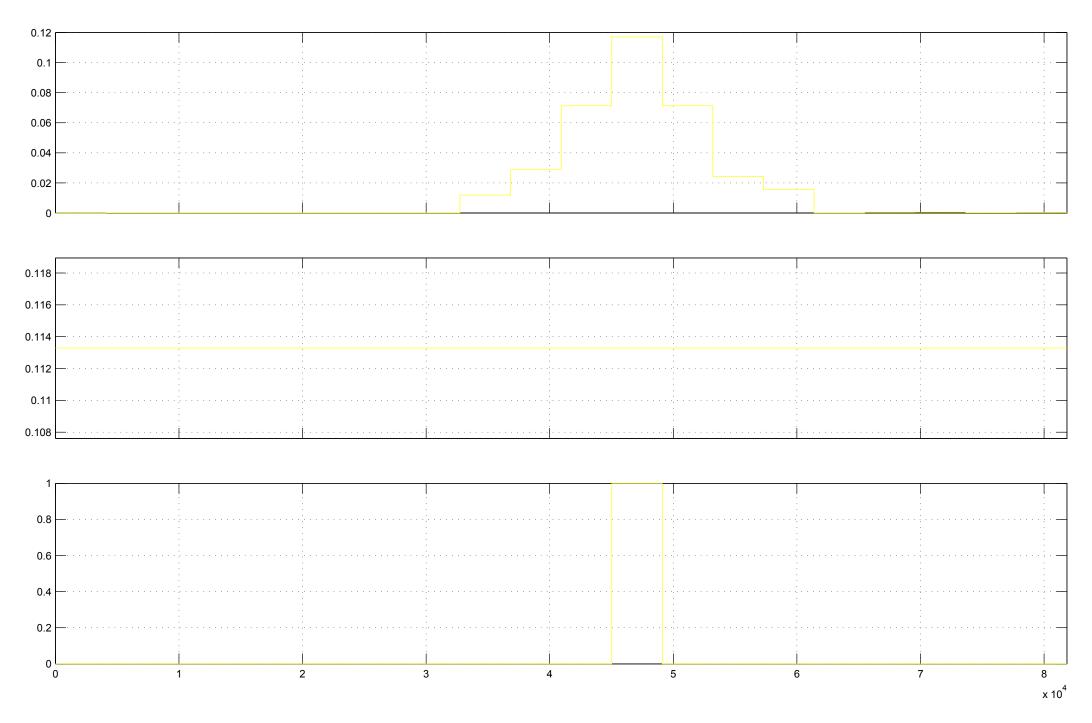

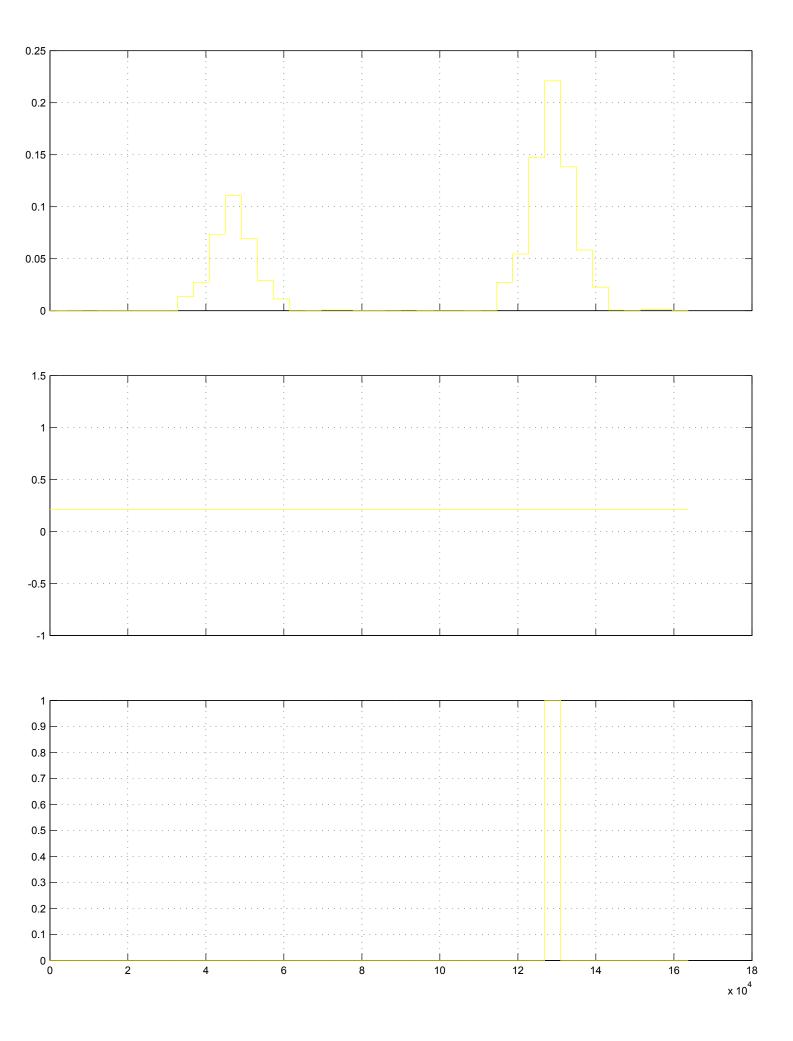

| Figure IV.5:    | Résultat de la simulation du détecteur quadratique                                                                     | 110 |

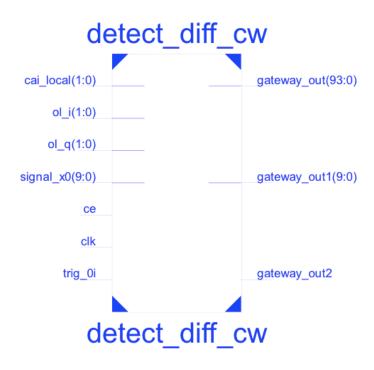

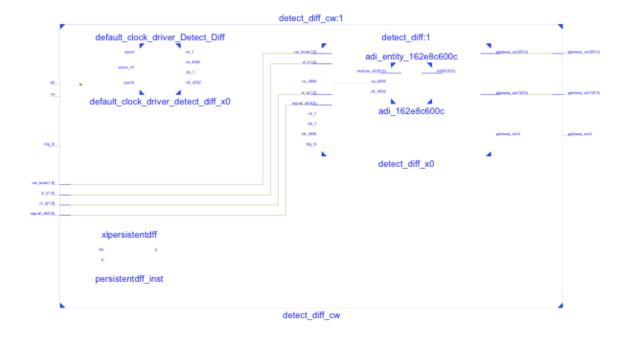

| Figure IV.6:    | Bloc RTL Schematic principal                                                                                           | 110 |

| Figure IV.7:    | Description "RTL Shematic"                                                                                             | 111 |

| Figure IV.8 :   | « Technologie Shematic » détecteur quadraique                                                                          | 112 |

| Figure IV.9 :   | détecteur série non cohérent                                                                                           | 115 |

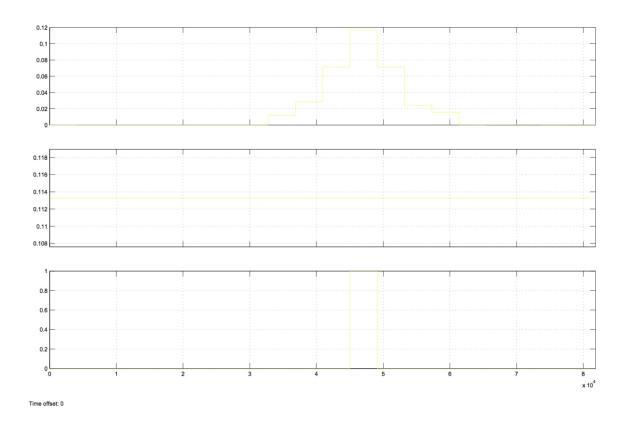

| Figure IV.10: | Résultat de la simulation du détecteur série non cohérent                        | 116 |

|---------------|----------------------------------------------------------------------------------|-----|

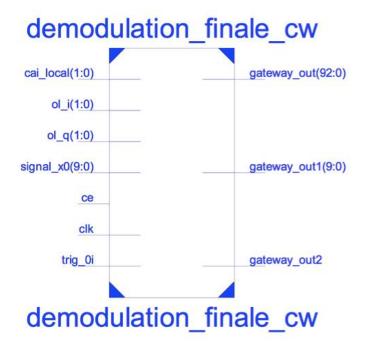

| Figure IV.11: | Bloc "RTL Shemati"c principal                                                    | 117 |

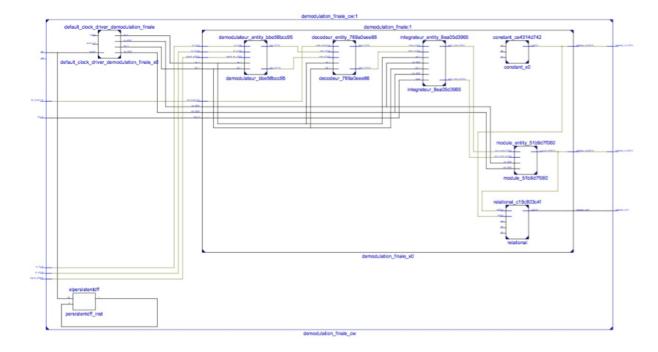

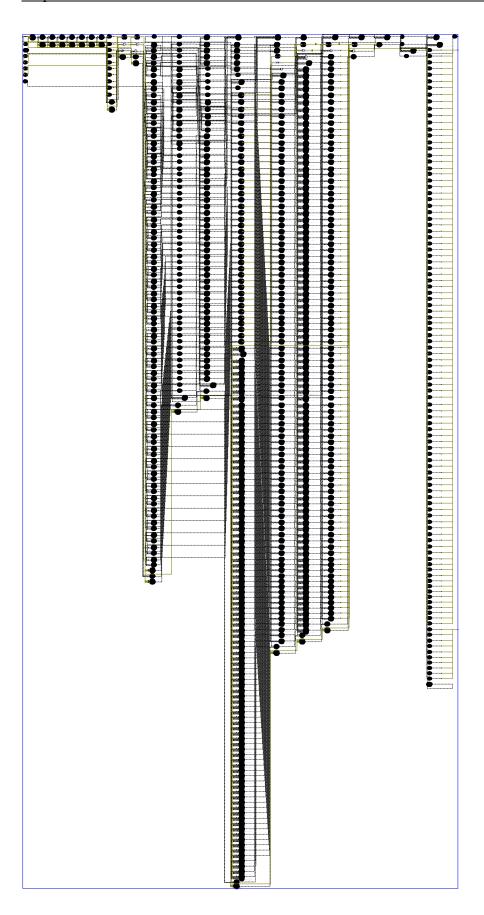

| Figure IV.12: | Description « RTL Shematic » du detecteur avec integration                       | 117 |

| Figure IV.13: | « Thecnologie shematic » du detecteur avec integration                           | 118 |

|               |                                                                                  |     |

|               | LISTE DES TABLEAUX                                                               |     |

| Tableau I.1:  | Paramètres de la constellation GPS.                                              | 19  |

| Tableau I.2:  | Bilan de liaison émission réception.                                             | 38  |

| Tableau I.3:  | Bilan de liaison entrée sortie de l'étage RF et SNR à l'entrée de l'acquisition. | 42  |

| Tableau II.1: | Famille FPGA Virtex-II                                                           | 52  |

| Tableau II.2: | Ressources du circuit VIRTEX-II PRO/ VIRTEX-II PRO X                             | 56  |

| Tableau IV.1: | Ressources utilisées pour détecteur quadratique.                                 | 108 |

| Tableau IV.2: | Ressources utilisées pour détecteur avec intégration                             | 114 |

|               |                                                                                  |     |

|               | LISTE DES SYMBOLES ET NOTATIONS                                                  |     |

| AWGN    | Bruit blanc gaussien additive             |  |

|---------|-------------------------------------------|--|

| BPSK    | Binary Phase Shifl Keying                 |  |

| $C/N_0$ | Rapport signal sur bruit                  |  |

| C/A     | Coarse Acquisition Code                   |  |

| CDMA    | Code Division Multiple Access             |  |

| DSP     | Digital Signal Processor                  |  |

| FPGA    | Field Programmable Gate Array             |  |

| UIT     | Union international des telecommunication |  |

| LNA     | Amplificateur faible bruit                |  |

| SDN     | Software Defined Navigator                |  |

| SDR     | Software Defined Radio                    |  |

| $A_{i}$                    | Amplitude du signal GNSS                                                                       |

|----------------------------|------------------------------------------------------------------------------------------------|

| $A_G$                      | Gain de l'amplificateur AGC                                                                    |

| $az_k$                     | Azimut du satellite k                                                                          |

| $\mathbf{B}_{\mathit{IF}}$ | Bande passante de l'étage radio fréquence                                                      |

| $\Delta b_r$               | Biais d'horloge du récepteur                                                                   |

| $\Delta b_{si}$            | Biais d'horloge du satellite i                                                                 |

| C                          | Vitesse de la lumière                                                                          |

| $d_{euc}$                  | Distance euclidienne entre le satellite i et le récepteur                                      |

| $d_i(t)$                   | Données de navigation                                                                          |

| $el_k$                     | Elévation du satellite k                                                                       |

| $f_e$                      | Fréquence d'échantillonnage                                                                    |

| $f_{d\mathrm{min}}$        | Fréquence Doppler minimale dans l'espace de recherche                                          |

| $f_{d\mathrm{max}}$        | Fréquence Doppler maximale dans l'espace de recherche                                          |

| $\Delta f$                 | Résolution fréquentielle dans l'espace de recherche                                            |

| $\Delta f_f$               | Décalage Doppler sur la fréquence de la porteuse                                               |

| $\delta f_d$               | Erreurs résiduelles entre le centre de la cellule et la vraie position de la fréquence Doppler |

| $\Delta f_f$               | Décalage Doppler sur la fréquence de la porteuse                                               |

| $f_{\scriptscriptstyle E}$ | Fréquence du signal émis par le satellite                                                      |

| $f_c$                      | Fréquence du code d'étalement                                                                  |

| $f_{\scriptscriptstyle L}$ | Fréquence de la porteuse du signal GNSS                                                        |

| $f_{\it IF}$               | Fréquence intermédiaire d'un récepteur GNSS                                                    |

| $f_{c,d}$                  | Fréquence du code d'étalement affecté par le Doppler                                           |

| $f_d$                      | Décalage Doppler                                                                               |

| $\hat{f}_d$                | Décalage Doppler estimé                                                                        |

| $f_0(s)$                   | Densité de probabilité de la variable s sous $H_0$                                             |

| $f_1(s)$                   | Densité de probabilité de la variable s sous $H_1$                                             |

| $G_{t}$                    | Gain de transmission                                                                           |

| $G_r$                                | Gain de réception                                               |

|--------------------------------------|-----------------------------------------------------------------|

| $H_1$                                | Hypothèse alternative                                           |

| $H_0$                                | Hypothèse nulle                                                 |

| N                                    | Longueur de la période d'intégration                            |

| $N_{	au}$                            | Nombre de cellules dans la direction du temps dans l'espace de  |

| <b>3.</b> 7                          | recherche  Desition du hit de transition                        |

| $N_r$                                | Position du bit de transition                                   |

| $N_f$                                | Nombre de cellules fréquentielles dans l'espace de recherche    |

| $N^{}_0$                             | Densité spectrale de puissance du bruit                         |

| $P_r$                                | Puissance reçue                                                 |

| $P_{t}$                              | Puissance transmise                                             |

| $P_d$                                | Probabilité de détection                                        |

| $P_{\mathit{fa}}$                    | Probabilité de fausses alarmes                                  |

| $R_c\Big(\hat{	au},\hat{f}_d\Big)$   | Fonction d'ambiguïté                                            |

| $R_n(\hat{\tau}, \hat{f}_d)$         | Fonction de corrélation en présence du bruit seul               |

| r[n]                                 | Signal échantillonné                                            |

| $r_q[n]$                             | Signal quantifié                                                |

| $r_{RF}$                             | Signal reçu au niveau de l'antenne du récepteur                 |

| $S\!\left(\hat{	au},\hat{f}_d ight)$ | Variable de décision                                            |

| $S_L(\hat{	au},\hat{f}_d)$           | Variable de décision en considérant l'intégration non cohérente |

| $T_c$                                | Temps d'intégration                                             |

| T                                    | Longueur du code d'étalement                                    |

| $T_s$                                | Période d'échantillonnage                                       |

| $T_{ch}$                             | Durée d'un chip du code d'étalement                             |

| $t_r$                                | Temps de réception du signal au niveau du récepteur             |

| $t_{si}$                             | Temps d'émission au niveau du satellite i                       |

| $V_r$                                | Composante radiale de la vitesse du satellite                   |

$Y_I(\hat{\tau}, \hat{f}_d)$  Partie réelle de la variable de décision

$Y_{Q}(\hat{\tau},\hat{f}_{d})$  Partie imaginaire de la variable de décision

α Rapport d'amplitude multitrajet / signal direct

$\beta$  Seuil de détection fixe

$\eta_{\it RF}$  Bruit Gaussien à l'étage radio fréquence

$\eta_{\it IF}$  Le bruit à la sortie de l'étage  $\it IF$

$\rho_i$  Pseudo-distance entre le récepteur et le satellite i

$\rho_{MS,k}$  Pseudo-distance séparant le récepteur du satellite k

$\sigma_n^2$  Variance du bruit reçu après corrélateur

*τ* Retard de propagation

$\hat{\tau}$  Retard de propagation estimé

$\delta \tau$  Erreurs résiduelles entre le centre de la cellule et la vraie position du

code phase

$\varphi_i$  Phase du signal reçu

$\hat{\boldsymbol{\varphi}}_{i}$  Phase du signal estimé

## INTRODUCTION GENERALE

En 1983 le conseil de l'OACI a affirmé que les systèmes et procédures supportés par l'aviation civile ont atteint leurs limites de performances et poseront problème sur la capacité de l'espace aérien international. Ce premier a créé le comité FANS pour des systèmes de navigations futurs. Le comité FANS proposa à son tour le concept CNS/ATM à la 10ème conférence de la navigation aérienne en 1991. Prévu pour déploiement en 2020, le concept CNS/ATM vise à utiliser plusieurs technologies de communications, de navigation et surveillance dans un système interopérable gérant le trafic aérien en toute transparence, pour un moindre coût et sans compromettre les niveaux de sécurité établis au préalable[15].

La mission du déploiement sera d'améliorer la sécurité, la régularité et l'efficacité des vols, augmenter la capacité et l'efficacité des espaces aériens en plus de minimiser les équipements. Cela est réalisable en maîtrisant les transferts d'informations, la précision de la navigation et l'étendue de la surveillance. D'autres bénéfices adviendront de ceux cités. Les systèmes de trafic aérien basés sur le CNS/ATM dépendent étroitement des satellites ! [15]

Le Radiorepérage par satellites consiste à déterminer la position, la vitesse ou d'autres caractéristiques d'un objet, ou obtention de données relatives à ces paramètres, et cela à l'aide des propriétés de propagation des ondes radioélectriques. Le système *GNSS* est un système à *Diffusion* qui transmet des renseignements concernant la navigation aérienne. Les satellites *GNSS* émettent en continu des signaux que le récepteur exploite pour extraire leur temps de parcours ainsi qu'un certain nombre d'informations utiles. Afin de répondre aux nouvelles exigences des récepteurs *GNSS* en termes d'interopérabilité, l'implémentation logicielle s'exécutant sur ordinateur ou sur carte électronique est la nouvelle tendance des recherches.

L'Acquisition dans les systèmes *GNSS*, étant la 1ère étape dans le traitement logiciel, et qui consiste à déterminer la présence des signaux des satellites visibles aux récepteurs et de donner une rugueuse estimation des paramètres du signal (décalage temporel et fréquentiel) requises pour l'estimation de la position. Afin de déterminer les paramètres de performance de l'acquisition et les limites des techniques utilisées, il faudra modéliser le signal le long de ses transitions dans le récepteur pour ensuite établir un programme de détection fiable, en temps pratique selon les besoins de notre application de navigation aéronautique.

## But et approche pédagogique du projet

Le but de ce travail de PFE est l'évaluation de performance des différentes techniques d'acquisition, plus précisément la partie détection, afin de tirer des conclusions sur les avantages et les inconvénients associés à chaque méthode. Par la suite, on réalise ces détecteurs afin de d'établir un bilan lié à leur implémentation.

L'application d'un tel projet a nécessité, d'abord une orientation de l'étude par apport aux besoins de l'aviation civile et aux performances requises RNP du projet CNS/ATM de l'OACI ainsi qu'aux besoins futurs de la radionavigation, et cela en termes d'interopérabilité car de nos jours des milliers de satellites sont en orbite autour de la Terre. Parmi eux, nous pouvons citer les satellites des constellations **GPS** Américain, **GLONASS** Russe, **Galileo** Européen, **Beidou** Chinois. Avec plusieurs signaux différents l'implémentation devient un défi vu la complexité des fonctions à exécuter. Sous contraintes temporelles, une réalisation d'un tel système demande un travail laborieux et très méthodique.

#### Deux approches logiques seront utilisées :

La première serait de présenter les composantes du récepteur *GNSS* et les paramètres recherchés pour l'acquisition du signal, et cela de façon générale, permettant ainsi de bien définir le but du travail et schématiser la chaine de transmission ainsi que déterminer l'emprise de chaque espace de modélisation sur le signal.

✓ La deuxième approche consiste en l'étude des traitements et opérations élémentaires sur le signal séparément dans chaque bloc. Cela nous aidera à mettre en évidence les opérations liées directement ou indirectement aux performances du système d'acquisition et de choisir ensuite la meilleure adaptation selon les performances requises pour notre application. Ainsi, le signal va être poursuivi de sa génération puis sa propagation et enfin dans les phases du traitement par le récepteur.

Dans ce sens la structure de ce travail s'est faite sous quatre chapitres :

❖ Dans le premier chapitre nous étudierons la chaine de transmission des signaux GPS en nous intéressant au signal et ses paramètres jusqu'au bloc d'acquisition.

- ❖ Le deuxième chapitre est une introduction aux FPGA's et leur caractéristiques. La connaissance des performances des cartes électroniques ainsi que les méthodes de conception est primordiale pour leur exploitation à juste valeur.

- ❖ Dans le troisième chapitre nous entamerons l'analyse des performances de l'acquisition en définissant le choix de la stratégie à entreprendre pour la simulation de notre récepteur en mettant en évidence les contraintes auxquelles on peut s'attendre avant l'implémentation.

- ❖ Le quatrième chapitre est dédié à la l'implémentation sous logiciels de notre acquisiteur, ou nous analyserons les difficultés d'une conception en apportant les conclusions nécessaires pour notre maitrise.

## Chapitre I

# Généralités sur la chaine de transmission GNSS dédiée à l'acquisition

- **!** Introduction

- **Constellation**

- **❖** Principe de détermination de la position

- **❖** Modélisation du signal

- **\*** Conclusion

#### I.1. INTRODUCTION

Le concept traitement radio software est réalisé à l'aide d'un convertisseur analogique numérique. Une fois l'obtention d'un signal numérique, les données sont traitées pour recueillir les informations recherchées [3]. L'avantage primordial du traitement soft est de minimiser les composants hardwares ou un récepteur de plusieurs signaux, issus de systèmes différents, encombrent un système hard. D'autres avantages peuvent être cités : comme pouvoir simuler la chaine de transmission sur logiciel afin d'analyser les performances du système et exercer plusieurs tests et visualiser les schémas d'implémentation pour améliorer le système avant conception, mais aussi enregistrer des séquences de signaux reçus.

Les généralités, dans ce chapitre, porteront attention sur les paramètres clés pris en compte pour l'analyse de l'acquisition du signal GPS, et les conséquences de la transition du signal à travers le canal de transmission et les composantes électroniques du récepteur, sur ces paramètres. Ainsi, nous pourrons passer à l'étape suivante qui consiste à choisir l'architecture de notre système numérique d'acquisition, et entreprendre l'analyse de la stratégie à modéliser. On s'intéressera au traitement du récepteur à savoir les opérations accomplies pour accommoder le signal au bloc d'acquisition visé par l'étude, en détaillant les transformations subies par le signal.

Ainsi, nous entamerons avec le principe de positionnement de la constellation *GNSS*, puis nous introduirons les éléments de la transmission d'un signal *GNSS* dans le but de relever les paramètres clés de l'acquisition. Pour cela on prendra cas du signal *GPS* afin d'évaluer un signal concret. Ce chapitre comprendra les généralités du système *GPS*, notamment la structure du signal *GPS* et ses caractéristiques. Puis on évoquera la transmission du signal, dans le but d'établir un *bilan de liaison*.

#### I.2. Constellation

Il y a un total de 24 satellites *GPS*, divisés en six orbites, chaque orbite a quatre satellites. Chaque orbite fait un angle de 55 degrés avec l'équateur, c'est l'*inclinaison*. Les orbites sont séparées de 60 degrés pour couvrir 360 degrés. Le rayon de l'orbite du satellite est de 26 560 km et il tourne autour de la terre deux fois par *jour sidéral* [1]. À tout moment et en tout lieu sur la terre, en négligeant des obstacles tels que les montagnes et les immeubles de grandes hauteurs, un récepteur *GPS* doit avoir une visibilité directe, et recevoir des signaux de 4 à 11 satellites [2].

Le rayon de la terre est de 6 378 km autour de l'équateur et de 6 357 km en passant à travers les pôles, et le rayon moyen peut être considéré comme 6 368 km. Le rayon de l'orbite du satellite est de 26 560 km, ce qui correspond à environ 20 192 km (26560 - 6 368km) audessus de la surface de la Terre [1]. Cette hauteur est approximativement la distance la plus courte entre un utilisateur sur la surface de la terre et un satellite, qui se produit vers *le zénith* ou une élévation angle d'environ 90 degrés [1]. La distance depuis un satellite vue *d'horizon* par l'utilisateur est de 25 785 km [1].

On peut voir que les retards de la transmission satellites-terre sont dans la plage de 67 ms (20 192 km/c) à 86 ms (25 785 km/c), où c est la vitesse de la lumière. Si l'utilisateur est à la surface de la terre, le temps de retard différentiel maximal de deux satellites différents doit être compris entre 19 (86–67) ms.

**Tableau I.1** : paramètres de la constellation GPS.

## Constellation

| Nombre de satellites                  | 24          |

|---------------------------------------|-------------|

| Nombre de plans orbitaux              | 6           |

| Inclinaison de l'orbite               | 55°         |

| Rayon de l'orbite                     | 26560 km    |

| Période                               | 11hrs 57min |

|                                       | 57.26 sec   |

| Distance la plus proche de la surface | 20192 km    |

| Distance la plus longue de la surface | 25785 km    |

| Temps de propagation                  | 67-86 ms    |

Source: Fundamentals of Global Positioning System Receivers: A Software Approach

James Bao-Yen Tsui

L'estimation du temps de propagation s'interprète, géométriquement, par une distance entre le satellite et le récepteur, une donnée nécessaire pour le calcul de la position. Le signal émis du satellite, contenant les informations requises pour le calcul de position (I.4.1), est porté par un code d'une période d'une milliseconde (I.4.3) Doté de 1023 bits sur une fréquence d'un Méga Hertz. Ainsi, connaître la position du 1<sup>e</sup> bit sur le code reçu indique le retard sur une milliseconde de plus que l'estimation initiale du temps de propagation est donc une estimation précise de la distance. Sachant que 1 milliseconde d'erreur a pour effet 300 km d'erreur sur la position, le système doit être précis et fiable (III.3.1) (III.3.2).

## I.3. Principe de détermination de la position

En deux dimensions, l'estimation d'une distance à partir d'un point fixe est représentée par un cercle. Avec deux points et deux distances, l'intersection entre deux cercles donne deux points, un troisième point et une troisième distance sont nécessaire pour déterminer une solution unique : un point. De même dans les systèmes de positionnement par satellites en trois dimensions, l'intersection de deux sphères donne un cercle, le cercle intersecté avec une autre sphère donne deux points. L'un des deux points est considéré obsolète par le système géométrique vu que l'un sera positionné sur la surface terrestre tandis que l'autre sera beaucoup plus loin dans l'espace [2].

Dans la technologie *GPS*, la position du satellite est connue à partir des données des éphémérides transmises par le satellite. La distance mesurée entre l'utilisateur et le satellite est supposée être très précise et non biaisée. Cependant, la distance mesurée entre le récepteur et le satellite a un biais inconnu constant, parce que l'horloge de l'utilisateur est généralement différente de l'horloge des satellites. Afin de résoudre cette erreur de biais, un satellite supplémentaire est requis [8].

Le principe pour déterminer la position du récepteur est d'initialiser une position qui pourrait être le centre de la terre par exemple, puis, effectuer des itérations aux équations de pseudo distances.

#### I.3.1. Calcul des distances

L'estimation de la distance via le système *GNSS* repose sur la mesure du temps de propagation, de l'émission à la réception du signal électromagnétique. La mesure du temps de propagation du signal provenant de plusieurs satellites permet, par multilateration, de

déterminer la position du récepteur. Le signal voyageant à la vitesse de la lumière c. La distance recherchée est donnée par :

$$R = c \times T \tag{I.1}$$

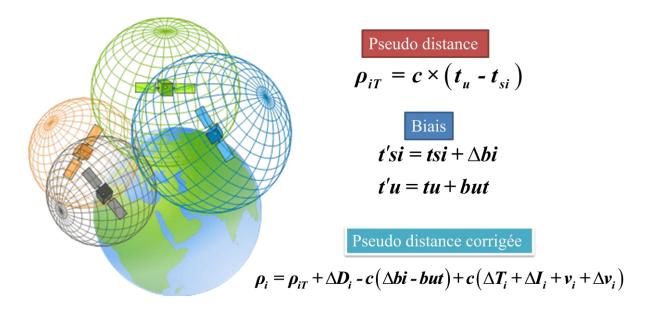

Chaque satellite envoie un signal à un instant  $t_{si}$ . Le récepteur reçoit le signal à l'instant  $t_u$  après une certaine durée. La distance entre le satellite i et le récepteur est :

$$\rho_{iT} = c \times (t_u - t_{si}) \tag{I.2}$$

Ou c est la vitesse de la lumière ; $\rho_{iT}$ est souvent désignée comme la vraie valeur de pseudo-distance d'un utilisateur à un satellite i,  $t_{si}$  est appelée l'instant réel de transmission depuis le satellite i,  $t_u$  est l'instant de réception réel. Du point de vue pratique, il est difficile, voire impossible, d'obtenir l'heure correcte du satellite ou de l'utilisateur. L'heure satellite d'horloge réelle t'si, et l'instant d'horloge utilisateur réel t'u est lié à l'instant réel par :

$$t'si = tsi + \Delta bi$$

$$t'u = tu + but$$

(I.3)

Ou  $\Delta bi$ : l'erreur d'horloge du satellite ; but: l'erreur d'horloge du récepteur. D'autres facteurs peuvent affecter la mesure de la pseudo-distance dont son équation est la suivante [1] [2] [3] [15][19] :

$$\rho_{i} = \rho_{iT} + \Delta D_{i} - c(\Delta bi - but) + c(\Delta T_{i} + \Delta I_{i} + v_{i} + \Delta v_{i})$$

(I.4)

Ou  $\Delta D_i$ : l'effet de l'erreur de position du satellite sur la distance ; $\Delta T_i$ : Le retard du à la troposphère ;  $\Delta I_i$ : Le retard du à l'ionosphère ;  $v_i$ : Bruit ;  $\Delta v_i$ : Correction temps.

#### I.3.2. La Dilution de Précision (DOP)

Un récepteur peut recevoir des signaux de plus de quatre satellites. Pour calculer la position, on pourrait éventuellement utiliser tous les signaux, cela dit, les positions des combinaisons des satellites influents sur la précision des mesures, cela est dû à leurs positions dans l'espace [1].

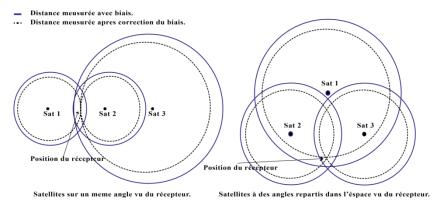

**Figure I.2**: Dispositions de satellites et la relation avec la précision de mesure.

La **Figure I.2** montre deux combinaisons possibles et illustre leurs impacts sur la précision de la position. Les cercles en gras représentent la distance mesurée par le récepteur en considérant le biais d'horloge, et les cercles en pointillés représentent les cercles des distances après la correction du biais. Sur **Figure I.2** à gauche, l'erreur de la position est plus grande que celle de la figure à droite, car dans le 1<sup>er</sup> cas les positions des satellites sont sur une seule ligne, tandis que dans l'autre figure, les satellites sont répartis avec des angles bien clairs, et il est difficile de mesurer la position avec précision à partir de points tangentiels On peut également mesurer les triangles formés par les satellites, la plus grande surface de ces triangles détermine la position la plus proche du réel. Donc dans un cas en 3D, il est préférable de maximiser le volume défini par les satellites pris en comptes pour le calcul de la position du récepteur.

The Dilution Of Précision DOP est utilisé pour évaluer la précision des mesures. Plusieurs définitions existent pour le DOP, et qui sont en fonction de la géométrie des satellites dans l'espace de tel que leurs positions déterminent les valeurs des DOP's [2] [19].

GDOP =

$$\frac{1}{\sigma} \sqrt{\sigma_x^2 + \sigma_y^2 + \sigma_z^2 + \sigma_b^2}$$

PDOP =  $\frac{1}{\sigma} \sqrt{\sigma_x^2 + \sigma_y^2 + \sigma_z^2}$

HDOP =  $\frac{1}{\sigma} \sqrt{\sigma_x^2 + \sigma_y^2}$

VDOP =  $\frac{\sigma_z}{\sigma}$

TDOP =  $\frac{\sigma_b}{\sigma}$

Ou  $\sigma$  est la variance de l'erreur de la pseudo distance,  $\sigma_x$ ,  $\sigma_y$ ,  $\sigma_z$  correspondent aux erreurs de mesures dans les axes x,y,z.  $\sigma_b$  est la variance de l'erreur de l'horloge exprimée en distance. La plus petite valeur du DOP révèle la meilleure combinaison pour le calcul de la position avec précision.

## I.4. Espaces de modélisation du signal

Le système *GPS* comprend trois segments : le segment de control, le segment espace et le segment utilisateur. Le segment de control comprend plusieurs stations au sol dont la station mère principale située à *Falcon Air Force Base, Colorado Springs, CO*, et qui traite les rapports de fonctionnement et positionnement des satellites, reçus des autres stations. Ainsi, la station mère gère les données qui vont être transmises aux satellites, ces données comprennent principalement la mise à jour des messages de navigation et corrections (orbite, temps, etc.)[4].

La répartition des satellites dans l'espace est faite en sorte qu'au minimum 11 satellites soient visibles, et que la constellation englobe la terre en termes de couverture, en plus de minimiser l'impact de panne d'un satellite sur les performances du système en termes de couverture et du *DOP* [1][2][4]. Au moins trois espaces de modélisations et de mesures des paramètres du signal sont nécessaires pour bien évaluer et expliquer les changements que subit le signal dans la chaine de transmission, au niveau du satellite, de l'espace et du récepteur [4].

## I.4.1. Le signal au niveau du satellite

Afin de comprendre les opérations établies sur le signal reçu, il est d'abord nécessaire de connaître sa forme, ses composantes, et ses caractéristiques au niveau du satellite émetteur.

## > Fréquence du signal

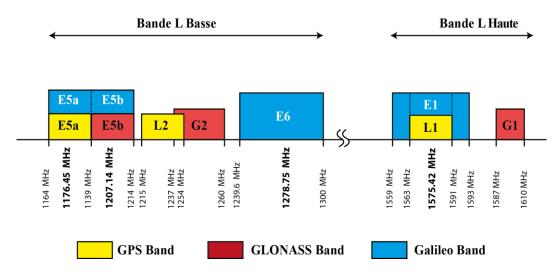

Le signal GPS civile est envoyé sur deux fréquences porteuses  $F_{L1}$  et  $F_{L2}$ .

$$F_{L1} = 154 \ F_0 = 1575.42 \ [MHz]$$

$$F_{L2} = 120 \ F_0 = 1227.60 \ [MHz]$$

Ces fréquences sont en *UHF* () spécifiquement la bande L. La bande L est choisie car l'atmosphère est transparente pour la gamme *UHF* et *SHF*. Pour les gammes moindres, l'ionosphère devient de plus en plus opaque pour les ondes radio. Au-dessus de la bande *X* l'onde devient tellement petite qu'elle est d'autant susceptible d'être affectée par l'oxygène et la vapeur d'eau. A noter que la fréquence d'émission est très précise vu l'utilisation de l'horloge atomique au sein des satellites [8].

Figure I.3: Répartition des fréquences pour le système GNSS.

## Donnée de navigation

Les informations contenues dans le message de navigation ont la structure de trames de base représentées ci-dessous

Figure I.4: Message de navigation d'un signal GPS.

Un message complet se compose de 25 trames, chacune contenant 1500 bits à 50 Hz (ce qui signifie que l'on transmet 50 bits par secondes). Chaque trame est subdivisée en cinq sous-trames de 300 bits : 6sec et chaque sous-trame se compose de 10 mots de 30 bits : 0,6sec. Le premier mot de chaque sous-trame est SLT (mot de télémétrie), il contient des informations sur l'actualité des éphémérides. Il est suivi du mot Comment (mot de transfert) contenant le nombre Z époques compté. Ces données incluent le temps écoulé depuis le dernier redémarrage. La transmission du message complet de navigation de 25 trames nécessite 750s ou 12,5 min [3] [5].

Les données restantes de la première sous-trame contiennent des données sur l'état et la précision du satellite ainsi que les valeurs de correction d'horloge. Les deuxièmes et troisièmes sous-trames contiennent des paramètres de l'éphéméride, et les sous-trames 4 et 5 comprennent enfin les almanachs [3] [5].

Les systèmes GNSS sont en général des systèmes DSSS « DIRECT SEQUENCE SPREAD SPECTRUM » étalement de spectre à séquence directe, une technique d'étalement de spectres utilisée dans le but du DSSS et d'une part est de rendre les signaux, occupants une bande de fréquence, plus résistants aux brouillages et aux interférences, et d'autre part de permettre à plusieurs équipements de partager la même fréquence porteuse et pour cela ils sont combinés à un code d'étalement. Les propriétés de corrélation des codes d'étalement permettent d'identifier le signal émis et de calculer les temps de transmission [3] [8] [1].

## **≻** Code C/A

Acronyme de « *Coarse Acquisition* », en français : « acquisition brute »est un code binaire pseudo- aléatoire (code qui revient périodiquement à la même structure de bit (un et zéro) ou *PRN* (*en anglais Pseudo Random Noise*) de débit 1,023 Mbit/sec de période 1 ms [3].

**Figure I.5**: Forme d'un code PRN.

Figure I.6 : Spectre de fréquence du code PRN.

A partir du la **Figure I.6** on remarque que le lobe principal, qui contient une grande puissance est contenu dans une bande de 2 MHz.

La transmission des données se fait selon le principe *CDMA* (Code Division Multiple Access), c'est-à-dire que chaque satellite de la constellation dispose d'une clé (mot d'un code) à l'aide de laquelle il code l'information à transmettre. Connaissant la clé d'un satellite donné, le récepteur est capable d'extraire le message de ce satellite du signal composite reçu. Le message transmis résulte de l'addition modulo-2 (message de navigation et des codes). Avec le

code modulé ci-dessus la porteuse subit une modulation de type *BPSK* (*Binary Phase Shift keying*). Ainsi la porteuse fait un saut de phase de 180° à chaque changement d'état et codé en NRZ. Le signal GNSS reçu peut être écrit [1][2][3][19] :

$$r_{RF}(t) = \sum_{i=1}^{L} y_i(t) + \eta_{RF}(t)$$

(I.6)

Qui est la somme de L signaux différents pour L satellites émetteurs et n(t) désigne le bruit environnent.

$$y_{i}(t) = \sqrt{2P} \cdot \left(c_{i}(t) \oplus d_{i}(t)\right) \cdot \cos\left(2\pi F_{L1}t\right) + \sqrt{2P} \cdot \left(p_{i}(t) \oplus d_{i}(t)\right) \cdot \sin\left(2\pi F_{L1}t\right) + \sqrt{2P} \cdot \left(p_{i}(t) \oplus d_{i}(t)\right) \cdot \sin\left(2\pi F_{L2}t\right)$$

$$+ \sqrt{2P} \cdot \left(p_{i}(t) \oplus d_{i}(t)\right) \cdot \sin\left(2\pi F_{L2}t\right)$$

(I.7)

P: représente la puissance totale ;  $c_i$  est le code d'étalement du satellite i ;  $d_i$  représente le message de navigation ;  $p_i$  est le code d'étalement dédié au signal militaire appelé code P au lieu de code C/A [3]. Dans notre étude on prendra en considération le code C/A uniquement.

$$y_{i}(t) = \sqrt{2P} \cdot \left(c_{i}(t) \oplus d_{i}(t)\right) \cdot \cos\left(2\pi F_{L1}t\right)$$

(I.8)

**Figure I.7**: Echantillon d'un signal GPS. Code PRN modulé par une porteuse

On remarque qu'un changement de phase se produit à plusieurs reprises, signifiant un changement de signe du code *PRN* à chaque changement de phase de 180°, c'est une modulation *BPSK*.

## I.4.2. Propagation du signal dans l'espace

Dans cette section on parlera de la propagation du signal de l'émetteur au récepteur, afin d'établir un bilan de liaison de la transmission, cela nous permettra de déterminer la puissance reçu au niveau du récepteur, les changements subis par signal et de définir les éléments susceptibles d'atténuer le signal ou de modifier sa fréquence dans l'espace.

Figure I.1: Illustration des principaux espaces de modélisations du signal.

#### Gain de l'antenne d'émission

Dans un bilan de liaison, le gain est la caractéristique la plus importante d'une antenne. Il est défini comme étant le rapport de la puissance rayonnée par l'antenne, dans une direction, par unité d'angle solide, sur la puissance rayonnée par une antenne référence par unité d'angle solide. Ce gain est dit absolu si l'antenne référence est isotrope, c'est-à-dire qu'elle rayonne uniformément dans toutes les directions. Il est exprimé en dBi. Le gain absolu est souvent utilisé dans le calcul d'une liaison par satellite. Pour un satellite de la constellation *GPS*, on considère que la puissance générée par le satellite est de 33 watts, et pour une antenne isotopique [2], la densité de puissance sera:

$$Pt = P \times G \quad [watts] = P + G \quad [dBw] \tag{I.9}$$

$$P = \frac{Pt}{4.\pi R^2} \left[ watts / m^2 \right]$$

$$P[dB] = 10.\log \left( \frac{Pt}{4\pi R^2} \right) = 10\log(Pt) - 10\log(4\pi R^2)$$

(I.10)

Pt : Puissance total émise par le satellite

## P: Puissance reçu au niveau du récepteur

Puisque le niveau de puissance est inversement proportionnel au carré de la distance en dB, la différence de niveau de puissance peut être trouvée comme :

$$\Delta P = 10.\log\left(\frac{25785^2}{20192^2}\right) = 2.1[dB] \tag{I.11}$$

L'antenne, , ayant une directivité et une ouverture du lobe principal, à un gain qui représente la fraction ou le rapport géométrique de son ouverture sur celle de la sphère de la puissance isotopique dissipée [2].

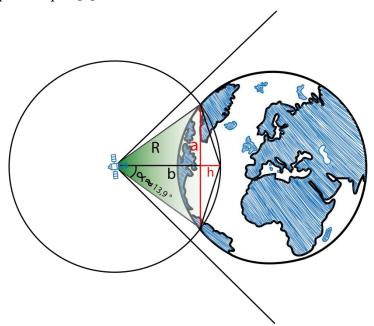

Figure I.8 : Gain de l'antenne d'émission.

Surface d'une sphère :  $4\pi R^2$

Surface d'un arc sphérique :  $a = R \sin(\alpha)$ ,  $b = R \cos(\alpha)$

On

$$a \ h = R - b = R(1 - \cos \alpha)$$

;  $p = \sqrt{h^2 + a^2} = R\sqrt{2 - 2\cos \alpha}$

Le rapport s'écrit :

$$G(\alpha) = \frac{4\pi R^2}{\pi p^2} = \frac{2}{1 - \cos \alpha}$$

La valeur approximative de  $\alpha$  est de 13.87° qui est l'angle solide pour couvrir la terre [2].

**Note**: le gain d'antenne s'ajuste afin recevoir une puissance minimum garantie sur toute la surface terrestre rayonnée

#### Atténuation du signal

La puissance reçue, garantie aux récepteurs, peut être calculée à partir de la puissance émise par le satellite, largeur de bande de l'antenne émettrice, la distance entre le satellite et le récepteur ainsi que la surface effective de l'antenne de réception. On aura la distance du satellite de la surface  $R=20000\,Km$  la surface effective A d'une antenne  $A_{eff}=\frac{\lambda^2}{4\pi}$  avec  $\lambda=0.19m$ : longueur d'onde. On notera également le gain de l'antenne de réceptionGa=1=0dB La puissance reçu s'écrit :

$$\Pr e \varsigma ue = \frac{Pt.Gt.A}{4.\pi R^2} = 1.41*10^{-16} [w] = -158.5 [dBw] = -128.5 [dBm]$$

(I.12)

La puissance reçue comme estimée est très faible et le spectre est étalé, donc il ne peut être directement analysé par le récepteur [1] [2][8].

## Pertes de propagation

L'atmosphère autour de la Terre affectera la vitesse de déplacement du signal GPS et provoque des erreurs de mesure. Ces erreurs devraient être corrigées. Pour GPS application, l'atmosphère est généralement divisée en deux parties : *l'ionosphère* et la *troposphère*. La *troposphère* est la plus proche des deux à la surface de la terre tandis que l'ionosphère est audessus de la troposphère. La troposphère contient les particules neutres et l'ionosphère contiennent des ions libres.

L'ionosphère, couche haute de l'atmosphère, contient des particules chargées qui réduisent la vitesse de propagation et allongent le chemin parcouru par réfraction (diminution de la vitesse de groupe et avance de la phase) causant des erreurs pouvant atteindre plusieurs dizaines de mètres. Le modèle de correction ionosphérique utilisé en aéronautique [15] (Annexe 10 volume13 OACI 3.1.2.4 Correction du retard ionosphérique)

La troposphère, couche basse de l'atmosphère, contient de la vapeur d'eau. Elle ralentit le signal et peut causer des erreurs de l'ordre de 2 à 25m, et des atténuations inférieures à 0.5dB. Ces effets varient en fonction de l'angle d'élévation, de la pression et de la température du milieu. Des modèles mathématiques, prenant en compte ces paramètres, peuvent apporter des corrections sur les retards induits par la troposphère. Il est aussi important de noter que la troposphère est un milieu non dispersif et donc, affecte les signaux transmis à différentes fréquences de la même manière.

Remarque: Il est à noter que l'impact de l'ionosphère sur la transmission des signaux dépend directement de la fréquence (évolution du retard en1/f2). L'utilisation de 2 fréquences différentes (par exemple L1 et L2 en GPS) permet alors d'estimer et de compenser les retards induits par l'ionosphère. Cependant, les récepteurs classiquement rencontrés sont mono fréquence.

## **Effet Doppler**

La vitesse du satellite et celle du récepteur influent sur le signal reçu. Ces deux vitesses génèrent une déviation de la fréquence du signal reçu, de celle émise [8]. Cette déviation est en fonction de plusieurs paramètres, c'est l'effet Doppler. On illustrera le phénomène comme suit, nous nous intéresserons d'abord, à la vitesse du satellite :

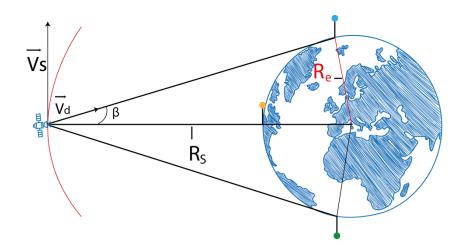

**Figure I.9**: *vitesse du satellite et effet doppler.*

$V_s$ : est la vitesse radiale du satellite ;  $R_e$ : Rayon de la terre  $R_s$ : Rayon de l'orbite ;  $\beta$ : Angle de position du satellite par rapport au zénith.

Les trois illustrations des positions de récepteur sont indiquées par les trois points, bleu jaune et vert, ces trois points sont considérés comme les points aux limites, vues du récepteur. Le satellite et au zénith pour le point jaune, et à l'horizon aux points vert et bleu.

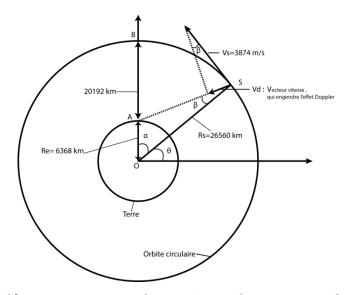

**Figure I.10** : Frequence Doppler causée par le mouvement du satellite.

Dans la figure **I.10** le satellite est à la position S et l'utilisateur est à la position A. La vitesse du satellite peut être calculée à partir de sa vitesse angulaire ( $d\alpha/dt$ ) et la vitesse radiale [1].

$$\frac{d\alpha}{dt} = \frac{2\pi}{12 \times 3600} = 1.458 \times 10^{-4} \quad [rad/s]$$

$$V_s = Rs \frac{d\alpha}{dt} = 26560 \text{ km} \times 1.458 \times 10^{-4} = 3874 \quad [m/s]$$

(I.13)

La fréquence Doppler est due à la vectrice vitesse en direction du récepteur :

$$V_{d} = V_{s} \sin \beta \tag{I.14}$$

En utilisant la loi de cosinus et du sinus sur le triangle OAS, on aura :

$$AS^{2} = Rs^{2} + Re^{2} - 2ReRs.\cos\alpha = Rs^{2} + Re^{2} - 2ReRs.\sin\theta$$

$$\frac{\sin\beta}{\sin\alpha} = \frac{\sin\beta}{\cos\theta} = \frac{Re}{AS}$$

(I.15)

En remplaçant dans l'équation (1.15):

$$V_d = \frac{V_S \operatorname{Re} \cos \theta}{AS} = \frac{V_S \operatorname{Re} \cos \theta}{\sqrt{Rs^2 + \operatorname{Re}^2 - 2\operatorname{Re} Rs.\sin \theta}}$$

(I.16)

Quand  $\theta=\pi/2$ , la vitesse doppler  $V_d$  est nulle. La vitesse est à son maximum à l'horizon et  $\theta$  est donné comme suit :

$$\sin \theta = \frac{\text{Re}}{Rs} \quad or \quad \theta = \sin^{-1} \left(\frac{\text{Re}}{Rs}\right) \approx 0.242 [rad]$$

(I.17)

Le module du vecteur vitesse  $V_d$  à son maximum se calcule comme suit :

$$V_{dm} = \frac{V_s \text{ Re}}{Rs} = \frac{3874 \times 6368}{26560} \approx 929 [m/s]$$

(I.18)

On obtient la fréquence Doppler à partir de la fréquence RF [1][8]:

$$f_D = \frac{f_{RF} \times V_{dm}}{c} = \frac{1575.42 \times 929}{3 \times 10^8} \approx 4.9 [KHz]$$

(I.19)

C'est pourquoi pour un récepteur statique la déviation est entre -+5khz. Si un récepteur se déplace à une grande vitesse l'effet doppler dû au déplacement du récepteur doit être pris en considération, ces valeurs déterminent la plage de recherche de la fréquence dans l'acquisition.[1]

Pour la fréquence du code qui est relativement faible, à partir de sa fréquence, mais peut causer un désalignement du code généré avec le code reçu qui n'est pas désiré .Si on échantillonne le signal à 5MHz or la fréquence du code pourrait se décaler de 15 H donc à un temps 1/15hz il y aura un décalage d'un chip entre les codes.

## I.4.3/ Evolution du signal dans le récepteur

Les récepteurs radio fréquence sont caractérisés par leur sensibilité et leur sélectivité [1] :

- ➤ La sensibilité définit la capacité du système à détecter et à amplifier le signal recherché quand son amplitude est faible.

- La sélectivité évalue la capacité du système à détecter et à amplifier le signal recherché lorsque celui-ci est entouré de signaux parasites d'amplitude plus forte.

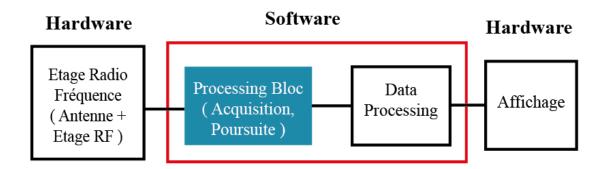

**Figure I.11**: composantes d'un récepteur GNSS et leurs rôles dans la chaine.

Un récepteur *GNSS* peut être décomposé en trois bloques significatifs[8][9][3], comme illustré dans la **Figure I.12**.

Le premier étant l'antenne et l'étage radio fréquence « FRONT END » (filtres, amplificateurs, Mélangeur, ADC) qui est chargé de conditionner le signal pour les traitements soft, c'est la partie hardware.

- Pour le deuxième bloque du traitement de signal appelé « PROCESSING BLOC » le traitement consiste à l'estimation des paramètres du signal, à savoir le code du satellite émetteur, le temps de propagation et la fréquence de réception, c'est « l'acquisition » l'autre opération de ce bloc est la poursuite ou des boucles d'asservissement poursuivent les paramètres obtenus de l'acquisition, ce qui demande moins de temps de traitement, néanmoins l'acquisition est nécessaire.

- Le 3ème bloque traite les données de navigation pour but d'acquérir le message de navigation, contenant les informations permettant de calculer les équations de navigation et obtenir la position et la vitesse du récepteur.

## I.4.3.1. Etage Radio Fréquence

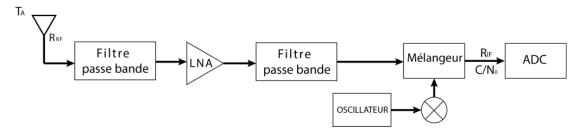

Figure I.12 : Architecture généralisée d'un étage radio fréquence d'un récepteur GNSS.

Il est nécessaire d'étudier le comportement du signal à travers l'antenne et l'étage Radio Fréquence nommé ensemble «  $FRONT\ END$  », afin d'établir un bilan de liaison entre le signal reçu et celui qu'on va traiter dans l'étage d'acquisition, en définissant les variables pondérantes sur ce bilan. On s'intéressera également au  $C/N_0$  et on cherchera à exprimer la variable de sortie de l'étage RF en fonction du  $C/N_0$  à l'entrée du récepteur. Ce  $C/N_0$  sera important pour évaluer la sensibilité des détecteurs dans le chapitre III. Le signal intercepté par l'antenne subit deux traitements l'un analogique et l'autre Numérique. Le signal étant numérisé, l'étage d'acquisition qu'on verra en détails par la suite interviendra afin de relever les informations de temps et de fréquence recherchées.

Il existe deux manières de convertir le signal analogique en signal discret [1][3][5]:

✓ Une digitalisation directe, directement à la fréquence L1: Pour réaliser une digitalisation directe, un convertisseur analogique numérique à fréquence élevée est nécessaire, ce qui n'est pas simple à concevoir, aussi l'amplificateur à fréquence

élevée est plus onéreux, de plus à une fréquence haute, un filtre à bande étroite cause des erreurs.

✓ Convertir le signal de la fréquence reçue à une fréquence intermédiaire f<sub>IF</sub>, puis procéder à la digitalisation : Le passage à une fréquence intermédiaire détériore le signal en niveau (SNR) et en fréquence, tel que des atténuations (faibles) dues à la non linéarité des filtres engendrant des erreurs de quantification et peuvent erroner l'information reçue). A une fréquence bassef<sub>IF</sub>, les filtres à bande étroite sont précis et engendrent une moindre perte tandis que l'oscillateur et le mixeur sont encombrants et causent des erreurs sur la fréquence, et donc auront un impact sur le signal reçu.

**Note :** Pour un traitement soft sur un signal GPS, il est requis d'avoir un signal numérique échantillonné, cet échantillon sera enregistré pour être traité, un minimum de 30 secondes d'enregistrement est nécessaire et ainsi l'espace de la mémoire influx sur la latence du processus.

## > Fonctionnement général

Il existe plusieurs types d'architectures de récepteurs, dont les plus connus sont les architectures hétérodynes, homodynes ou les architectures à faible fréquence intermédiaire. Toutefois, on peut généraliser le fonctionnement de l'étage radio fréquence en notant les caractéristiques des composantes et leur effet sur le signal [20].

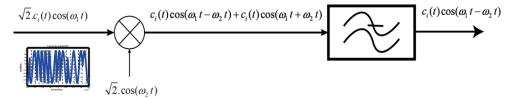

La partie *Front end* est constituée de filtres, amplificateurs, de mélangeurs et d'oscillateurs locaux. Le canal désiré est sélectionné par le biais d'un filtre passe bande, puis un amplificateur faible bruit amplifie le signal, très faible pour être quantifié directement, et cela tout en limitant le bruit à l'entrée du mélangeur. Le signal est ensuite transposé à une ou plusieurs fréquences plus basses, grâce à un mélangeur qui multiplie ce signal par une sinusoïde de fréquence F<sub>01</sub> fournie par l'oscillateur local. Le résultat de ce mélange est deux composantes aux fréquences *Fporteuse* † *fol*.Le filtre passe bas en sortie du mélangeur est alors utilisé pour ne retenir que la fréquence haute.[20]

Figure I.13 : Rôle du mélangeur et du filtre passe bas.

## > Antenne de réception

Une antenne GPS doit avoir une grande ouverture pour recevoir un nombre maximal de signaux. L'exigence commune est de recevoir les signaux de tous les satellites à environ 5 degrés au-dessus de l'horizon. Toutefois, la Combinaison de satellites à faible angle d'élévation et des angles d'élévation élevés peut engendrer une faible valeur de dilution géométrique de précision (GDOP) [2][1][21]. De plus, d'un faible angle d'élévation viennent beaucoup d'interférences et multi trajet. Par conséquent, en choisissant une antenne GPS, un compromis entre le nombre maximal de satellites captés par l'antenne et le brouillage causé par des signaux non désirés doit être soigneusement évalué [2] [5].

On peut citer les principales caractéristiques d'une antenne GNSS [2] :

- ✓ Le gain : Dans les systèmes CDMA il est préférable de recevoir des signaux d'amplitudes similaires, car un signal à amplitude supérieur parrapport aux autres pourrait les rendre indétectables, pour cette raison on considérera notre antenne réceptrice isotopique.[2]

- ✓ La bande passante : est choisie selon les fréquences dédiées, une bande étroite diminue l'impact d'interférences.

La polarisation et le diagramme de rayonnement :sont aussi un atout pour atténuer les Multi trajets d'angles plats par rapport à l'angle d'ouverture de l'antenne GPS. Par conséquent, même les signaux des satellites avec une faible élévation seront atténués ce qui explique en partie l'angle de garde que spécifie l'ouverture de lobe de l'antenne d'émission.

Remarque: Si l'antenne est jumelée avec un amplificateur (antenne active) on peut relier le récepteur à l'antenne avec un long câble sans qu'il y est de pertes, la raison est apparente dans (.4.3.4).

## Mélangeur Oscillateurs locaux

Le mélangeur est utilisé pour la conversion de la fréquence du signal reçu. Étant donné la non-linéarité de ce module, il génère un très grand nombre de signaux parasites dont certains peuvent se retrouver à l'intérieur de la bande utile, qui ne vont pas être filtrés. La perte de conversion du mélangeur, généralement entre 3 et 9 dB [2].

➤ L'oscillateur local fournit au mélangeur le signal nécessaire à la conversion en fréquence du signal reçu. La fréquence du signal de l'oscillateur local doit être très stable, précise et comporter des signaux parasites extrêmement faibles. Il n'empêche

qu'en réalité il existe toujours une erreur (un résidu de fréquence), cela est un inconvénient pour la corrélation qu'on verra plus loin.[19]

# > Filtre passe bande

Un filtre passe bande est un filtre ne laissant passer qu'une bande ou intervalle de fréquences, compris entre une fréquence de coupure basse et une fréquence de coupure haute du filtre. Caractérisé par sa fréquence de coupure, conventionnellement, cette limite est souvent fixée à la fréquence pour laquelle la puissance de sortie est réduite à moitié pour un signal d'entrée de même amplitude par rapport à la puissance de sortie à la fréquence de référence [1].

Vu le spectre du signal GPS, nous prenons en considération lors de la simulation que le filtre a une bande de fréquence de 2MHz autour de la fréquence porteuse, ou on pourra récupérer la majeure partie de la puissance du signal. En pratique, ce type de filtre laisse passer des résidus de fréquence au-delàs de la bande voulue, également le filtrage se fait graduellement, ce qui provoque une atténuation du signal et un ajout de bruit. On notera cette atténuation  $\Delta_{\rm IF}$  qu'on soustrait directement au (SNR) $_0$  idéale (sans pertes).

Si X (t) est un processus aléatoire gaussien, appliqué à un système LTI de réponse impulsionnelle h(t), alors le processus de sortie est également gaussien. Par conséquent, le processus de sortie Y (t) sera complètement spécifié, étant donné le processus d'entrée X (t) et la réponse impulsionnelle h (t).[9]

# > Amplificateurs

La plus importante des caractéristiques de ce module est son gain. Celui-ci doit être suffisamment élevé pour minimiser la contribution des modules subséquents au bruit, particulièrement celle du mélangeur. Il faudra toutefois s'assurer de ne pas saturer le mélangeur, avec un gain trop élevé [1][2].

L'amplificateur utilisé dans le récepteur GNSS est un amplificateur «LNA: Low Noise Amplificator ». La caractéristique de cet amplificateur est son très faible bruit. Ce module est conçu de telle sorte que sa contribution au bruit soit minimale permettant ainsi la détection de signaux très faibles. C'est cet amplificateur qui détermine la sensibilité du récepteur. L'amplification est nécessaire car la sensibilité du convertisseur analogique numérique requiert un niveau du signal beaucoup plus important que le niveau reçu, toute fois le bruit omniprésent, une trop forte amplification risque de saturer l'ADC avec le bruit.[1][2][3]

| Tableau I.2 :  | Bilan de | liaison | émission | réception  |   |

|----------------|----------|---------|----------|------------|---|

| I abicau I.2 . | Duan ac  | uuuson  | CHUSSIOH | reception. | • |

| Paramètres                     | Valeur en SI               | En dB |  |

|--------------------------------|----------------------------|-------|--|

| Gain d'antenne d'émission      | 10                         |       |  |

| Puissance émise                | 294 W                      |       |  |

| Pertes d'espace                | 1,95 e-16 m <sup>-2</sup>  |       |  |

| Pertes atmosphériques          | 0,9                        | -0,5  |  |

| Puissance reçue                | 4,92 e-14 W/m <sup>2</sup> |       |  |

| Gain d'antenne de<br>réception | 1                          | 0     |  |

| Surface effective              | 2,87 e-3 m <sup>2</sup>    |       |  |

| Pertes de polarisation         | 0,50                       | -3    |  |

| Puissance reçue effective      | 1,41*10^-16 W = -158,5dBw  |       |  |

L'amplification concerne le niveau du signal, tel que le niveau minimum reçu garanti, est de - 130 dbm pour le signal GPS ce qui revient à choisir un amplificateur sensible à cette valeur.[2] [1] [3] [5]

# I.4.3.2. Le Convertisseur Analogique-Numérique (ADC)

La conversion de données de l'analogique vers le numérique permet de passer d'un signal continu dans le temps et de valeurs continues à un signal à temps discret et à valeurs discrètes. Un échantillonneur bloqueur par exemple pourra prélever à période fixe la valeur du signal à convertir et maintenir la valeur constante (bloquer) le temps nécessaire à la quantification. Quantifier une valeur de s(n) c'est l'approximer grâce à un multiple entier d'une quantité élémentaire $\Delta$ =2Vmax/Nbit dite « Pas de quantification ». La discrétisation, à l'aide d'un quantificateur, des valeurs continues provoque une perte d'informations dû à des erreurs de quantification qui diffèrent d'un dispositif à un autre. Nous pouvons dès lors assimiler l'erreur de quantification e(t) est une variable aléatoire de répartition uniforme et on assume qu'il s'agit d'un bruit blanc gaussien sa puissance s'écrit [20] :

$$Pe = \int_{-\Delta/2}^{\Delta/2} e(t)^2 pe(t) dt$$

$$-\Delta/2$$

$$Pe = \int_{-\Delta/2}^{\Delta/2} e^2 \frac{1}{\Delta} dt = \frac{\Delta}{12}$$

$$(I.22)$$

Pour minimiser cet effet on peut [1] [20] :

Soit augmenter la précision du quantificateur ce qui réduirait le pas de quantification : l'ajout d'un bit de précision divise la valeur de  $\Delta$  par un facteur 2.

✓ Soit augmenter la fréquence d'échantillonnage :

Les variables aléatoires de répartition uniforme engendrent un bruit de type blanc, c'est-à-dire de Densité Spectrale de Puissance (DSP) constante vis-à-vis des fréquences. Le bruit de quantification e(t) est donc un bruit blanc, nous noterons sa  $DSP|E(f)|^2$ . Pour calculer cette valeur, nous considérons que la condition de Shannon est remplie.

$$Pe = \int_{-F_{ech}/2}^{F_{ech}/2} |E(f)|^2 df = |E(f)|^2 F_{ech}$$

$$|E(f)|^2 = \frac{\Delta^2}{12F_{ech}}$$

(I.23)

La puissance de bruit de quantification associée au signal dans la bande utile [-fb,fb]est :

$$Pe = \int_{-f_{h}}^{f_{b}} |E(f)|^{2} df = 2f_{b} \frac{\Delta^{2}}{12F_{ech}}$$

(I.24)

Il est donc plus avantageux d'augmenter la résolution du quantificateur. Malheureusement la diminution du pas de quantification est limitée par la technologie et l'architecture du quantificateur. On peut donc utiliser des systèmes utilisant une fréquence d'échantillonnage largement supérieure à 2.fb (fréquence de Nyquist) : c'est la technique dite de « suréchantillonnage ». Cependant, une augmentation de la fréquence d'échantillonnage pose des problèmes de consommation ou de limitation de la fréquence de commutation des interrupteurs MOS. Ces pertes ont un impact négatif sur le (SNR)<sub>0</sub> que nous noterons $\Delta_Q$ .En négligeant les effets de la quantification, le signal sera de la forme [8][17]:

$$r(nT_{e}) = \sum_{i=1}^{L} A_{i} c_{i} (nT_{e} - \tau_{i}) d_{i} (nT_{e} - \tau_{i}) \cos \left[ \left( 2\pi (f_{IF} + f_{d,i}) nT_{e} + \varphi_{i} \right) + \eta_{IF} (nT_{e}) \right]$$

(I.25)

# > Détails sur la fréquence d'échantillonnage

Si un seul ADC est utilisé par un canal RF, le signal est réel, parallèlement avec un signal complexe, et la bande du signal est limitée par la fréquence d'échantillonnage selon Nyquist  $\mathbf{fs}/\mathbf{2} >= \mathbf{Bou}$ ,  $\mathbf{f_s}$ : fréquence d'échantillonnage ;B: bande passante du signal.Les emplacements des filtres dans un récepteur affectent les performances du frontal RF. Dans

plusieurs récepteurs *GPS*, le signal est converti dans deux canaux I et Q. A partir de là les données collectées sont complexes et la fréquence *Nyquist* sera donne **fs=B**.

Choisir la fréquence d'échantillonnage se fait en prenant en considération la fréquence du code *PRN*, de manière que l'échantillonnage ne doit pas être synchronisé avec la fréquence du code C/A(1.023Mhz),car en considérant le biais d'horloge la résolution de la distance liée à cette erreur sera moins importante que si on choisit une fréquence d'échantillonnage asynchrone or une fréquence différente que le multiple de la fréquence du code *PRN*. Toutefois pour notre cas, lors de la simulation d'une acquisition le but recherché n'est pas de calculer la position du récepteur et donc on peut négliger le biais d'horloge. Le signal reçu et échantillonné s'écrit [14]:

$$r[n] = \sum_{i=1}^{L} A_{i} e_{i} [n - \frac{\tau_{i}}{T_{e}}] d_{i} \left[ n - \frac{\tau_{i}}{T_{e}} \right] \cos \left[ 2\pi \frac{(f_{IF} + f_{d,i})}{f_{e}} n + \varphi_{i} \right] + \eta_{IF}[n]$$

(I.26)

On simplifie pour un satellite :

$$r[n] = Ae_{i}[n - \tau_{0}]d_{i}\left[n - \tau_{0}\right]\cos\left[2\pi F_{D}n + \varphi\right] + \eta_{IF}[n]$$

(I.27)

Dans cette équation,  $F_D=(f_{IF}+f_{d,i})/f_e$  et  $\tau_0=\tau_r/T_e$ .  $\eta_{if}=[n]$  est un bruit Gaussien centré discrétisé à la fréquence ' $f_e$ ' de densité spectrale de puissance ' $N_0$ ' et variance  $\sigma_{If}^2=N_0B_{IF}$ .  $B_{IF}$  est la bande passante après l'étage radio fréquence.

### I.4.3.3. Bruit dans le Front End

Le bruit thermique par unité de largeur de bande d'un objet est équivalent au bruit thermique généré par une résistance de 50 ohms à une température absolue T, alors le bruit est exprimé en termes de température absolue T et devient équivalent à l'énergie thermique moyenne rayonnée à la température absolue T. La puissance du bruit thermique par unité de largeur de bande, No peut être exprimée par kT avec k désigne la constante de Boltzmann ( $k=1,38\times10-23\,$  J/K). La température T qui correspond à ce bruit thermique est appelée température de bruit [20] ( $Noise\ température$ ).

La figure de bruit est une quantité qui exprime la qualité de point de vue bruit d'un dispositif tel qu'un circuit, un système ou une liaison. La formule de FRIIS nous permettra de calculer la température effective à la sortie de l'étage RF. Le niveau de bruit, dans un système de transmission par satellite doit être extrêmement faible puisque le signal désiré est souvent assez faible. Ce niveau du bruit peut être exprimé en termes de température absolue fictive.

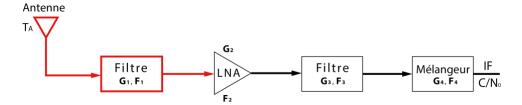

Figure I.14.a: Figure de bruit.

**Figure I.14.b** : Figure de bruit du « FRONT END » avec une digitalisation direct.

$$Teff = Ta + (F1-1) \times T + \frac{(F2-1) \times T}{G1} + \frac{(F3-1) \times T}{G1 \times G2} + \frac{(F4-1) \times T}{G1 \times G2 \times G3}$$

(I.28)

T : température ambiante ; F : figure de bruit, circuit passif : F=1/G circuit actif. La figure de bruit est spécifiée par le constructeur.

Une antenne de réception capte en plus du signal utile des ondes radio nuisibles. De surcroît, les pertes thermiques de l'antenne sont considérées comme bruit thermique, noté Ta[19]. D'après l'équation le premier composant qui suit l'antenne est soit un filtre soit un amplificateur, ainsi la deuxième architecture citée requiert que l'amplificateur soit intégré avec l'antenne. On déduit que si l'amplification est placé en 1<sup>er</sup>, la figure de bruit est faible (approximativement égale à la figure de bruit du 1<sup>er</sup> ampli). La figure de bruit qui caractérise le composant qui vient après le 1<sup>er</sup> composant sera atténué par le gain du 1<sup>er</sup> amplificateur .Toutefois, un signal avec une grande bande passante affecte l'ampli et génère ainsi des fréquences résiduelles. Avec un filtre en premier l'atténuation du signal sera plus importante et la figure du bruit du récepteur plus grande (-2 3 dB) [2] il s'agira également d'un filtre volumineux Le 1<sup>er</sup> cas est généralement établi quand le système n'est pas soumis à beaucoup d'interférences. Cela nous permettra de calculer la densité et la puissance du bruit

$$N_{o} = K \times Teff \qquad \left[\frac{w}{Hz}\right]$$

$$N_{i} = K \times Teff \times B \qquad [w]$$

(I.29)

Ni est la puissance de bruit en watts.

La température du bruit est à la température ambiante où T c 290K exprimé en dBm  $N_0$  (dBm) = -174 dBm /Hz ou  $N_0$  (dBm) = -114 dBm /MHz. Le signal est de 19 dB (-130 + 111) en dessous du bruit de fond. On prendra en compte le niveau de puissance par unité de la bande passante [dBw/Hz].

Figure I.15: Paramètres de l'étage RF.

**BER**

**Note**: La formule du facteur de bruit renseigne que le 1<sup>er</sup> élément de la cascade RF dans le résultat du facteur de bruit ce qui indique que les composantes passives qui viennent avant les éléments actifs vont avoir un effet négatif sur le facteur. Une solution est d'incorporer un amplificateur avec l'antenne, antenne qui nécessite une alimentation pour l'antenne.

**Tableau I.3** : Bilan de liaison entrée sortie de l'étage RF et SNR à l'entrée de l'acquisition.

| Paramètres             | Valeur en SI    | En dB         |

|------------------------|-----------------|---------------|

| Constante de Boltzmann | 1,38*10^-23 J/K |               |

| Température d'antenne  | 130 K           |               |

| Température            | 290 K           |               |

| F1                     | 1               |               |

| gain LNA               | 316,2           | 25            |

| F LNA                  | 1,5             | 1,9           |

| F3                     | 1,1             | 0,5           |

| F4                     | 7,9             | 9             |

| T <sub>eff</sub>       | 296,4 K         |               |

| Figure de bruit        | 1.6             | 2             |

| N0                     |                 | -203,9 dBw/Hz |

| Bande de fréquence     | 2 Mhz           |               |

| Puissance du bruit     |                 |               |

| C/N0 | 45,4 dB-Hz           |

|------|----------------------|

| SNR  | -20dB pour B = 2 Mhz |

**Remarque :** La majorité du bruit provient de l'étage radio fréquence par conséquent le choix de ce dernier est très important dans notre récepteur GPS.

### I.5. CONCLUSION