RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE

MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE

## UNIVERSITÉ DE BLIDA INSTITUT D'ÉLECTRONIQUE

MÉMOIRE DE MAGISTER

SPÉCIALITÉ: ÉLECTRONIQUE

OPTION: MICRO-ÉLECTRONIQUE

### **THEME**

# CONTRIBUTION À LA NAVIGATION DE ROBOTS MOBILES AUTONOMES

Implémentation de la stratégie sur un circuit FPGA

Présenté par : M<sup>elle</sup> Ouarda HACHOUR

Proposé par : Mr Karim ACHOUR

Soutenance devant le jury composé de :

USTB

Président

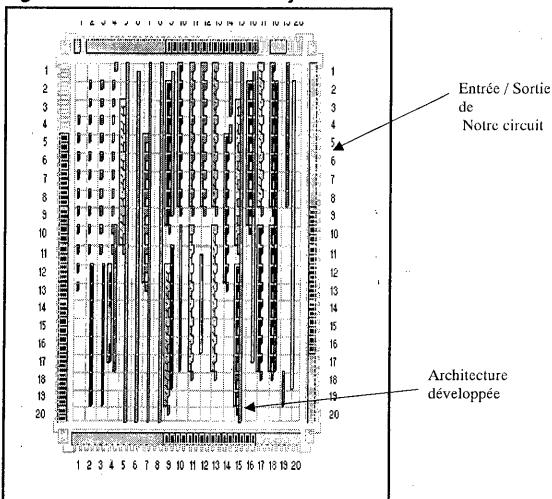

L'objectif essentiel de ce travail est l'implémentation d'une stratégie de navigation d'un robot mobile autonome dans des environnements inconnus sur un circuit intégré FPGA ( Field Programmable Gate Array). L'utilisation des techniques d'Intelligence Artificielle, de la logique floue et des algorithmes génétiques est nécessaire pour offrir un comportement intelligent aux véhicules autonomes similaire au système naturel. Cette approche doit rendre le robot capable d'accomplir ces tâches suivantes : de trouver un chemin vers sa cible et d'éviter les obstacles. Le travail est divisé en deux parties : une partie software et une partie hardware. La partie software a été développée en utilisant le langage de programmation Borland C++. Dans la partie hardware nous allons implémenter la même architecture développée en software. Afin de valider cette architecture nous avons opté pour une approche descendante basée sur la synthèse de Galileo, et comme langage de description nous avons utilisé VHDL (Very High Description Language). Nous proposons une description VHDL flexible et paramètrée qui peut être facilement adaptée à d'autres applications. La description VHDL de l'architecture est implémentée sur un circuit FPGA de la famille XC4000 de Xilinx.

The main objective of this work is the design and implementation of a FPGA (Field Programmable Gate Array) integrated circuit for a navigation approach in unknown environments. The use of techniques of Artificial Intelligent, fuzzy logic and genetic algorithms is necessary to bring the behavior of intelligent autonomous vehicle like the human. This approach must make the robot able to achieve these tasks: to make ones way towards its target, and to avoid obstacles. The work is divided in two parts: a software part and a hardware part. The software part has been developed using the Borland C++ language. In the hardware part, we implement the same architecture developed in software. In order to validate this architecture, we have opted for a top down approach based on logic synthesis and using the VHDL (Very High Description Language). We propose a flexible and parametric VHDL description, which can be easily adapted to other applications. The VHDL description of architecture is mapped into the FPGA Xilinx XC4000 family circuit.

# INTRODUCTION GENERALE

e tous les temps, l'homme n'a cessé de comprendre et de décrire la nature qui l'entoure telle qu'il l'observe et la ressent. Cette description a été traduite par les fresques, la littérature, la musique, la peinture, la sculpture et d'autres formes d'art. Pour parfaire cette description et d'en saisir le sens, l'homme a mis à contribution toutes ses facultés qu'elles soient morales, physiques où intellectuelles.

Son instinct dominateur l'a incité à vouloir maîtriser la nature afin de faciliter et d'améliorer son existence dans ce monde. En utilisant son intelligence à la recherche de moyens et de méthodes, il a voulu concevoir une machine à son image. Le premier automate connu date de l'époque pharaonique, c'est une réalisation d'un bras articulé représentant un boulanger pétrissant sa patte. Malgré toutes les difficultés et tous les obstacles rencontrés, l'être humain essaye toujours de mieux faire. Il ne veut pas que la machine imite tous ces faits et gestes seulement, mais aussi qu'elle pense et réfléchisse comme lui.

L'avènement des robots de la troisième génération capables de percevoir leur environnement et de réagir à celui-ci a fait faire un bond en avant aux théories et techniques de la perception. Parmi celles-ci, la robotique mobile présente un grand intérêt publique et pratique dans l'univers technologique. Vue l'importance cruciale donnée à ce domaine, cette description a fait actuellement l'objet d'efforts inhérent dans la plupart des pays industrialisés Les enjeux sont grands, ils sont à la fois :

- Economiques : on assiste actuellement à la naissance d'une véritable industrie des connaissances et à l'intégration des systèmes d'automatisation dans les systèmes d'informations et de production existants.

- Stratégiques : il s'agit d'exploiter au mieux les connaissances et le savoir faire , richesses souvent cruciales d'une entreprise ou d'une organisation . Les techniques de la robotique et l'Intelligence Artificielle sont aussi un moyen efficace pour maîtriser

l'information et de ce fait , augmenter la productivité et améliorer la qualité de la 4 production.

- Politiques : comme l'attestent les grands projets internationaux sur des l'attestent les grands projets projets internationaux sur des l'attestent les grands projets projets projets de l'attestent les grands projets projets de l'attestent les grands projets projet

Ceci justifie l'intérêt porté vers la conception et le développement des robots mobiles dans de nombreux laboratoires de recherches dans le monde .

Le pouvoir de faire déplacer un robot mobile d'un point source à un point but en sécurité est le point focal de toutes les recherches en robotique mobile , souvent le robot doit atteindre son objectif. Le robot autonome doit , avant tout, être capable de décider de ses actions de façon raisonnée , puis les exécuter dans un contexte réel [1]. Réagir aux événements imprévus peut conduire à modifier profondément le plan d'action établi par le planificateur , il faut donc contrôler à tout moment l'activité du robot pour assurer une bonne réactivité. En toute globalité , la navigation peut être résumée dans les réponses à ces trois questions : "ou` suis - je ? " , " ou` est-ce- que je vais ,? ", et " comment je vais atteindre mon but ? " . En outre , le mot clé de la robotique de troisième générations réside sur ce qu'on appelle l'autonomie , celle ci implique des capacités de perception de modélisation de l'environnement et de prises de décisions. Pour cela un robot est dit autonome s'il satisfait les conditions suivantes :

- Déplacement dans un environnement connu ou partiellement connu.

- L'autonomie qui s'explique par L'Intelligence et sources de puissances contenues dans un corps fermé.

- Compréhension de l'environnement qui est la reconnaissance du monde.

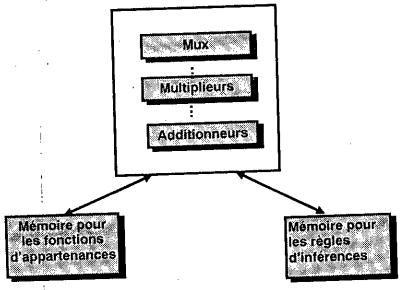

Afin d'assurer aux véhicules plus d'autonomie et plus d'intelligence avec des capacités de traitement en temps réel, l'utilisation des circuits ASICs comme les circuits FPGAs – qui est l'objectif essentiel de notre présent travail - est nécessaire pour compléter les lacunes et offrir un système robuste et rigoureux et ceci avec une rapidité accrue par rapport aux progrès de Soft- Computing basés sur les circuits à usage générale. Une nouvelle architecture s'impose alors en prise en charge des systèmes hybrides intelligents basés sur les algorithmes génétiques, la logique floue et les techniques d'Intelligence Artificielle pour la planification et le contrôle des robots mobiles. Cette méthodologie s'est alors mise en œuvre en utilisant le monde passionnant de la micro- électronique et qui a permit de dégager les meilleurs systèmes, en termes de facilité de mise en œuvre et de performances pour chaque comportement intelligent.

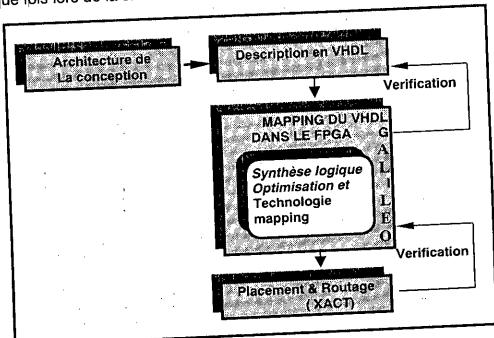

La technologie des FPGAs dédiée à l'implémentation d'une stratégie de navigation d'un robot mobile, nous a ramené à opter pour une approche basée sur une synthèse de haut niveau comme Galileo et une description hardware comme VHDL (Very High Description Language). Cet outil est le plus important pour un micro-électronicien pour qu'il puisse concevoir et réaliser un circuit intégré. Ce langage permet par son pouvoir de haut niveau de transformer un circuit modélisé en une réalisation physique du circuit. Selon les performances requises de l'application, le comportement de notre robot peut être mieux fait en hardware qu'en software avec un temps adéquat et convenable pour répondre encore plus aux exigences d'autonomie

dans des environnements parfaitement inconnus de manière similaire au système naturel et qui peut atteindre les meilleurs performances d'ordre pratique et théorique.

Notre travail s'inscrit dans le cadre d'un projet de recherche à la fois du laboratoire de Robotique et d'intelligence artificielles et du laboratoire de la micro-électronique du centre de développement des technologies avancées *CDTA* à *EL Madania*.

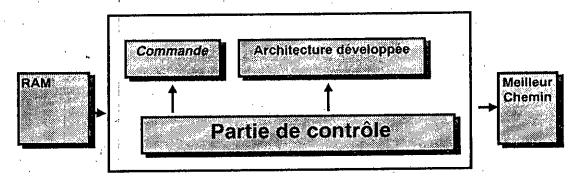

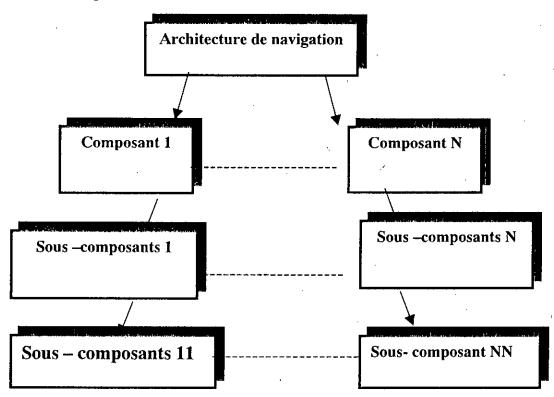

Ce projet qui s'intitule: "Contribution à la navigation de robots mobiles autonomes — implémentation de la stratégie sur un circuit FPGA-» a pour objectif de simuler un planificateur local des trajectoires pour mener le robot de la source à la destination en évitant les obstacles dans le sens "optimal". L'objectif essentiel de ce travail se focalise en l'implémentation d'une stratégie de navigation d'un robot mobile autonome sur une carte électronique dotée du circuit FPGA. La partie Software de notre conception (progiciel) a pour but l'étude de la faisabilité ce qui va être implémenté en hardware.

Pour décrire nos travaux, nous avons organisé ce mémoire en quatre (04) chapitres.

Le premier chapitre expose la navigation des robots mobiles.

Le deuxième chapitre est destiné à exploiter les performances de la logique floue et les algorithmes génétiques. Ces deux outils ont été utilisés pour optimiser et contrôler une trajectoire donnée.

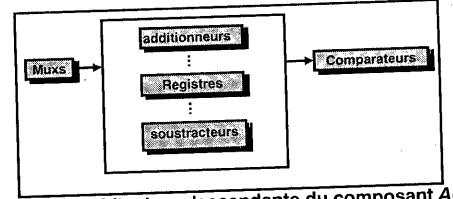

Le troisième chapitre décrit les circuits ASICs et les circuits FPGAs. Ces circuits nécessitent des connaissances de base sur cette technologie, une synthèse de haut niveau comme Galileo et un langage de description hardware comme le VHDL. Cette implémentation répond parfaitement aux exigences d'autonomies en un temps adéquat emballé par une rapidité accrue.

Le quatrième chapitre décrit l'analyse, le développement et la simulation proposée à la navigation des robots mobiles autonomes. Nous y détaillons toutes les étapes utilisées lors de la conception software et hardware. A cet effet, nous avons consacré une section pour la présentation de notre progiciel appelé AG-LF et une section pour la présentation de circuit FPGA avec une description et un traitement de la fonctionnalité. Pour chaque partie, nous présentons les résultats obtenus.

Nous terminons par une conclusion générale et par des perspectives suites à notre travail.

### Chapitre 1

# LA NAVIGATION DES ROBOTS MOBILES

## 1.1. INTRODUCTION

La robotique mobile expose un domaine qui s'étend rapidement et indéfiniment. Durant ces dernières années, supportées par l'état d'avancement de la technologie, plusieurs recherches ont été faites dans le cadre des robots mobiles autonomes articulées autour de deux axes principaux, à savoir la navigation et le guidage. On assiste également à une exploitation raisonnée de grandes bases de connaissances, ce qui constitue une des caractéristiques fondamentales de la robotique mobile qu'elle est fondée sur cette exploitation.

## 1.2. BREF HISTORIQUE

Le terme Robot est usuellement associé à la réalisation des tâches de façon automatique. Ce mot tire sa racine du bulgare robu qui signifie serviteur et qui a aussi donnée de le tchèque robota qui se traduit par travail forcé. C'est d'ailleurs par l'écrivain Karel Capek que c'est popularisé le terme du robot, nom qu'il avait donné à des petits artificiels (androïdes) évoluant dans sa pièce de théâtre Rossum's Universal Robots et qui répondaient parfaitement aux instructions de leur maître [2] Cette pièce, restée célèbre par cette invention décrivant une lutte dans la société avec les automates travailleurs « Ouvriers » [3]

En 1961, George *Devol* et *Engelberger* ont pu mettre en évidence les procédés d'inventions des robots industriels , dans le même concept , le premier robot "contrôlé par l'ordinateur" a été développé par Ernest à Mit. Et c'est vers la fin des années soixante 1960 que le concept de la robotique mobile est apparu. Pour essayer en vraie grandeur les principes développés par les chercheurs , on construit *Shakey* . C'est une réalisation d'une machine à roues , connectée à un gros

ordinateur, et qui évolue dans un univers de cubes et de pyramides de tailles et de couleurs différentes, ses missions : prendre un objet et le porter ailleurs, quelques soit sa position absolue dans la salle d'évolution, relative par rapport à d'autres objets. Ses moyens de perception : essentiellement une caméra qui lui permet d'acquérir des images de son environnement. Ses performances : une cinquantaine de minutes pour effectuer une " mission » [4].

### 1.3. DEFINITION

Il existe plusieurs définitions pour ce terme : Larousse par exemple donne une définition (robota: corvée en tchèque) c'est à dire appareil capable d'agir de façon automatique par une fonction donnée, le petit Robert l'explique par une machine à l'aspect humain capable de se mouvoir et d'agir. D'autres définitions ont lui été contribuées, parmi celles-ci on trouve « Manipulateur commandé en position, reprogammable, capable de manipuler des matériaux, des pièces, des outils et des dispositifs spécialisés, au cours de mouvement variables et programmés pour l'exécution d'une variété de tâches ».

Mais dans la conversation courante, ce terme couvre d'autres représentations , moins officielles : nous définissons aussi un robot mobile comme étant un système automoteur , disposant de moyens de traitement de l'information permettant une capacité décisionnelle suffisante de façon à pouvoir exécuter , sous contrôle humain un certain nombre de tâches précises, dans un environnement variable , non complètement connu à l'avance

### 1.4. MOYENS DE PERCEPTION

Vu la complexité de l'espace dans lequel les robots sont amenés à évoluer et vu que l'environnement de ces automates est vaste, variable et peu ou pas structuré, plusieurs dispositifs ont été mis à la contribution de la perception qui résident sur les différents senseurs [4,5]. Ces derniers permettent aux robots de comprendre la structure de l'univers de la navigation, il serait donc nécessaire de concevoir des systèmes - perception - qui permettent de mesurer et de contrôler en permanence la position par rapport aux tâches qu'elles sont demandées. Ces dernières années, l'évolution de la technologie a enrichie le matériel de perception qui peut être présenté en deux classes:

## 1.4.1. Systèmes télémétriques passifs

Ces types concernent les capteurs tactiles et les caméras qui fournissent une vue panoramique de l'environnement. La télémétrie passive fournit une description de l'environnement très détaillée mais le nombre d'informations à traiter par l'ordinateur est très important et conduit à un temps de calcul très élevé.

## 1.4.2. Systèmes télémétriques actifs

Dans ce cas les capteurs ne fournissent pas une vue panoramique de

l'environnement, nous pouvons citer à titre d'exemple les capteurs ultrasonores qui émettent des ultrasons et déterminent la distance à un obstacle par des mesures effectuées sur l'écho renvoyé par l'obstacle. Les ultrasons retournent moins d'informations à traiter mais ce moyen de perception est plus sensible aux distorsions et aux perturbations au monde extérieur.

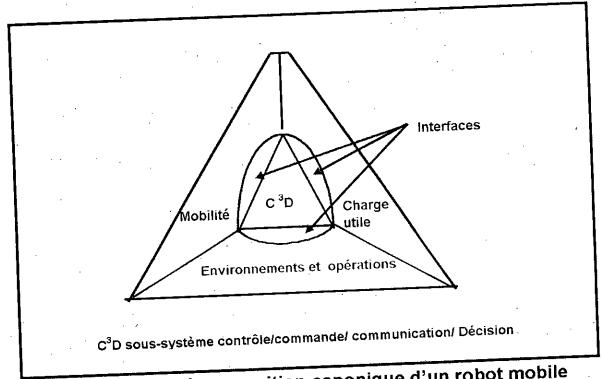

## 1.5. DECOMPOSITION CANONIQUE D'UN ROBOT MOBILE AUTONOME

A partir de la définition proposée dans le paragraphe (1.3), on peut , en premier temps, représenter un robot mobile autonome suivant le schéma de la figure 1.1. Trois sous systèmes principaux y apparaissant : le sous - système mobilité, le sous-système charge utile, le sous -système contrôle / commande / communication / décision ou C³D [4].

- Le premier associe l'ensemble des éléments nécessaires (électroniques, etc.) permettant d'assurer l'autonomie de mouvement nécessaire à l'accomplissement de la mission.

- Le second sous- système est le plus spécifique de la mission du robot. Ce peut être un outil de nettoyage (cas d'un robot nettoyeur), une caméra (avec ou sans traitement d'image) dans le cas d'un robot de surveillance, etc.

- le troisième sous- système regroupe l'ensemble des moyens d'acquisition ,de traitement et de calcul qui permettent au robot d'avoir une certaine d'autonomie décisionnelle.

### 1.5.1. Contrôle .Commande .Communication

Les fonctions du sous-système C³D sont celles qui vont qualifier une machine comme étant un robot mobile *autonome*. Il est nécessaire , dés maintenant, de bien mettre en évidence un certain nombre de notions clés relatives à certains concepts. Pour simplifier la compréhension du sujet, nous serons amenés à scinder en deux grandes parties la description du C³D : d'un côté les problèmes liés à la planification des actions, de l'autre côté, les techniques utilisées pour doter le robot de capacités de perception de l'environnement .

Figure 1.1 : décomposition canonique d'un robot mobile autonome

## 1.5.2. Problèmes de prises de décision

La commande et le contrôle des déplacements , ainsi que la perception de l'environnement du robot mobile autonome sont des éléments essentiels du système C³D. Nous allons décrire ces éléments rapidement dans ce paragraphe.

### Exemple

Supposons que nous donnions à un robot mobile qui opère des lieux (constituant le plan d'atelier ) la mission suivante : effectuer l'opération  $O_1$  sur les machines  $M_1$  de l'atelier  $A_3$ , la démarche à suivre peut se décomposer en une suite de tâches d'analyse et de prise de décisions. Celles-ci repassant dés la réception de l'ordre, et une partie d'elles vont continuer pendant toute la durée du travail s'agissant des opérations initiales , on aura l'analyse suivante

- Qu'est ce que l'opération O<sub>1</sub>? en particulier, ya t- il besoin pour l'accomplir d'un objet spécial? ou` se trouve la machine M<sub>1</sub>?

- Constations de l'état du robot : position, état de charge des batteries, matériel disponible à bord, etc.

- Génération d'un plan d'action d'abord grossier (aller chercher l'objet manquant, puis rejoindre M<sub>1</sub> et effectuer le travail requis).

Cette génération de plans est relativement classique, et pendant toute la durée de la mission, le robot devra contrôler l'exécution de ce plan, étape par étape. Si le robot va rencontrer un obstacle inattendu il est nécessaire donc de faire une modification locale de trajectoire pour le contourner, autrement dit, dans ce cas il

va falloir *remonter* dans le raisonnement jusqu'au niveau de l'ordonnancement des tâches pour rejoindre un problème.

Il est donc nécessaire de doter le robot d'un mécanisme décisionnel dit contrôleur d'exécution dont la fonction va être , à partir des informations recueillies par les différents capteurs ( d'environnement mais aussi proprioceptifs) , de choisir à quel niveau doit être réévaluée la mission. L'écueil principal de réalisation réside dans le caractère en temps réel imposé par les conditions de travail de la machine. Il pose avant tout un problème d'architecture

## 1.6. ROBOTIQUE ET INTELLIGENCE ARTIFICIELLE

Le vaste champ de la robotique mobile englobe l'ensemble des activités d'automatisation de tâches, notamment dans l'industrie (fabrication, manutention, réparation, etc.). Une partie des robots existants (par exemple les robots soudeurs ou peintres sur une chaîne de montage) se contentent de répéter indéfiniment une séquence d'opérations et ne possèdent donc aucune intelligence. En revanche, les nouvelles générations de robots sont de plus en plus dotées de capacités « intelligentes »de perception de leur environnement (notamment par la vision) et de planification de leur activité (génération d'une stratégie ou d'un plan d'action pour mener à bien une tâche). Ainsi, L'intelligence Artificielle IA joue un rôle croissant dans la robotique qui constitue une composante majeure de l'industrie de demain.

L'IA est une approche plus récente et très prometteuse qui tente de dépasser certaines de leurs insuffisances. Actuellement, plusieurs équipes de recherches développant des projets inhérents dans le vaste champ de la robotique constituent l'ossature d'un bon potentiel de niveau international. Les interactions entre les experts d'Intelligences Artificielle et de la robotique mobile dont le temps est grand illustre que la plupart des problèmes au niveau de l'automatisation et d'autres tâches de robotique mobile sont résou en faisant appel à l'Al.

Cette illustration peut être vue à priori, comme la structure d'un plan pour résoudre le problème donné. Les systèmes développés aujourd'hui montrent que les recherches scientifiques en robotique mobile font appel de plus en plus à l'IA [6].

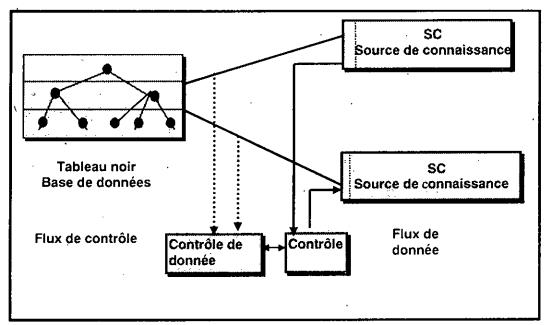

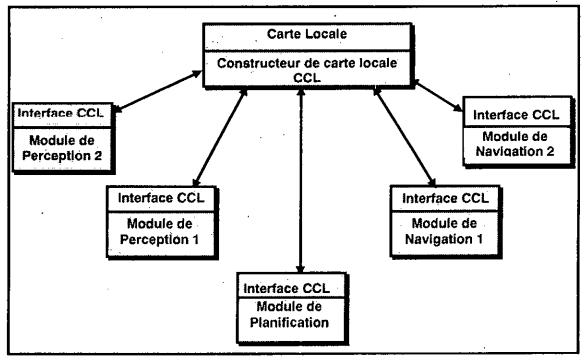

Les architectures qui comportent une fonction de planification en robotique mobile sont issues des techniques de l'Intelligence Artificielle du type tableau noir / tableau blanc, ou` le modèle de tableau noir propose un schéma pour organiser les domaines de connaissances et les étapes du raisonnement conduisant à la construction incrémentale de la solution au problème posé, ce modèle représenté à la figure 1.2 est composé de trois éléments majeurs [6,7,8]:

- Les sources de connaissances qui sont indépendantes utilisent exclusivement la base de données centrale.

- La base de données centrale ou tableau noir, mémorise, à chaque instant l'état courant de la résolution du problème. Les éléments de solutions sont mis à jour par les sources de connaissances.

- Le système de contrôle qui gère l'activité des sources de connaissances.

## RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE

MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE

## UNIVERSITÉ DE BLIDA INSTITUT D'ÉLECTRONIQUE

MÉMOIRE DE MAGISTER

SPÉCIALITÉ: ÉLECTRONIQUE

OPTION: MICRO-ÉLECTRONIQUE

### THEME

# CONTRIBUTION À LA NAVIGATION DE ROBOTS MOBILES AUTONOMES

Implémentation de la stratégie sur un circuit FPGA

Présenté par : M<sup>elle</sup> Ouarda HACHOUR

Proposé par : Mr Karim ACHOUR

## Soutenance devant le jury composé de :

| M <sup>r</sup> K.FERDJANI   | Maître de conférence | USTB | Président      |

|-----------------------------|----------------------|------|----------------|

| Mr B.BOUZOUIA               | Maître de recherche  | CDTA | Examinateur    |

| M <sup>r</sup> N.AMMOUR     | Chargé de cours      | USTB | Examinateur    |

| M <sup>r</sup> M.HADJ RABAH | Chargé de cours      | USTB | Co- rapporteur |

Université de Blida, 2001

En 1983, *ELFES* propose une architecture décisionnelle sur le robot de type tableau noir pour le contrôle du robot *CMU ROVER*. Un ensemble de modules experts communiquant par échange de message via un tableau noir pour exécuter une mission sous la direction d'un plan de contrôle .

Dans la figure 1.3 : on démontre une autre recherche dévouée par l'équipe de *C.THORPE*, cette équipe développa en 1986, un prototype *NAVLAB* capable d'effectuer le suivi de route. L'architecture est de type de tableau blanc, pour se démarquer du modèle tableau noir, cette architecture permet un accès asynchrone à la base de donnée pour y déposer ou en retirer des informations.

Figure 1.2 : Modèle de tableau noir

Figure 1.3 : Structure du robot NAVLAB

## 1.7. NAVIGATION DES ROBOTS MOBILES

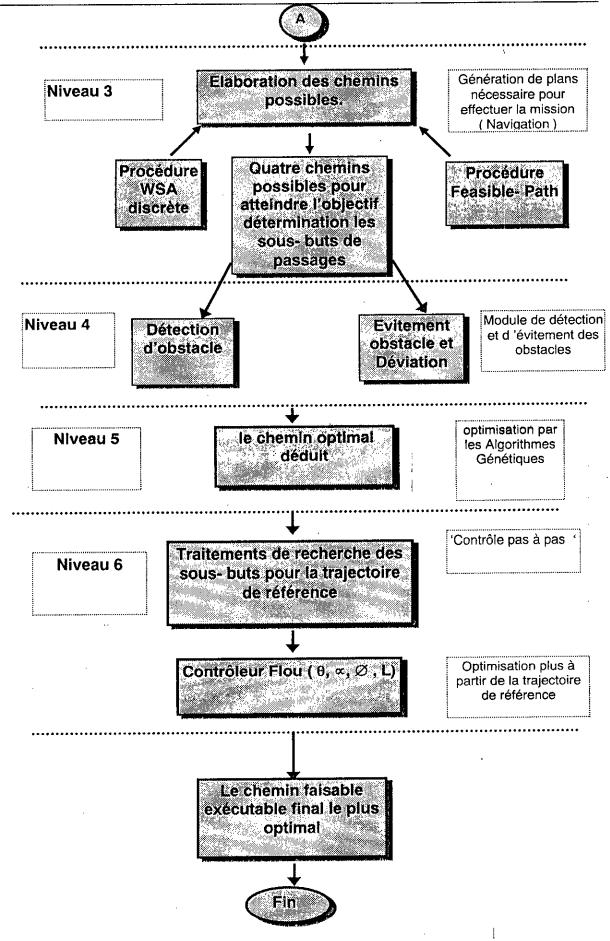

Le robot mobile doit atteindre son objectif en sécurité malgré le manque d'information sur son environnement. Cependant la navigation autonome représente l'un des grands objectifs de la robotique mobile. La navigation est l'art de contrôler l'évolution d'un robot mobile au moment ou il traverse un environnement (terre, mer ou air). Sans risques de collisions, la destination doit être atteinte à n'importe quel système de navigation, ceci implique la prise en charge de trois missions importantes à savoir: le planificateur- la cartographie- le pilotage. L'objectif de la navigation est de générer un chemin qui relie une configuration initiale à une configuration finale du robot en lui évitant toutes les collisions avec les imprévus de l'environnement. Dans ce domaine, plusieurs recherches ont été amenées pour modéliser l'environnement.

La modélisation de l'environnement est une façon de structurer l'espace d'évolution du robot. Celle-ci s'effectuera à partir des informations fournies par les moyens de perception (ultrasons, caméra, etc.). Un environnement peut être modélisé selon deux concepts:

- Le modèle de grille.

- Le modèle polygonale.

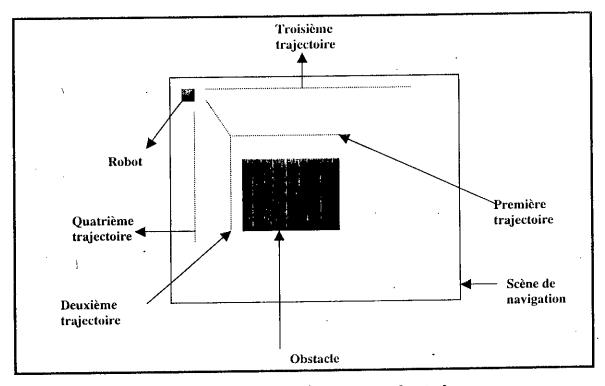

### 1.7.1. Modèle de grille

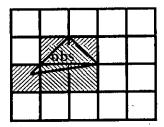

Une grille représente l'espace libre et l'espace occupé de l'environnement. Les cases de la grille résultent de l'intersection des lignes horizontales et des lignes verticales (cases carrées) et parfois diagonales (cases losanges).

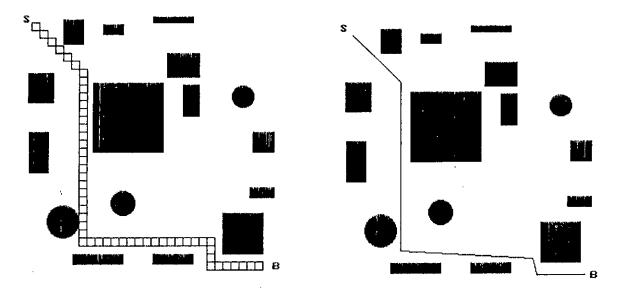

Cependant, la case de cette grille est représentée par une certaine étiquette indiquant sa fonction « libre ou occupée ». L'avantage majeur c'est qu'elle est facile à mettre en œuvre mais l'inconvénient elle occupe beaucoup d'espace mémoire. Voici un exemple de modèle de grille à cellules carrées :

Figure 1.4 : modèle de grilles à cellules carrées

Le chemin de Ci à Cf ne peut être trouvé par le système dans la figure 1.5, cette dernière démontre le problème d'utilisation de ce modèle; en effet, le chemin et le marquage successif sont difficiles à se retrouver lorsque une grille est à moitié pleine (voir la figure 1.5).

Figure 1.5: Exemple de décomposition occultant un chemin faisable

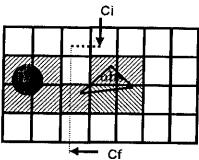

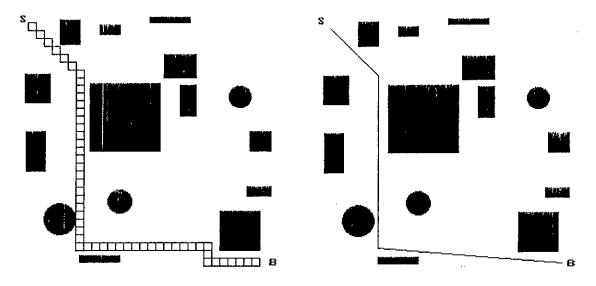

### 1.7.2. Modèle polygonale

L'espace libre du robot est divisé sous formes de polygones obtenus en reliant les sommets des obstacles aux autres sommets qui leur sont visibles, ensuite il y aura un graphe de connexité associé au modèle ou` les nœuds sont les cellules, et les arrêtes le lien entre les cellules adjacentes. Dans ce cas, un obstacle est alors représenté par les coordonnées de ces sommets dans le repère orthonomé. Voici un exemple :

Figure 1.6 : Exemple de décomposition en polygones

## 1.8. PLANIFICATION DE LA TRAJECTOIRE

On définit la planification de trajectoire comme étant la possibilité de faire évoluer un robot d'une configuration initiale à une configuration finale, cela suivant un chemin bien approprié en évitant tous les risques de collision avec d'autres corps (obstacles susceptibles de se mouvoir sur son chemin) [9]. Cependant, on assiste à trois catégories de méthodes de générations de trajectoire à savoir :

- Planificateur global.

- Planificateur local.

- Planificateur mixte.

## 1.8.1. Planificateur global (approche statique)

Le planificateur global est destiné à un environnement parfaitement connu. Dans ce cadre de planification, plusieurs approches ont été développées pour

planifier une trajectoire d'un robot mobile autonome, nous pouvons citer à titre d'exemple la méthode des grilles homogènes proposée par monsieur *LEE*, le modèle polygonal proposé par monsieur *LOZANO-PEREZ*, la modélisation polygonale proposée par monsieur *BROOKS* et d'autres méthodes qui ont été développées dans le sens de trouver une trajectoire dans un environnement connu.

### 1.8.2. Planificateur local (Approche dynamique)

A l'opposé des méthodes globales que nous avons introduit précédemment, les techniques locales n'utilisent pas de modèle complet de l'espace libre. Elles sont sans mémoire, et ne prennent en compte à un instant donné que l'environnement proche du mobile pour modifier une trajectoire de consignes. Ce type de navigation explique qu'un dispositif de perception est indispensable car on considère que le robot évolue dans un environnement qui lui totalement inconnu. Elle est appelée approche locale du faite qu'une seule information partielle (locale) sur l'environnement peut engendrer des incréments de déplacement du robot mobile. Ainsi, les temps de réponses sont nettement améliorés, ce qui permet l'utilisation de telles approches dans des environnements dynamiques (inconnus par le robot à priori).

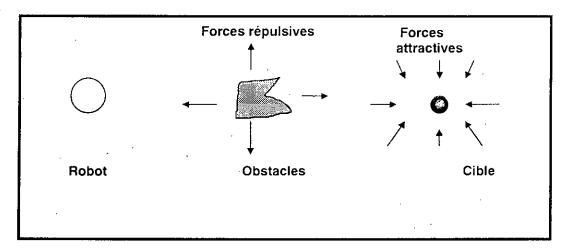

Ces méthodes de planification sont attrayantes par leur simplicité. Bien sûr, elles présentent le défaut de ne pas offrir la garantie d'arriver à l'objectif, le robot peut se trouver bloqué. Parmi les méthodes locales existantes, on choisit d'étudier l'approche la plus connue: *méthode des potentiels* développée par *OUSSAMA KHATIB*. Le principe de cette méthode consiste à introduire des forces s'exerçant à distance sur le robot, la cible exerce alors une force attractive et les obstacles exerçant une force répulsive (voir la figure 1.7).

Figure 1.7 : Approche du champs de potentiel Artificiel

### 1.8.3 Planificateur mixte

Un couplage des méthodes locales avec les méthodes globales simplifiées, permet d'obtenir des solutions avec de bonnes garanties de terminaison. Ce type de planification revient à l'utilisation conjointe des méthodes globales et locales. Au niveau globale, on n'utilise pas de description géométrique des obstacles, mais seulement des poids dépendants de la probabilité de succès de la méthode locale à

déplacer le robot entre deux régions connexes.

#### Remarque

Les approches globales (statique : grille, polygonale ) prennent un espace mémoire considérable, ainsi le temps d'exécution ne permet pas de concevoir un système intelligent pour la navigation. Par contre les approches locales (dynamiques) présentent certains avantages :

- Traitement en temps réel:

- Perspective de l'autonomie.

- Présentation des systèmes cognitifs et intelligents.

Les approches locales (classiques) ont été exploitées pour comprendre le fonctionnement du cerveau de l'être humain et de cela réputé intelligent un raisonnement logique pour que le robot peut se mouvoir, on assiste actuellement à l'introduction de la logique floue et les réseaux de neurones pour réaliser des systèmes anthropomorphes.

Dans ce qui suit, nous présentons notre conception de base pour développer notre approche, notre travail est consacré à la conception d'un planificateur local, grâce auquel on génère des trajectoires de références. Nous présentons d'abord la méthode de modélisation choisie pour notre environnement, ainsi que les étapes suivies pour parvenir à la construction du graphe de recherche. Ensuite, nous terminerons par l'analyse de l'environnement.

## 1.9. PROBLEMATIQUE DE NAVIGUER INTELLIGEMMENT DANS UN ENVIRONNEMENT INCONNU

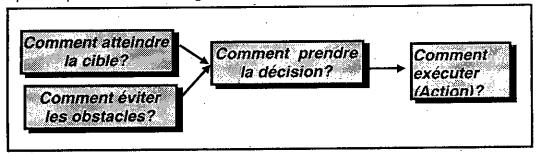

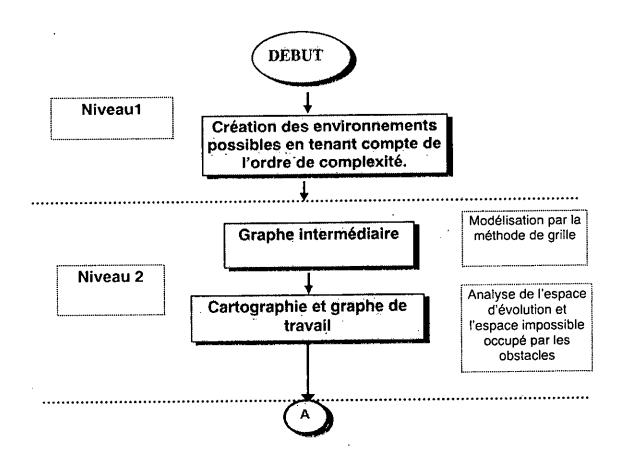

Les problèmes que nous avons rencontré lors de la conception et qui ont été résolus pour répondre à une navigation donnée sont décrits dans la figure suivante :

Figure 1.8 : Architecture globale de la problématique d'une navigation intelligente

Selon cette figure nous constatons que notre architecture peut répondre aux problèmes suivants:

• **Problème 1**: Ce problème consiste à donner un certain comportement intelligent, il faut donc trouver un moyen pour rejoindre la cible. Dans notre cas, nous allons élaborer tous les chemins possibles pour atteindre l'objectif en analysant la zone de sécurité du passage du robot (traiter pixel par pixel jusqu'à atteindre l'objectif).

- Problème 2 : Les obstacles sont parsemés sans connaissance au préalable. Il faut donc trouver un moyen pour les détecter et les éviter par la suite. La richesse du langage de programmation (Borland C++) et ses clefs graphiques peuvent nous aider à résoudre ce problème. Une couleur différente par rapport à celle permise nous informe qu'il y a un problème (obstacle) donc il faut l'éviter par un contournement et une modification de la trajectoire. Il faut tester la valeur renvoyée (l'intensité lumineuse) de chaque pixel.

- Problème 3 : Ce stade d'inquiétude pour le système mobile ne cesse de donner un certain raisonnement (calcul, etc.) pour prendre une décision logique et pertinente. Après les deux niveaux de tactique cités ci dessus, le problème de prise de décision exploite les résultats estimés avant de décider comment se diriger vers la cible. Ce comportement permet à notre robot de raisonner, à partir de ces résultats, et de décider de l'action appropriée lui permettant à la fois de se diriger vers sa cible et d'éviter les éventuels obstacles rencontrés.

- **Problème 4**: Le véhicule intelligent est capable de prendre cette décision par exécution de l'action décidée par l'étage précédent. Donc ça ne cesse de demander aux moteurs du véhicule d'exécuter ces actions.

## 1.10. CHOIX DE LA METHODE DE MODELISATION

Vue l'importance cruciale de la modélisation de l'environnement, il était nécessaire de choisir une bonne méthode de représentation qui tienne compte de toute les contraintes et critères imposés, et essentiellement de :

- La complexité de l'espace d'évolution du robot.

- La nature de la tache que doit accomplir le robot.

- Les conditions liées du robot.

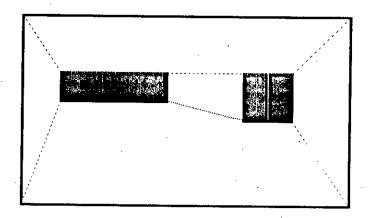

La modélisation de l'environnement est une façon de structurer l'espace d'évolution du robot, celle-ci s'effectuera grâce aux moyens de perception, dans notre cas, nous avons utilisé une caméra ( en plus les capteurs ultrasoniques embarqués avec le robot ). Ce moyen de perception peut nous fournir toutes les informations nécessaires ( vue panoramique avec le moindre détail ) sur l'environnement pour définir bien la cartographie de travail ( qui est important pour nous du moment que l'environnement est parfaitement inconnu ). En outre, nous tenons à préciser que les capteurs ultrasoniques limitent la cartographie par leur inconvénients. Une fois que la cartographie a été bien déterminée nous allons la décomposer en trois niveaux à savoir :

### a. Niveau géométrique

Ce niveau correspond à la carte des lieux dans laquelle les objets sont représentés par leurs projections au sol. La surface du plan de la scène est assimilée à une surface plane idéale ou' rien ne fait voir une hauteur ou un paramètre d'épaisseur d'un objet quelconque [10].

### b. Niveau topologique

Ce stade constitue en la décomposition du modèle géométrique en zones libres et zones occupées, et le développement d'une structure qui définit la relation d'accessibilité entre les zones libres. Dans notre cas, du moment que l'environnement est parfaitement inconnu, il était nécessaire d'utiliser les techniques du graphisme du langage Borland C++ pour bien situer et étudier le problème, pour définir les circonstances lors de la navigation et les cas possibles qui peuvent avoir lieu.

### c. Niveau sémantique

Il attribut à chaque élément (ou zone) du modèle topologique une étiquette ou un label représentant sa fonction. A ce stade de traitement, nous affectons à chaque case de la cartographie la probabilité suivante :

$$P: \begin{cases} 1: Si \ la \ zone \ est \ libre. \\ 0: Sinon. \end{cases}$$

## 1.10.1. Principe du modèle de grille

Pour réaliser notre projet, nous nous sommes inspirés du modèle de grilles pour représenter l'espace libre et l'espace occupé de l'environnement et qui était bien convenable dans notre cas. Les cases de la grille se résultent de l'intersection parallèle des lignes horizontales avec des lignes verticales qui peuvent nous offrir des cases carrés (grilles homogènes) avec la détermination des zones de sécurité et des zones dangereuses. Le niveau sémantique pourra bien apprécier son rôle ici après avoir affecté à chaque case un label, nous nous retrouvons avec des distributions de probabilités ou` la plus grande correspond bien à un état apprécié (libre ou occupé).

Ces grilles homogènes présentent un certain avantage majeur : c'est qu'elles peuvent trouver un marquage successif possible dans un environnement inconnu (chemin liant la source à la cible), mais le problème qui se pose lorsqu'une grille à moitié pleine (c'est à dire en réalité : elle est occupée par un obstacle) fait partie d'un chemin faisable exécutable comment peut-on remédier à ce problème? Cette situation est la plus délicate dans l'étude et la conception, il a fallu bien étudier et tester le cas ou` une grille à moitié pleine fait partie d'un ensemble de sous - buts qui peuvent nous fournir un chemin faisable exécutable afin que le robot peut passer sans crainte ou risque de collisions. Pour cela nous avons déposé la condition suivante : si le robot peut passer en tenant compte de son encombrement, alors on peut prendre cette case comme étant une case accessible , sinon, elle sera inaccessible.

## 1.10.2. Planificateur local Appliqué à l'approche

Notre étude est basée sur la conception d'un planificateur local ( notre environnement est parfaitement inconnu sauf les coordonnées de l'objectif et de la source), pour présenter une vraie tâche intelligente assistée par un ordinateur. Pour cela nous avons intégré un tel planificateur. Cette assistance intelligente est fondée sur les techniques d'Intelligence Artificielle IA qui est en osmose avec la robotique

mobile, d'après les relevés requises de notre travail, nous avons constaté que ces deux disciplines complémentaires et étroitement imbriquées concourent à doter des automates de facultés simulant celles de l'être humain et qui sont difficile à séparer nettement.

Le modèle choisi montre ainsi que l'IA joue un rôle croissant dans la robotique et qui constitue une composante majeure pour prendre une décision sur le chemin à choisir.

## 1.10.2.1. Approche développée

Notre architecture s'inspire du modèle possédant une fonction de planification réactive, ici le mécanisme de planification génère les trajectoires et contrôle leurs exécutions. Ces trajectoires peuvent être modifiées si le robot rencontre un obstacle imprévu ou un problème quelconque. Par les moyens de perception, le robot mobile autonome mesure des distances, des intervalles temporaires et effectue des calculs ainsi que des tests nécessaires. A cet effet, on effectue une génération de plan d'action un petit peu grossière ( passer par le nord de l'obstacle, passer par ce coté gauche ,etc.).

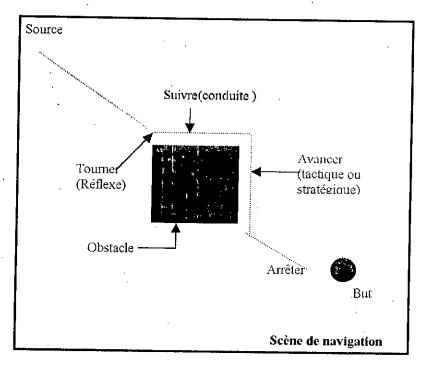

## 1.10.2.2. Génération de plan

Pendant toute la durée de la mission, le robot devra "contrôler l'exécution " de ce plan étape par étape. Si le robot va rencontrer un obstacle inattendu, la modification locale de trajectoire est donc nécessaire pour le contourner, autrement dit, dans ce cas il va falloir "remonter " dans le raisonnement jusqu'au niveau de l'ordonnancement des tâches pour résoudre le problème. La difficulté clé est donc la détection du niveau auquel peuvent être réglées de telles situations: réflexe, conduite, tactique ou stratégique (voir la figure 1.9).

- Réflexe: cette technique correspond à diminuer la vitesse si un obstacle est détecté dans la zone de sécurité du robot (un virage ou lorsque le robot est prés de la cible).

- Conduite: celle ci est résolue par une modification locale de la trajectoire, cela se traduit par un contournement d'obstacles lors d'un cas imprévu.

- Tactique ou stratégique : un nouveau calcul de chemin et de trajectoire, la trajectoire est changée, donc il est nécessaire de faire un autre calcul et un autre test possible pour une nouvelle mission .

Pour la planification et l'exécution des trajectoires nous avons élaboré :

- Planificateur ( planificateur global de trajectoires): nous avons élaboré tous les chemins possibles après un certain traitement pour atteindre l'objectif (nous avons élaboré quatre chemins possibles). Ce traitement se démarque par les sous- buts de passage du véhicule intelligent nécessaires afin de tracer et de planifier toutes les trajectoires possibles pour atteindre l'objectif, ensuite, il faut bien étudier le cas le plus favorable ( celui-ci est le rôle du second planificateur).

- Navigateur ( planificateur local de trajectoires) : celui ci utilise le plan d'action

du planificateur global en prévoyant une routine encore plus simple grâce à la combinaison hybride des algorithmes génétiques et la logique floue( que nous allons exposer dans le deuxième chapitre) en délivrant ainsi une trajectoire plus en accord et plus optimale.

Pilote: Si on veut exécuter la trajectoire finale issue de les deux étages précédents, ça ne cesse de demander au pilote (moteurs d'actions) de naviguer sans crainte ou risque de collisions après avoir bien spécifier, traiter et planifier le chemin à poursuivre. Il se traduit donc par l'exécution de cette trajectoire finale obtenue après un certain temps de calculs mené par les deux planificateurs décrits ci dessus.

## 1.10.2.3. Architecture hiérarchisée

La planification de la trajectoire utilisée pour développer notre progiciel est décomposée comme suit :

## Technique du tableau noir

La représentation du trajet du robot est illustrée sous forme d'un ruban, ce dernier est découpé en des segments qui sont décrits séquentiellement. Ces segments offrent un certain comportement important pour notre véhicule issu du principe de la technique de tableau noir. Le choix de cette technique est du son opportunité pertinente dans notre conception. En effet, le comportement adéquat offert par la technique du tableau noir " *Blackboard* » nous a été très intéressant d'offrir un comportement réactif intelligent à notre automate (voir la figure 1.9).

Lors du développement de notre architecture, nous avons remarqué un certain nombre de modules de travail constituant la base comme : percevoir ( vision), tourner (modification locale ), suivre ( avancer tous droit suivant la nouvelle trajectoire), avancer (le nouveau calcul du trajectoire) et arrêter ( l'arrivée au but ) qui font appel à cette technique pour offrir un contrôle robuste. Ces modules constituent les sources de connaissances indépendantes de notre tableau noir, le rôle est donc comment définir chaque événement correspond à ces modules et comment relier entre eux pour construire la base de données qui donne à la fin l'allure du chemin final exécutable.

Ces modules peuvent échanger des informations en les transmettant vers la base de donnée centrale ( celle ci mémorise tous les résultats possibles concernant un raisonnement bien approprié).

Pour cela, il était nécessaire donc de baptiser la navigation de notre robot sur un concept hiérarchique centralisé en utilisant la technique du tableau noir. Cette technique offre un comportement important dans une situation dramatique et peut rendre notre automate apte de naviguer sans crainte ou risque de collisions. Les résultats obtenus montrent que la technique du tableau noir est bien convenable pour donner une vraie autonomie.

Figure 1.9 : un exemple de l'architecture développée

## 1.11. CONCLUSION

Le concept de la robotique mobile est en osmose avec *l'IA* et la perception (vision). Ces domaines complémentaires et étroitement imbriqués sont difficiles à séparer nettement. Ainsi que la composante de planification est donc indispensable dans la structure d'un robot mobile, à associer à la réactivité.

La modélisation de l'environnement est une façon de structurer l'espace d'évolution, une étape inhérente avant de tout traitement. Deux composantes majeures qui contribuent encore plus à la navigation : le taux de connaissance de l'environnement avant la mission, et le type de capteurs utilisés pour la détection des situations topologiques et imprévues.

# Dédicaces

mes très d'ère parents, l'univers d'affection et d'arrour, qui ne cessent de me guetter par ses divins sacrifices aux pèlerirs qui dévorent tout un vanneur, qui m'ont toujours aidée durant toute ma vie et qui m'ont encouragée pendant mes années d'études, suntout en ces derniers moments. Pour leur bonté, leur comprébension et leur tendresse, qui m'ont éclairée dans l'ordre à la lurière de leur yeux qui d'erdrent sans cesse de me voir comme je suis aujourd'hui, je leur dédie ce mémoire.

À mes grands-parents qui m'ont toujours aimée et soutenue depuis mon enfance.

À tous les membres de ma famille, avec qui je suis heureuse, qui m'ont toujours ouverte les horizors de cette vie et qui m'ont aidée à tracer et parcourir le chemin. Je les remercie de tout mon cour pour leur tendresse, leur aide, airsi que leur haute bienveillance envers moi. Ils n'ont cessé de me chercher un avenir vivifiant, et avec qui j'ai passé les plus belles années de mu vie.

À mon fière Faouzi et mu sour Soubila, aux qui j'ai partagé le destin, qui nous a préservé dans la vie de ce monde où nous avors reçu le désir de la perspective purifié par la volonté de Dieu.

Je dédie ce mémoire à mes cousines Wassila et Rosa, à qui je leur offre les perles de la pluie et je leur dit : il faut hair le feu des anciers volcars, avoir la peau d'une bonne foie et creuser la terre jusqu'à prés de la tombe et de ne l'arroser jamais avec les larmes pacifiques car ça coûte d'er de parsemer les graines avec les souvenirs fleurissants pour cueillir les plus beaux souvires derrière la gloire de la paie.

À mes meilleures arnies Fouzia et sa fille Nawel, Safia, Nassima Chahra et Dahbia, aux qui j'ai goûté la bonne et la mauraise invitation de ce monde. Nous avors reçu ensemble les choix et les joies de l'aube et de la nuit, que nous avors sernés dans le jardin du silence, et on les a offerts au maudit oxéans qui garde les otages de la vie morte.

À tous œux qui ont versé dans le palais de l'indigent une portion des biens que le ciel les a départis aux flammes de leur splendeur, qui ont le vait de culte pratique agitée en harmonie pour guetter la prédication pour devenir difficile, voire dangereux pour remédier aux defs de diaments.

À tous œux qui ont examiné la bonne, l'agréable et la parfaite de la cérémonie qui ne prosterneront point devant l'image taillée et qui ne serviront loin de sa figure inspirée.

À œux qui portent les preuves de sagesse visibles promulguées pour non crainte salutaire rebellée contre la volonté propulsée.

### Chapitre 2

## PERFORMANCES DES ALGORITHMES GENETIQUES ET LA LOGIQUE FLOUE

## A. ALGORITHMES GENETIQUES

### A.1 INTRODUCTION

Les algorithmes génétiques AGs ont été développés par JHON HOLLAND, avec ses collègues et étudiants en 1975, à l'université de MICHIGAN. Leurs recherches avaient deux objectifs principaux :

- Mettre en évidence et expliquer rigoureusement les processus d'adaptations de systèmes naturels.

- Concevoir des systèmes artificiels (en l'occurrence des logiciels) qui possèdent les propriétés importantes des systèmes naturels.

Ce statut de recherche constitue le point focale de toute les conceptions dans ces dernières années et qui a été introduit comme une méthode robuste de recherche et d'optimisation pour divers problèmes.

Les AGs génèrent une séquence de population par l'usage d'un mécanisme de sélection, et utilise le crossover et la mutation comme des mécanismes de recherches. En revanche , les systèmes naturels sont robustes, efficaces et performants car ils s'adaptent à une large variété d'environnement. En reproduisant sous forme artificielle le principe naturel de l'algorithme de sélection de la meilleure adaptation, nous espérons atteindre la même polyvalence. Dans les faits, les AGs ont fait preuves de leur capacités dans de nombreuses études théoriques et expérimentales. Les différences séparant les AGs des techniques d'optimisation conventionnelles sont :

La manipulation directe d'une population, et non d'un point unique.

- L'exploitation au moyen d'une population, et non d'un point unique.

- L'exploitation aveugle à partir uniquement des valeurs de la fonction.

La recherche sur les AGs a pour souci principal l'amélioration de la robustesse [11], l'équilibre entre la performance et le coût nécessaire à la survie dans des environnements nombreux et différents.

### A.2 DEFINITION

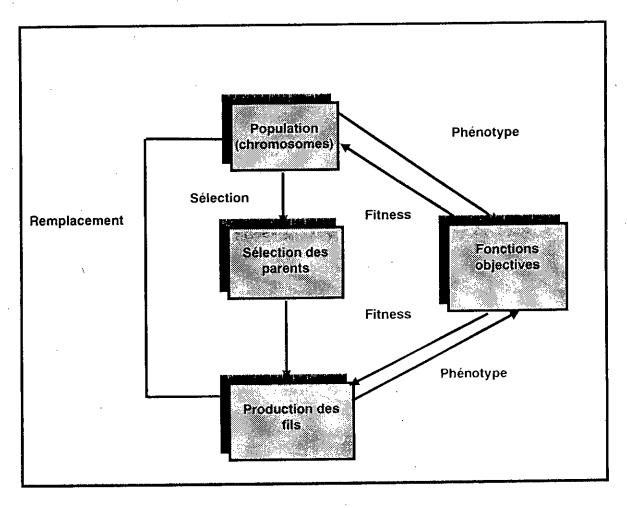

On définit les AGs comme des algorithmes d'exploration fondés sur les mécanismes de la sélection naturelle et de la génétique de GOLDBERG. Ils utilisent à la fois les principes de la survie des structures les mieux adaptés, et les échanges d'information pseudo- aléatoires. A chaque génération, un nouvel ensemble de création artificielles (des chaînes de caractères) est crée en utilisant des parties des meilleurs éléments de la génération précédente, ainsi que les parties innovatrices à l'occasion. Pour un problème quelconque ( en général un problème d'optimisation), les solutions vont être codées sous forme de chaînes de caractères appelés chromosomes, les caractères étant gènes. L'algorithme consiste en trois opérations : sélection, opération génétique et remplacement.

Le cycle typique d'un algorithme génétique est montré dans la figure 2.1. Une population comprend un ensemble de chromosomes qui se présentent comme des solutions candidats au problème [12]. Initialement, un ensemble d'individus appelé population initiale, est généré de façon aléatoire. Les valeurs d'adéquation de tout les chromosomes sont calculées par une fonction objective dans une forme décodée (phénotype). Chaque individu représente une solution potentielle. Une première phase de "sélection" sert à établir une liste de paires d'individus. Une phase dite de reproduction de la population est ensuite effectuée : elle consiste à appliquer des opérateurs dits génétiques sur les paires d'individus pour engendrer de nouveau individus. La reproduction a pour but de faire évoluer la population en y propageant les caractéristiques des individus, les meilleurs étant, suivant la métaphore évolutionniste, les plus adaptés à leur environnement.

Une taille constante de la population étant requise, une phase de "remplacement" est effectuée. Elle consiste à remplacer les plus mauvais individus de la population courante par les meilleurs produits. La taille constante de la population induit un phénomène de compétition entre les individus. Le cycle génétique est réitéré sur la nouvelle population jusqu'à un certain critère d'arrêt.

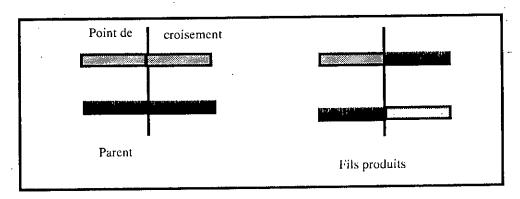

## A.3. LE CROISEMENT " CROSSOVER "

C'est un opérateur de recombinaison de deux chromosomes parents pour produire des chromosomes fils ayant les meilleurs particularités des parents. Les utilisateurs des AGs considèrent que l'opérateur crossover est le facteur qui distingue des AGs à d'autres algorithmes d'optimisations [13]. Il existe plusieurs opérations de croisement à savoir : le croisement multi- point et le croisement uni point . Voici un exemple d'un crossover en un seul point proposé dans la figure 2.2. L'opération s'effectue en coupant une paire de chromosomes de la population en un point même choisi aléatoirement et produit deux nouveaux chromosomes en échangeant les parties coupées aux mêmes endroits dans les deux chromosomes. Le croisement est inspiré du procédé biologique par la

combinaison de gènes de deux parents, il travaille par couple d'individus en coupant en un ou plusieurs points.

Figure 2.1 : Cycle d'un algorithme génétique

Figure 2.2 : exemple de crossover en un point

### A.4. SELECTION

Le principe consiste de sélectionner au hasard des individus de la population sur la base de leur fonction d'adéquation [14].

Les principales difficultés d'emploi des AGs sont liées aux problèmes suivants

- 1. Trouver un moyen efficace pour modéliser le problème (au sens des AGs) d'une façon efficace et générique

- 2. Définir une fonction d'aptitude mesurant le meilleur coût à partir d'un individu.

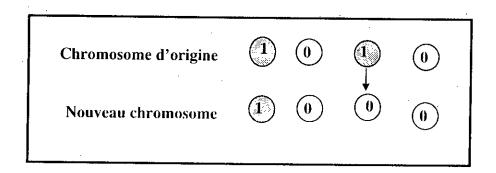

### A.5. MUTATION

La méthode de mutation des bits utilise une chaîne binaire aléatoire de taille égale au chromosome parent. A chaque position , les bits seront changés. Voici un exemple d'une mutation au troisième bit :

Figure 2 .3 : Exemple de mutation au troisième bit

## A.6. FONCTION D'ADEQUATION "FITNESS"

Le rôle des fonctions objectives est celui d'optimisation, elles fournissent le mécanisme d'évaluation pour chaque caractère [14]. Sa rangée de valeurs varie selon les domaines des variables d'un problème posé. Cette fonction permet de donner une évaluation de la chaîne de population.

De cela on peut résumer que :

- La structure des AGs prévoit un outil pour optimiser la topologie ou la structure en parallèle avec les paramètres des solutions pour les problèmes particuliers.

- Le problème multi- objectif peut être adressé par des moyens d'approches génétiques.

# A.7. ALGORITHMES GENETIQUES APPLIQUES AU PROBLEME DE LA NAVIGATION

Ce paragraphe expose comment les AGs ont été appliqués : ces algorithmes permettent de trouver la trajectoire la plus optimale (le paramètre est la distance ) sous forme de points de passage sans collisions entre le point Source et le point But .

### Modélisation du problème

On se propose à présent d'appliquer comme une alternative les AGs pour la recherche de la trajectoire la plus optimale. On montre que l'établissement d'une stratégie de renouvellement et de tri des coûts des chemins ( la distance) permet de trouver le chemin le plus optimal pour effectuer la mission du robot. L'étape la plus délicate dans l'application des AGs est la modélisation du problème. Comme nous avons le graphe ( les sous- passages ) de l'environnement ( ce graphe obtenu après la génération de plan et modélisation ), la recherche du plus court chemin par les AGs utilise les informations déduites de celui-ci.

La population sera formée d'un ensemble de chemin, ou chaque chemin est une suite de grille (sous-buts) de passage de robot. Ainsi que la population est prise comme un ensemble d'individus de taille connue (le nombre de sous points de passage sur le chemin). Ce dernier est représenté par une chaîne binaire de taille fixe, modélisant une suite de sous buts ou points du passage de robot dans l'environnement. En terme de biologie, les individus sont les chromosomes et les positions sont les gènes.

Le principe consiste à construire une population initiale de chemin de façon aléatoire, puis d'appliquer les opérateurs génétiques. Il s'agit de combiner des paires de chromosomes choisis aléatoirement, d'attribuer un coût à les trajectoires obtenues. Ce traitement se répétera jusqu'à obtenir un certain nombre  $^{\rm c}$  Pop Size  $^{\rm a}$  ou bien la taille de population d'individus. On relancera le processus de production de population autant de fois nécessaire pour obtenir les meilleurs individus ( bien étendu le chemin optimal). L'arrêt est contrôlé par une fonction statistique vérifiant la variation des coûts des chemins, notre critère d'arrêt est appliqué lorsque la nouvelle population obtenue lors de la progéniture atteint le nombre  $2^n-4$  ( n étant le nombre de chemin ), on retranche le nombre 4 car on peut pas comparer et combiner un chemin avec lui même.

### Fonction d'adaptation

La fonction d'adaptation sert à calculer le coût du chemin. Pour tout chromosome, on calcule la distance séparant le point courant et le point qui lui est visible, en évitant le cas de collision, ce point devient le point courant et on recommence le calcul, après sommation du trajet effectué jusqu'à atteindre la cible ( c'est à dire jusqu'à ce que le point actuel soit égal à la cible ).

### Sélection et Opérateurs génétiques

On sélectionne au hasard des individus de la population caractérisés par leurs fonctions d'adaptation ( la distance), on obtiendra par la suite une population P' sur laquelle on appliquera la reproduction avec croisement et mutation. Pour le crossover : on choisit au hasard deux individus ( appelés parent 1 et parent 2), ensuite, on applique l'opérateur de combinaison et de comparaison, à chaque exploration, on compare le coût et on sauvegarde la valeur du coût minimal. Le processus s'effectuera 12 fois " critère d'arrêts " et on aura donc après plusieurs générations les meilleurs points de passage du robot. Cette opération sert à modifier plusieurs gènes de chromosomes après avoir choisir le meilleur coût. Le

chemin déduit de cette opération est le plus optimal pour la navigation et ceci bien sûre pour le gain en énergie et la capacité de puissance contenus dans le corps fermé (robot).

### **B. LOGIQUE FLOUE**

### **B.1 INTRODUCTION**

La logique floue dite "fuzzy logic" a été introduite en 1965 par le professeur LOTFI ZADEH à l'université de Californie à Berkeley , jusqu'à ces dernières années, la logique floue était restée le domaine réservée de quelques chercheurs curieux et peu d'applications pratiques n'avaient vu le jour. Elle permet de manipuler des symboles et d'inférer des actions en utilisant les règles logiques à partir de prémisses imprécises ou incertaines. Le terme logique est lié directement à la logique classique, logique binaire dont la caractéristique première est de connaître deux états biens définis vrais ou faux. Au contraire la logique floue est lancée pour la formalisation de modes de raisonnement précis est vu comme un cas limité du raisonnement approximatif. Dans nos jours la logique floue a déjà trouvé une application pratique dans des produits très divers .

Il existe dans l'industrie de très nombreux processus de fabrication "optimisables" en faisant appel à la logique floue. C'est dans ce domaine en particulier que peuvent se concrétiser les avantages très spécifiques de cette nouvelle logique, dans notre monde de l'électronique ce nouveau terme "FLOUE" ne tardera pas à remplacer les "numériques" dans différentes utilisations.

Le chemin le plus utilisé pour combiner la logique floue et d'autres disciplines est la fuzzification qui consiste à associer à chaque entrée du système plusieurs notes qui sont les degrés d'appartenances aux différents sous-ensembles flous pour chaque entrée. Dans les années quatre - vingt dix : quelques recherches spécifiées sont pour l'accord sur la fonction de degré d'appartenance et la reconnaissance des échantillons.

### **B.2. DEFINITION**

La logique floue est considérée comme une extension de la théorie des ensembles. Etant donné un ensemble de référence X, on peut indiquer les éléments de X qui appartiennent à une certaine classe de X et ceux qui n'y appartiennent pas[15]. Si l'appartenance de certains éléments de X n'est pas absolue, on peut indiquer avec quel degrés chaque élément appartient à cette classe. Celle-ci est alors un sous-ensemble flou de X.

## **B.3. LES BASES DE LA LOGIQUE FLOUE**

L'un des fondements les plus importants de la logique floue est la théorie des ensembles.

### B.3.1. Théorie des ensembles flous

La logique floue travaille avec les ensembles flous, ces ensembles peuvent être définis mathématiquement par une fonction de degrés d'appartenance, qui définit pour tout élément le degrés d'appartenance à cet ensemble. Ce degrés varie de 0 à 1 [16].

Les notions d'inclusions, unions, intersections, complément et implication sont étendues aux ensembles flous [17].

#### **B.3.2. Définitions**

### B.3.2.1. Définition d'un ensemble flou

Soit X un ensemble de points, avec un élément de X noté par x. L'ensemble flou A dans X est caractérisé par la fonction d'appartenance FA(x), qui associe à chaque point de X le nombre réel limité par l'intervalle [0,1], avec la valeur de la fonction FA(x), représentant le degré d'appartenance de x dans A . Ainsi plus la valeur de FA(x) s'approche de un plus le degré d'appartenance de x dans A est grand [18].

#### B.3.2.2. Définition d'un ensemble flou vide

Un ensemble flou est vide , si et seulement si sa fonction d'appartenance est identique à zéro sur x.

### B.3.2.3. Définition de deux ensembles flous égaux

Deux ensembles flous A et B sont égaux, écris comme A = B, si et seulement si FA(x) = FB(x) pour tout élément x dans X

### B.3.2.4. Définition de l'intersection de deux ensembles flous

L'intersection de deux ensembles flous A et B avec des fonctions d'appartenance respectives FA(x) et FB(x) et l'ensemble flou C, écris comme  $C=A \cap B$ , donc la fonction d'appartenance est alliée à celle de A et B par :

$$FC(x) = MIN [FA(x), FB(x)], x \in X.$$

### B.3.2.5. Définition de l'union de deux ensembles flous

L'union de deux ensembles flous A et B avec des fonctions d'appartenance respectives FA(x) et FB(x) et l'ensemble flou C, écris comme  $C = A \cup B$ , dont la fonction d'appartenance est alliée à celle de A et B par [19]:

$$FC(x) = MAX [FA(x), FB(x)], x \in X.$$

### B.3.2.6. Définition du complément d'un ensemble flou

Le complément de l'ensemble flou A est noté Par A' est définit par FA'= 1-FA.

### B.3.2.7. Définition de d'implication de deux ensembles flous

L'opération est donnée par : si A est vrai, B est il aussi vrai ? A ⇒ B

En logique binaire l'opération d'implication est que si A n'est pas vrai, aucune information n'est connue pour B , sur ce n'importe qu'elle valeur de B est acceptable. Cette relation est donnée par le tableau suivant :

| Α | В | A⇒B |

|---|---|-----|

| 1 | 1 | 1   |

| 1 | 0 | 0   |

| 0 | 1 | 1   |

| 0 | 0 | . 1 |

Figure 2.4 : Table de vérité de l'implication

#### B.3.2.8. Définition d'un sous-ensemble flou

Un sous-ensemble classique A est défini par une fonction caractéristique Ga qui prend la valeur 0 pour les éléments de x n'appartient pas à A et la valeur 1 pour ceux qui appartiennent à A: Ga  $(x): X \to [0,1]$ . Un sous ensemble flou A est défini par une fonction d'appartenance qui associe à chaque élément x de X, le degrés FA (x), compris entre 0 et 1, avec lequel x appartient à A: FA $(x): X \to [0,1]$ . En général les fonctions d'appartenance sont des fonctions mathématiques simples de forme trapézoïdales, et ont pour but de faciliter le calcul et la représentation .

### **B.4. L'INFERENCE FLOUE**

Ce qu'on appelle inférence floue, c'est l'inférence d'action utilisant des règles logiques à partir des prémisses imprécises (floues). Le type de règles utilisé est simple du genre : si condition 1, condition 2, et ......condition n alors action [20].

### B.5. DEFINITION D'UN CONTROLEUR FLOU

Un contrôleur flou est un système définissant une fonction (par exemple à deux entées X, Y et une sortie U) basé sur des règles exprimées par des catégories linguistiques telle que [21,22]:

### Si (X est A1) et (Y est A2) alors (U est B)

ou` A1, A2, B sont des prédicats mentionnés comme "grand positif", "moyen", "petit négatif" etc.

Pour concevoir un contrôleur flou , il faut :

- Définir les variables d'entrée et les variables de sorties.

- Définir les ensemble flous correspondants.

- Définir les règles d'inférences.

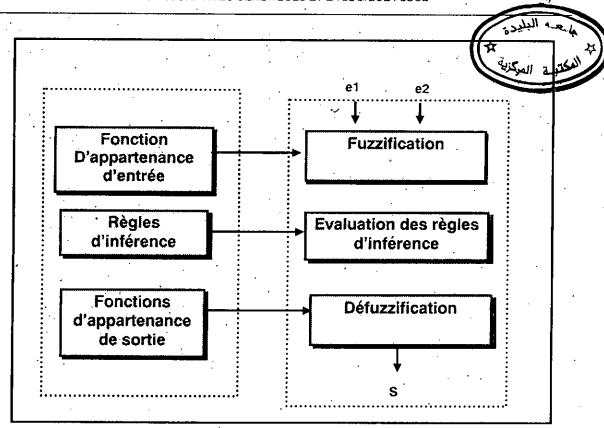

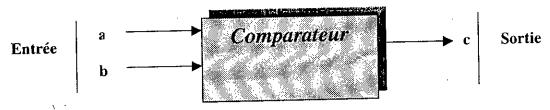

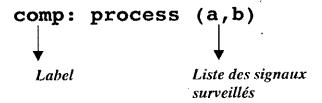

En termes plus formels, un contrôleur flou (dont la structure générale est donnée dans la figure 2.5 [23] ) se compose de trois modules opérant sur un système d'entrée et délivrant un système de sortie. Ces modules sont les suivants [22, 24, 25]:

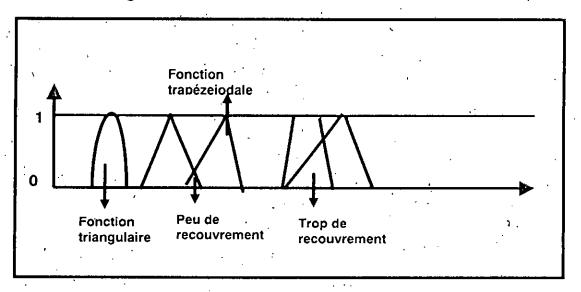

## **B.5.1. Fuzzification:**

Comme les valeurs d'entrée du contrôleur ne sont pas floues , il est nécessaire de les rendre floues, afin de pouvoir faire l'inférence floue et de faciliter le calcul [26]. La fuzzification consiste à calculer les degrés d'appartenance de chaque valeur d'entrée aux ensembles flous correspondants à la variable qu'elle présente. Ces ensembles sont utilisés mathématiquement par une fonction d'appartenance . La fuzzification a pour but de faciliter les calculs et représentation, les fonctions utilisées sont des fonctions triangulaires et trapézoïdales . La figure 2.6 représente les différents cas d'ensembles flous :

### B.5.2. L'inférence floue

Cette technique est déjà expliquée ci dessus et qui représente une étape importante pour un contrôleur flou. En effet, c'est une application des règles d'inférence pour déterminer la grandeur de sortie. La logique floue a besoin d'une large variété de concepts et de techniques pour la représentation et la déduction à partir des connaissances. Celles ci se focalisent sur les règles d'inférences de types *If /THEN* [27,28,29,30,31]. Un grand nombre de relations exprimées sous formes d'implications floues peuvent être utilisées pour la représentation de la signification d'une règle de production tel que comme : if ( proposition 1 ) *THEN* (proposition 2).

## B.5.3. Défuzzification

Elle consiste à calculer la valeur de sortie finale du système, grâce aux sorties floues et aux fonctions d'appartenance de sortie. Parmis les techniques de défuzzification les plus utilisées nous pouvons citer : la méthode du centre de gravité et la méthode de la moyenne pondérée.

À œux qui sont encastrés dés les premières lucins de l'aube, œux qui résonnaient au bruit parvenait par les bribes de fréquents, riexber entre les toits d'un cinéma, croyant avoir la cage d'un acteur et vaiment qui peuvent renærser sans scrupules le manipule d'un favori des scénaries.

À tous œ qui sont entrecroisés par les traces du crayon, sur la timidité tacite à piraterie, indinée par la doison de peur pour s'écarter à des degrés de mesure d'un fil ombré doté à le trafiquer.

À œux qui creusent le reste du temps derrière le flot des piétors, lorsque les trottoirs sont encombrés, œux qui sont vaiment coincé au balayage d'un fétu de paille leur poussés soudaient à reprit sentencieux.

À œux qui distribuent le fleure en temps décrue emplissant les yeux au contre – comant basculé souvent par les nuages de la librairie bandée, qui ne s'écraseront jamais aux regards sombres logés au prés de la raque de la mujesté.

À œux qui mesurent le marché des connaissances essuyer par les rayants nombreux prometteurs qui circulent dans les parois de l'expérience et qui nous heurtent par les activités utiles livrées par une certitude très daire à discipliner désonnuis de tous freires qui prenait la loi, ou plus que jamais le temps a son prit.

Qu'on ne peut guère réclainer d'autrui, et dest bien regietable...

Mais il viendra le pouvoir de parserner aux sobriété un texte de réminisarnee, orné son esprit de ces traits légers ou moraux qui agrémentent les cornersations d'un art de bon aloi habité à l'abnégation de la modestie.

À œux que je leur offre les termes de la bougie ou`ils jasaient le soir à petits bruits, quand la fenêtre rougit pour ouvrir les âmes d'un petit récit, ou`ils ne refusaient jamais les sons des surprises car faire fuir tous œux qui ont quoi rendérissent les fripors qui ne finiront point.

À tous œux qui m'ont aidée, airrée, conduite à la vie éternelle de prix égaré dans le voilà assez..., d'une façon ou d'une autre, et qui par oubli ne figurent pas ici.

À œux qui vont sûrement reconnaître cette piste arrosée par le manque de terms.

En wilà assez! il faut s'arrêter... pour toucher le wile pétrissant et dire :

À tous œux qui ont incinéré leur passé comme font les incliens à leurs morts et qui s'il leur reste des ændres les jettent à la mer.

Figure 2.5 : Structure d'un contrôleur flou

Figure 2.6 : Différents cas d'ensembles flous

## B.6. CONTROLEUR FLOU APPLIQUE AU MOUVEMENT DU ROBOT

Pour une bonne exécution de la trajectoire de référence ( issue de l'étage des algorithmes génétiques expliqué dans la première section A), nous pourrons encore plus optimiser cette référence en appliquant le contrôleur logique flou [58]. Ce dernier peut encore nous offrir une bonne assurance d'atteindre la cible en

évitant les obstacles et réaliser un bon lissage afin de gagner et réaliser les exigences d'autonomies.

### Contrôleur flou appliqué pour avoir une bonne optimisation

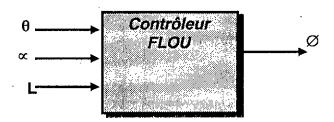

En ayant la trajectoire de référence, le mouvement du robot peut être contrôlé par un contrôleur flou. Connaissant l'allure du chemin à suivre, le robot doit viser le sous but à atteindre à chaque pas d'avancement. Les directions à prendre dépendant alors des points intermédiaires de la trajectoire de référence. Le contrôleur utilisé est illustré dans la figure suivante :

figure 2.7 :Le modèle de contrôleur flou utilisé

Selon cette figure le contrôleur a comme entrée

$\theta$  ; est l'orientation courante du robot (actuelle).

$\alpha$ : l'orientation avec laquelle le robot s'oriente pour rejoindre le po int visé. L : la dis tan ce int ermidiare entre le po int acuel et le po int visé, le po int courant et le point int ermédiaire et le point int ertermédiare et le point visé.

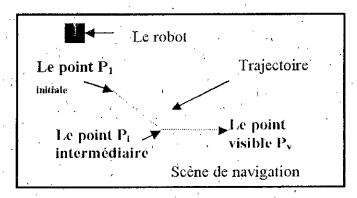

L'orientation déduite du contrôleur flou Ø est l'orientation délivrée pour le robot, donc cette sortie du contrôleur représente l'orientation pour rejoindre le point visé en évitant les obstacles, le processus se répète jusqu'à ce que le point visé devient la cible (voir la figure 2.8).

Le processus de traitement est décrit par les démarches suivantes :

Calculer l'angle  $\theta$ : celui ci est déterminé par la pente du segment de la droite liant le point actuel (X1,Y1) et le point qui lui est intermédiaire (Xi, Yi) donné par

$$\theta = \tan^{-1} \frac{\left(Y_i - Y_1\right)}{\left(X_i - X_1\right)}$$

Calculer l'angle x : cet angle représente la différence de phase avec laquelle le robot rejoint le point visible et qui est illustré par :

$$\alpha = \tan^{-1} \frac{\left(Y_{\nu} - Y_{1}\right)}{\left(X_{\nu} - X_{1}\right)} - \theta$$

Calcul de la distance selon les cas : entre le P<sub>1</sub> et P<sub>1</sub>, P<sub>i</sub> et P<sub>v</sub> et P<sub>1</sub> et P<sub>v</sub> (voir la figure 2.8).

Ce processus se répétera à chaque segment et à chaque pas d'avancement jusqu'à ce que le point visé devient la cible ( l'objectif est atteint ).

Figure 2.8 : exemple d'une scène de navigation

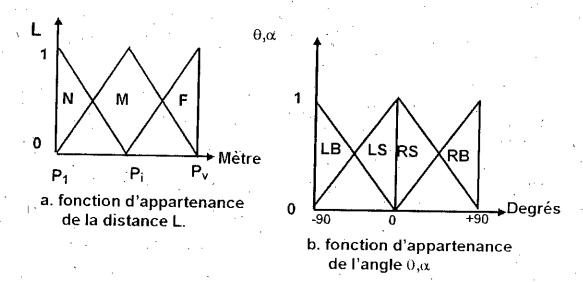

#### B. Variables linguistiques

#### B.1. Variable Linguistiques utilisées pour l'angle « et 0 sont :

Grand gauche LB ( Left Big). Petit gauche LS ( Left Small). Petit droit RS ( Right Small). Grand droit (Right Big).

#### B.2. Variable Linguistiques utilisées pour la distance L :

Proche N ( *Near*). Moyen M (*Medium*). Loin F (*Far*).

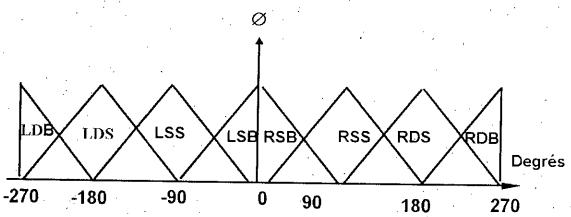

#### B.3. Variable Linguistiques pour l'angle $\varnothing$

Grand danger gauche (LDB): Left Danger Big.

Petit danger gauche (LDS): Left Danger Small.

Petite sécurité gauche (LSS): Left Safery Small.

Grande sécurité gauche (LSB): Left Safety Big.

Grand danger droit (RDB): Right Danger Big.

Petit danger droit (RDS): Right Danger Small.

Petite sécurité droite (RSS): Right Safety Small.

Grande sécurité droite (RSB): Right Safety Big.

#### C. Fonctions d'appartenances

Les fonction d'appartenances utilisées sont les suivantes :

Figure 2.9 : Les fonction d'appartenances utilisées pour les variables d'entrées

Figure 2.10: Les foncions d'appartenances de la direction  $\varnothing$

La défuzzification qui se traduit par la décision du système s'expose par la formule suivante

$$G = \frac{\sum \left( \mu_i * g_i \right)}{\sum \mu_i} \quad 1 \le i \le m.$$

Ou' m : le nombre de règles inférences .

g<sub>i</sub> : le centre de gravité. μ<sub>i</sub> : degrés d'appartenance.

Les règles d'inférences sont définies comme suit

```

Si (θ est LB et L est N) Alors (Ø est LDS)

Si (θ est LB et L est M) Alors (Ø est LSS)

Si (θ est LB et L est F) Alors (Ø est LSB)

Si (θ est LS et L est N) Alors (Ø est LDB)

Si (θ est LS et L est M) Alors (Ø est LDS)

Si (θ est LS et L est M) Alors (Ø est LDS)

Si (θ est LS et L est N) Alors (Ø est RDB)

Si (θ est RS et L est N) Alors (Ø est RDS)

Si (θ est RS et L est M) Alors (Ø est RDS)

Si (θ est RS et L est F) Alors (Ø est RSS)

Si (θ est RB et L est N) Alors (Ø est RDS)

Si (θ est RB et L est M) Alors (Ø est RSS)

Si (θ est RB et L est M) Alors (Ø est RSS)

Si (θ est RB et L est M) Alors (Ø est RSS)

```

```

Si (∞ est LB et L est N) Alors (⊘ est LSS)

Si (∞ est LB et L est M) Alors ⊘ est LSS)

Si (∞ est LB et L est F) Alors (⊘ est LSB)

Si (∞ est LS et L est N)Alors (⊘ est LDB)

Si (∞ est LS et L est M) Alors (⊘ est LDS)

Si (∞ est LS et L est F) Alors (⊘ est LSS)

Si (∞ est LS et L est N) Alors (⊘ est RDB)

Si (∞ est RS et L est M) Alors (⊘ est RDS)

Si (∞ est RS et L est F) Alors (○ est RDS)

Si (∞ est RB et L est N) Alors (○ est RDS)

Si (∞ est RB et L est M) Alors (○ est RDS)

Si (∞ est RB et L est M) Alors ○ est RSS)

Si (∞ est RB et L est F) Alors ○ est RSS)

```

Figure 2.11 : Les règles d'inférences utilisées.

Remarque: Les vitesses du véhicule sont considérées constantes dédiées pour trois phases: accélération si le point visé est loin, vitesse est constante dans des distances intermédiaires et décélération dans la dernière portion de la trajectoire pour rejoindre le point visé (dans un autre cas ce point visé devient la cible) et ralentissement dans un virage (évitement d'obstacles), dans ce cas la vitesse du robot doit être suffisamment réduite pour qu'il ne dérape pas et ne sort pas de la trajectoire.

Notre objectif était en fait de jouer sur les directions du moment qu'on a une trajectoire de référence optimale et de contrôler et d'optimiser plus à partir de cette référence. Nous voulons réaliser une tâche qui répond aux critères de la navigation afin de gagner plus en temps , en coût , en consommation , etc.

#### 2. CONCLUSION

L'idée ultime de ce chapitre consiste à exposer les performances de la logique floue et les algorithmes génétiques pour résoudre les points sensibles d'un problème d'optimisation et raisonnement non binaire, nous avons donc pris connaissance de la robustesse et comment manipuler les AGs et la LF.

Les systèmes hybrides intelligents basés sur les AGs et la LF offrent un comportement intelligent pour un robot mobile autonome.

Les AGs sont des alternatives inhérentes pour le problème d'optimisation de la trajectoire, en établissant une stratégie de renouvellement et de tri des coûts des chemins. Les AGs permettent en un temps acceptable d'obtenir la meilleure solution.

A cote de cette solution ultime, la logique floue est un outil très puissant qui peut faciliter la modélisation des problèmes basés sur le raisonnement humain, sans avoir recours à des constructions mathématiques complexes. Cet

outil nous a permis de trouver la meilleure orientation à donner pour notre robot pour accomplir la mission demandée. De plus, la logique floue rend le mouvement plus robuste et plus fiable. Ce mouvement lisse est adéquat pour exécuter une trajectoire faisable. Ceci n'exclut pas le fait de présenter quelques inconvénients, à savoir : la nécessité de bien définir le problème et surtout la nécessité d'évaluer et d'affiner les résultats.

#### Chapitre 3

# LES ASICs et LES FPGAs

### A. CIRCUITS ASICS

#### A.1. INTRODUCTION

Le rôle des fabricants de semi-conducteurs pendant ces trois dernières décennies ne s'est pas limité à faire progresser la technologie et, ainsi, à augmenter le nombre de fonctions par circuit ; il s'est aussi attaché à définir des types de circuits à créer et à commercialiser pour répondre aux demandes des utilisateurs. La demande des utilisateurs a toujours été une constante : être capable de réaliser des fonctions de plus en plus complexes occupant le moins de place possible, c'est à dire coûtant le moins cher, utilisant le moins d'énergie et fonctionnant le plus rapidement possible[32,33,34]. Pour ce faire , les fabricants de semi-conducteurs ont proposé au fil des années des produits susceptibles de répondre à ces besoins.

#### Dans les années 1960 :

- Les circuits intégrés SSI (Small Scale Integration), les portes.

- Puis les MSI (Medium Scale Integration), les registres à décalages, les compteurs.

#### Dans les années 1970 :

Les circuits LSI (Large Scale Integration), les microprocesseurs.

#### Dans les années 1980 :

• Les circuits intégrés VLSI (Very Large Scale Integration) : la révolution moderne de la micro-électronique.

Notons que cette évolution a amené, au milieu des années 1970, à résoudre la majeure partie des problèmes. Cette évolution s'est heurtée à plusieurs obstacles. D'une part la gamme des produits offerts aux utilisateurs n'est pas infinie, ceux - ci ne trouvent pas toujours les circuits adaptés à leurs applications, d'autre part, les fabricants de semi-conducteurs ont des difficultés à poursuivre l'innovation interne et, enfin vu le retard des outils de conception et de test rend plus difficile et plus coûteuse la conception de produit très complexes.

Ainsi les produits standards, les plus complexes soient ils , ne peuvent pas tous répondre, dans les meilleurs conditions, aux préoccupations de tous les utilisateurs.

La fabrication d'un circuit intégré nécessite un certain nombre d'étapes technologiques, afin de réaliser les différents composants du circuits. Cependant, elle est extrêmement coûteuse en temps de conception et en investissement de logiciel et, de plus, nécessite une bonne connaissance des règles technologiques du fondeur. Pour cela une voie s'est ouverte dans les années 1980 sous un nouveau concept spécifique : l'utilisation des ASICs (Application Specific Integrated Circuits) ou bien "circuits intégrés pour des application spécifiques". Cette voie a pu voir le jour grâce surtout aux progrès des outils de CAO (Conception Assistée par Ordinateur). Ils sont, en effet, devenus suffisamment performants pour permettre aux concepteurs, de concevoir un circuit intégré rapide. Les ASICs pour les années 90 tiennent une place aussi importante que les microprocesseurs dans les années 70 et 80.

La conception de ces circuits nécessite une culture générale en électronique de base, des notions élémentaires de technologie et la maîtrise des outils de CAO, alors ; Qu'est ce qu'un un circuit ASIC ? Pour répondre a cette question, la section suivante peut éclairer la richesse du domaine.

#### A.2. DEFINITION

Par définition, les circuits *ASICs* regroupent tous les circuits dont la fonction peut être personnalisée d'une manière ou d'une autre en vue d'une application spécifique, par opposition aux produits standards courants de fonctionnement normaux [34].

Dans ce qui suit, nous allons passer sur les différents types de circuits ASICs qui peuvent exister.

#### A.3. STYLES DE CONCEPTION

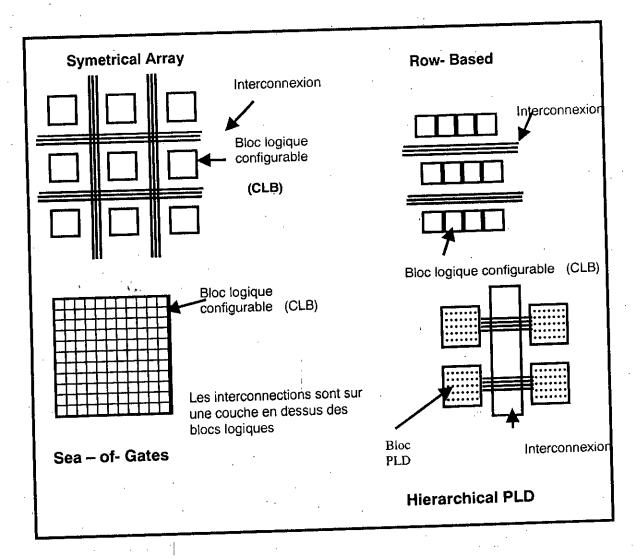

Du concept ASIC découle quatre grands styles de conceptions (Design Style) à savoir :

- Les circuits sur mesure " Full Custom ".

- Les circuits précaractérisés " Standard Cells ".

- · Les circuits prediffusés " Gate Array ".

- Les réseaux logiques programmables "FPGA, PLD".

Chaque famille diffère par rapport à l'autre dans : le niveau de complexité, un type d'outils de conception et une méthodologie de conception. Dans ce qui suit, nous allons exposer les quatre familles :

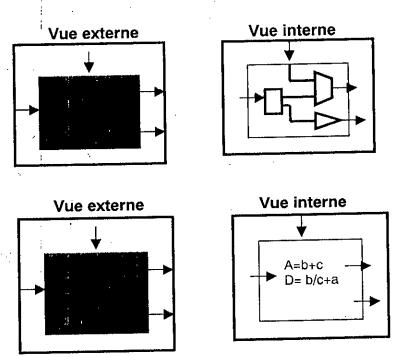

#### A.3.1. Circuits sur mesures "Full Custom"

Historiquement, ce sont les premiers ASICs qui ont été développés. Dans une conception full custom les dimensions et les performances d'un circuit sont optimisées. Toutes les étapes de fabrication sont spécifiques mais le temps de conception, ainsi que les coûts de développements sont très élevés par rapport aux circuits précaracterisés.