الجمهورية الجزائرية الديمقراطية الشعبية République Algérienne démocratique et populaire

وزارة التعليم السعساني والبحث العسامسي Ministère de l'enseignement supérieur et de la recherche scientifique

> جامعة سعد دحلب البليدة Université SAAD DAHLAB de BLIDA

> > كلية التكنولوجيا Faculté de Technologie

قسم الإلكترونيك Département d'Électronique

#### Mémoire de Master

Mention Électronique

Spécialité Microéléctronique, Microsystème et Conception de Circuit

présenté par

Azibi Rafik

&

Diellali Samir

# Conception d'une bibliothèque de cellule standard en technologie CMOS 1µm

Proposé par : Djouama Malik & Bougherira Nadia

Année Universitaire 2016-2017

Avant tout nous remercions "Allah" tout puissant qui nous a donné le courage, la volonté et la force pour accomplir ce modeste travail. Merci de nous avoir éclairé le chemin de la réussite.

Nous avons le grand plaisir d'exprimer nos sentiments les plus profondes par le remerciement de notre promotrice Mme N.BOUGHRIRA et promoteur Mr M.DJOUAMA de leur aide à concevoir ce projet de fin d'étude et de leur guide et entretien afin de nous donner un encouragement à sa réalisation.

Nous remercions tous les participants et les enseignants de département d'électronique et l'équipe de chercheurs de département micro-électronique de CDTA pour leur aide durant notre cursus universitaire.

### **Dédicaces**

#### Je dédie ce travail à:

- Mes très chers parents qui m'ont encouragé pendant le long de mes études et soutenu par leur amour et leur tendresse.

- Mes frères et mes sœurs.

- ➤ Toute ma famille sans exception

- Les professeurs et mes camarades de la spécialité « Microé lectronique, Microsystèmes et Conception de Circuits ».

- Le D. Djoumaa Malik qui m'a encadré dans ce projet de fin d'étude.

### **Dédicaces**

#### Je dédie ce travail à:

- Mes très chers parents qui m'ont encouragé pendant le long de mes études et soutenu par leur amour et leur tendresse.

- Mes deux frères et mes deux sœurs.

- > Toute ma famille DJELLALI et IDJELLIDAINE

- Mes cher aimes « Seyfo ,Hosam,Raouf,Mohamed Bouali,Sou alhi,Mohamed Cherif »

- Le D. Djoumaa Malik qui m'a encadré dans ce projet de fin d'étude.

ملخص:

هذه الأطروحة تستعرض جزءا من دراسة و تحقيق لخلية منطقية لمكتبة قياسية مخصصة إلى حساب محطة تكنولوجية (غرفة بيضاء) التي تقع في مركز تنمية التكنولوجيات المتطورة. هذه المكتبة تسهل تصميم و تنفيذ دارات ().المكتبة القياسية تتكون من عدة بوابات منطقية بسيطة (و,او,...) و معقدة (المهزة, الجامع, الذاكرة) مع التكنولوجيا 1 مبكرو متر. الدراسة في السؤال تأخذ بعين الاعتبار عدة عوامل, استهلاك (التيار، والاستطاعة) والتوقيت (مدة الانتشار، زمن الصعود, زمن النزول) والابعاد. تبدأ هذه الدراسة عن طريق تعريفات حول مختلف المكتبات التكنولوجية في السوق الصناعية، واستعمال جميع النظريات مع مراعاة دفتر شروط المكتبة. سيتم استخدام أداة التصميم لبرنامج كادونس أثناء تدفق التصميم. ثلاث خطوات لتحقيق الخلايا المنطقية: التصميم، تصميم القناع (التخطيط)، والتحقق من قواعد التصميم.

كلمات المفاتيح :التصميم المحاكاة التخطيط

#### Résumé :

Ce mémoire de fin d'études aborde une partie d'une étude et réalisation de cellule logique d'une bibliothèque standard dédiée pour le compte d'une Centrale technologique (salle blanche) situé au centre de développement des technologies CDTA. Cette bibliothèque facilite la conception et l'implémentation des circuits ASIC. La bibliothèque standard est constituée de plusieurs portes logiques simples (and, nand, or, nor.) et complexes (MUX, bascule, additionneur, mémoire.) avec la technologie 1µm. l'étude en question prend en considération plusieurs facteurs, consommation (courant, puissance), timing (délais de propagation, temps de monté et temps de décente) et dimension. Cette étude commence par l'état de l'art sur les différentes bibliothèques des technologies dans le marché industriel, par la suite, développé toute la théorie en prenant compte du cahier de charge de la bibliothèque. L'outil de conception Virtuoso de Cadence sera utilisé durant le flow de conception. Trois étapes nécessaires pour la réalisation de ses cellules logiques : conception, dessin de masque (layout), et vérification des règles de dessin.

Mots clés: conception, simulation, layout.

#### Abstract:

This thesis addresses a part of a study and realization of cell logic from a standard library dedicated to the account of a Central technological (clean room) located at the center of development of technologies CDTA. This library facilitates the design and implementation of ASICS. The standard library consists of several logic gates simple (and, nand, or, nor.) and complex (MUX, flip-flop, adder, memory.) with the technology 1µm. The study takes many factors into account, consumption (current, power), timing (time delays, time mounted time decent) and dimension. This study begins with the state of the art on the different libraries of the technologies in the industrial market, subsequently, developed the theory by taking account of the specifications of the library. The design tool Virtuoso from Cadence will be used during the flow of design. Three steps necessary for the realization of its logic cells: design, drawing of mask (layout) and verification of the rules of drawing.

**Keywords**: design, simulation, layout.

| Introduction générale                                                 |    |

|-----------------------------------------------------------------------|----|

| Chapitre 1 : Conception des circuits intégrés                         | 1  |

| 1.1. Introduction                                                     | 2  |

| 1.2. Les ASICs (Application Spécifie Integrated Circuit)              | 2  |

| 1.2.1. Définition                                                     | 2  |

| 1.2.2. Méthode de conception.                                         | 2  |

| 1.2.3. Avantages et inconvénients de l'utilisation d'ASIC             | 3  |

| 1.3. Opérations élémentaires pour la fabrication des transistors CMOS | 4  |

| 1.4. Circuit CMOS dans le silicium.                                   | 7  |

| 1.4.1. Règles de dessin.                                              | 7  |

| 1.4.2. Paramètres électriques.                                        | 8  |

| 1.4.3. Dispersion de paramètre                                        | 9  |

| 1.4.4. Protection de l'entrées/sorties                                | 9  |

| 1.5. Caractéristiques importantes et critères de sélection            | 10 |

| 1.5.1. Caractéristiques de transfert                                  | 10 |

| 1.5.2. Marges de bruit                                                | 11 |

| 1.5.3 .Fan-in et fan-out.                                             | 11 |

| 1.5.4. Puissance dissipée                                             | 11 |

| 1.5.5. Délais de propagation par porte                                | 11 |

| 1.5.6. Produit puissance-délai.                                       | 11 |

| 1.6. Conclusion.                                                      | 12 |

| Chapitre 2 : Etude théorique des portes logiques13                |

|-------------------------------------------------------------------|

| 2.1. Introduction                                                 |

| 2.2. Rappel théorique sur les transistors MOS                     |

| 2.2.1. Les dimensions importantes dans un MOS                     |

| 2.2.2. Régimes de fonctionnement du transistor MOS                |

| a. Le régime bloqué15                                             |

| b. Le régime linéaire (ohmique)16                                 |

| c. Le régime de saturation                                        |

| d. Le régime de forte saturation (effet de modulation du canal)17 |

| e. Le régime de faible inversion                                  |

| 2.2.3. Modélisation du transistor MOS                             |

| a. Modèles petits signaux en régime saturé21                      |

| b. Modélisation petits signaux en régime Ohmique23                |

| c. Modélisation petits signaux en régime bloqué24                 |

| 2.3. Inverseur CMOS                                               |

| 2.3.1. Principe de fonctionnement                                 |

| 2.3. 2. Régime statique                                           |

| 2.3. 3. Caractéristiques de transfert dans un inverseur           |

| 2.3.4. Analyse en régime dynamique                                |

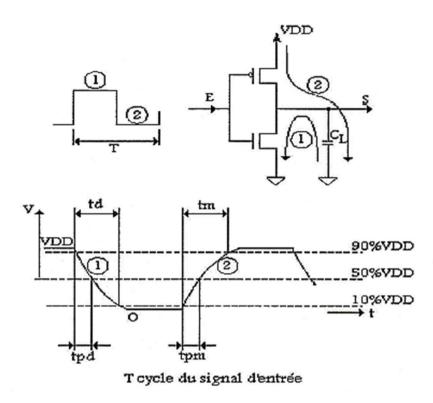

| a. Temps de descente t <sub>d</sub>                               |

| b. Temps de montée t <sub>m</sub> 30                              |

| c. Temps de propagation à la descente t <sub>pd</sub> | 31 |

|-------------------------------------------------------|----|

| d. Temps de propagation à la montée t <sub>pm</sub>   | 32 |

| 2.3.5. Puissance dissipée                             | 33 |

| a.Puissance dynamique                                 | 33 |

| b. Puissance statique                                 | 33 |

| c. Puissance de court-circuit.                        | 33 |

| d. Puissance totale                                   | 34 |

| 2.4. Portes logiques de base                          | 34 |

| 2.4.1. Porte NAND.                                    | 37 |

| 2.4.2. Porte AND                                      | 38 |

| 2.4.3. Porte NOR.                                     | 38 |

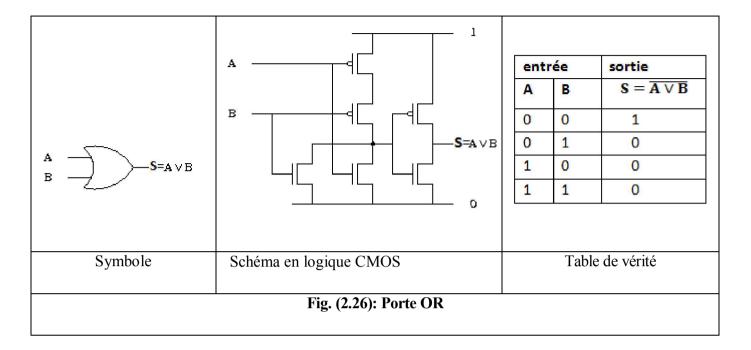

| 2.4.4. Porte OR                                       | 39 |

| 2.5. Conclusion.                                      | 40 |

| Chapitre 3: Etude pratique des portes logiques        | 41 |

| 3.1 Introduction.                                     | 42 |

| 3.2 Outil de conception Cadence                       | 42 |

| 3.2.1 Présentation du design kit.                     | 42 |

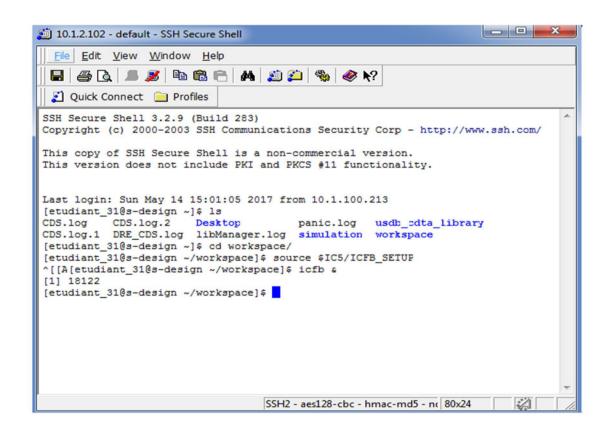

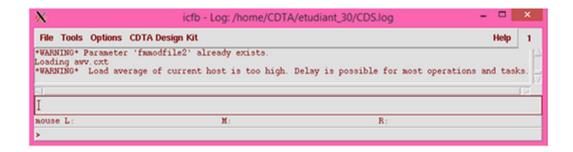

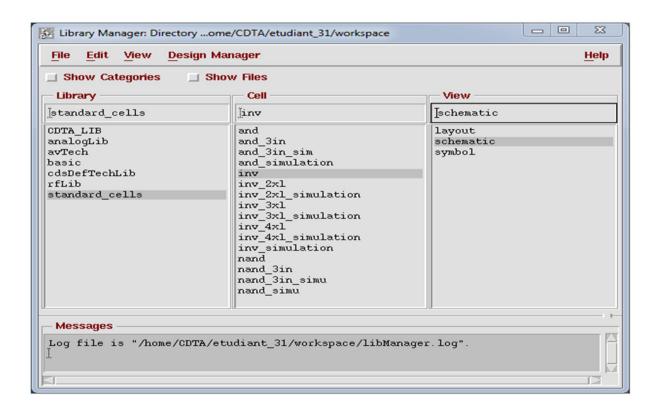

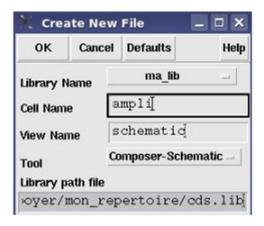

| 3.2.2 Création d'un projet sur cadence                | 43 |

| 3.3 Bibliothèque des cellules                         | 45 |

| 3.3.1. Concept                                        | 45 |

| 3.3.2. Librairie de base.                             | 46 |

| 3.3.3. Mode de représentation.                                                | 46 |

|-------------------------------------------------------------------------------|----|

| 3.4 Tests et résultats des différents éléments de la bibliothèque             | 47 |

| 3.4.1. Cellule simple                                                         | 47 |

| a. Inverseur simple.                                                          | 47 |

| b. porteNAND2XL                                                               | 57 |

| c. Porte AND2XL.                                                              | 60 |

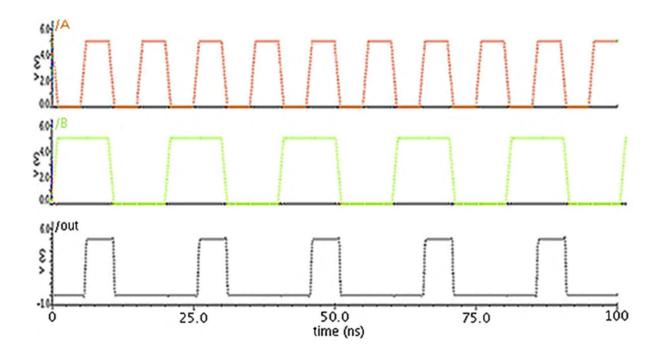

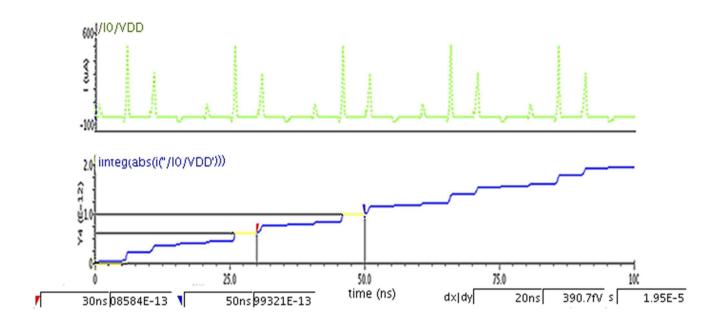

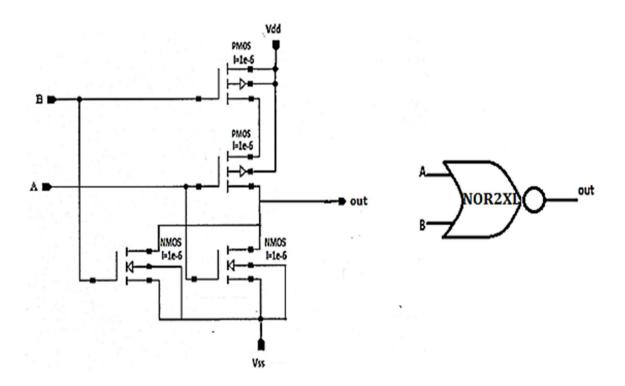

| d. porte NOR2XL                                                               | 63 |

| e. Porte OR2XL                                                                | 64 |

| 3.4.2 Cellules complexes.                                                     | 66 |

| a. NAND3XL                                                                    | 66 |

| 3.5 Vues géométriques (Layout)                                                | 70 |

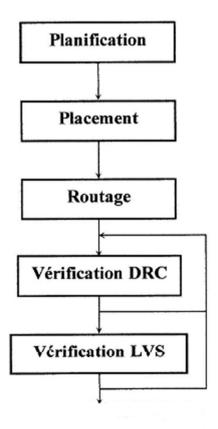

| 3.5.1. Les étapes de layout                                                   | 70 |

| a. Planification.                                                             | 71 |

| b. Topologie de la forme générale                                             | 71 |

| c. Placement des composants                                                   | 71 |

| d. Routage                                                                    | 71 |

| e. Vérification d'un layout.                                                  | 71 |

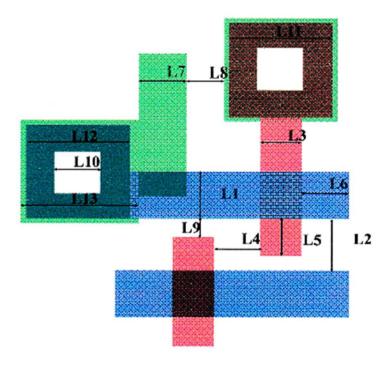

| 3.5.2. Layout et règles de dessin.                                            | 73 |

| a. les différentes couches utilisées dans un layout                           | 73 |

| b. Règles de Conception d'un layout.                                          | 75 |

| c. Les points communs entre les différentes cellules formants la bibliothèque | 77 |

#### Table des matières

| d. Les étapes de dessins. | 78 |

|---------------------------|----|

| 3.6 Conclusion.           | 82 |

| Conclusion générale       | 83 |

| Bibliographie             |    |

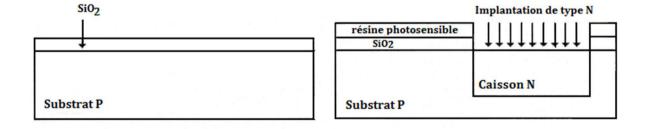

| Figure 1.1. Réalisation du caisson N sur le substrat                      | 4  |

|---------------------------------------------------------------------------|----|

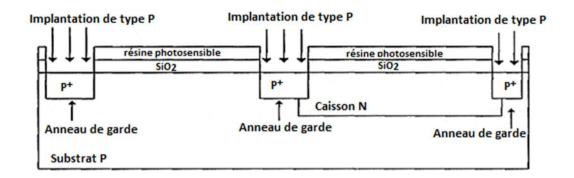

| Figure 1.2 .Fabrication des anneaux de garde et champ d'oxyde épais       | 5  |

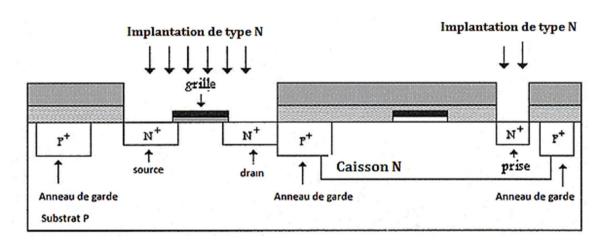

| Figure 1.3. Fabrication des grilles poly-cristallines et des diffusions N | 5  |

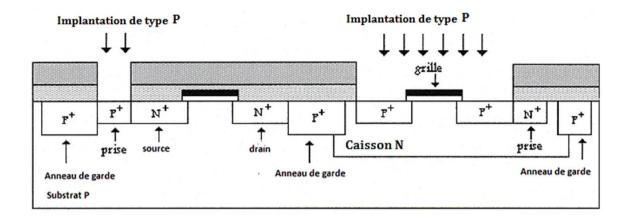

| Figure 1.4. Diffusions P.                                                 | 6  |

| Figure 1.5. Premier niveau d'interconnexion.                              | 6  |

| Figure 1.6. Caractéristiques de transfert                                 | 10 |

| Figure 2.1. Dimensions dans un MOS                                        | 15 |

| Figure 2.2 .Le MOS en régime de blocage                                   | 15 |

| Figure 2.3. Formation du canal en dessous de la grille                    | 16 |

| Figure 2.4 .Distribution des charges en régime ohmique                    | 16 |

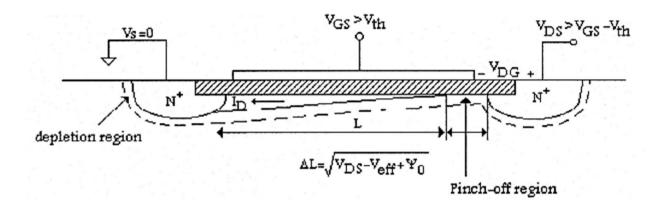

| Figure 2.5. Pincement du canal                                            | 17 |

| Figure 2.6. L'expression du courant dans les régimes de conduction        | 17 |

| Figure 2.7. L'effet de la modulation du canal                             | 18 |

| Figure 2.8. Régime de faible inversion.                                   | 19 |

| Figure 2.9. Effet du substrat.                                            | 20 |

| Figure 2.10. Caractéristique du NMOS                                      | 20 |

| Figure 2.11. Modèle petit signal a basse fréquence                        | 21 |

| Figure 2.12. Modèle petit signal à haute fréquence                        | 22 |

| Figure 2.13.Modèle petit signal dans le régime ohmique                    | 23 |

| Figure 2.14. Modèle petit signal dans le régime bloqué                    | 24 |

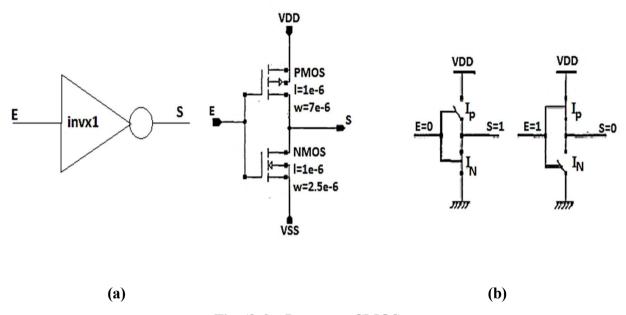

| Figure 2.15. Symbole et réalisation de l'inverseur en technologies CMOS   | 25 |

| Figure 2.16. Caractéristiques de transfert d'un inverseur CMOS                         | 26 |

|----------------------------------------------------------------------------------------|----|

| Figure 2. 17. Capacité totale de charge de sortie d'un inverseur CMOS                  | 28 |

| Figure 2.18. Processus de chargement et de déchargement de la capacité de sortie CMOS. |    |

| Figure 2.19. Schéma de principe de la logique complémentaire                           | 35 |

| Figure 2.20. Schéma du fonctionnement de la logique complémentaire                     | 35 |

| Figure 2.21. Porte NAND.                                                               | 37 |

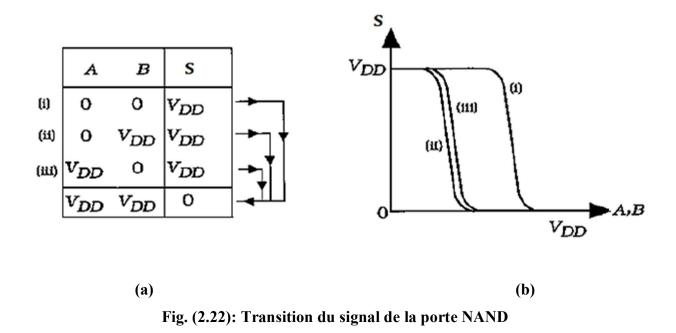

| Figure 2.22. Transition du signal de la porte NAND.                                    | 37 |

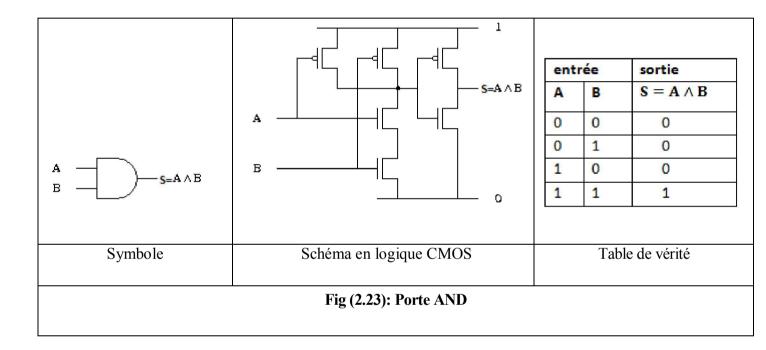

| Figure 2.23. Porte AND.                                                                | 38 |

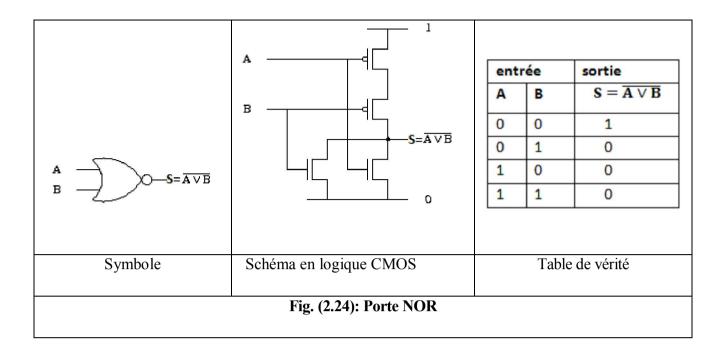

| Figure 2.24. Porte NOR.                                                                | 39 |

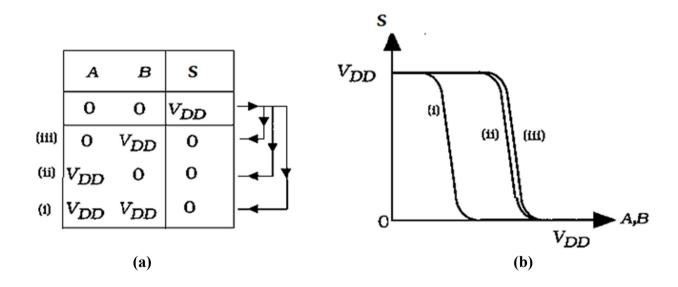

| Figure 2.25. Transition du signal de la porte NOR.                                     | 39 |

| Figure 2.26. Porte OR.                                                                 | 40 |

| Figure 3.1. Lancement d'un projet sur Cadence                                          | 43 |

| Figure 3.2. Fenêtre principale sur Cadence.                                            | 44 |

| Figure 3.3. Library Manager sur Cadence.                                               | 44 |

| Figure 3.4. Création d'une cellule sur Cadence                                         | 45 |

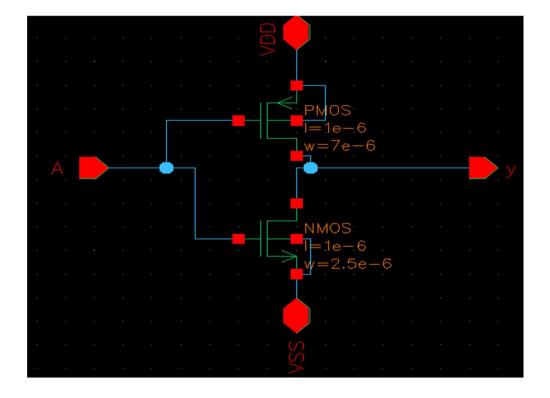

| Figure 3.5. Schéma d'inverseur sur Cadence                                             | 45 |

| Figure 3.6. Inverseur CMOS                                                             | 48 |

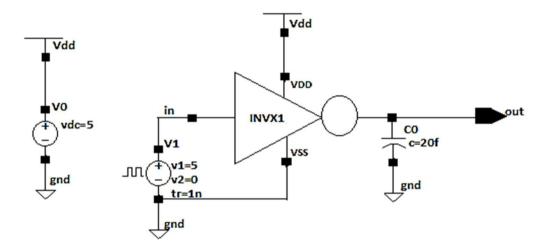

| Figure 3.7. Test bench                                                                 | 49 |

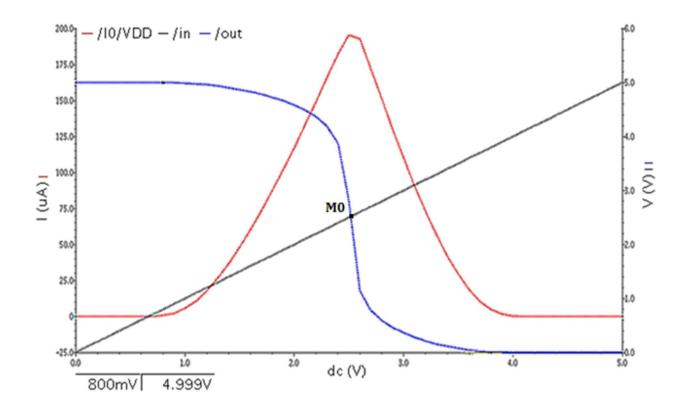

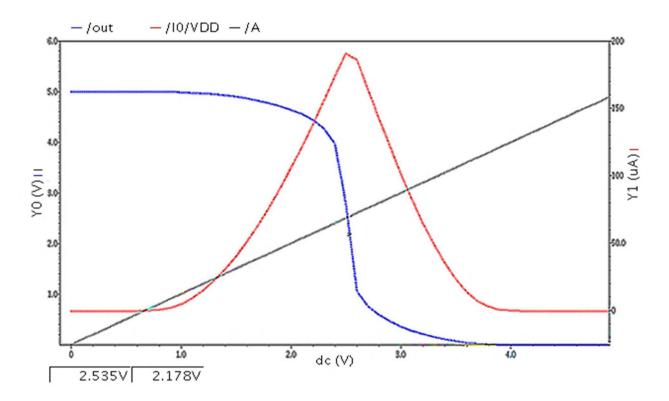

| Figure 3.8. Courbe de transfert de tension (VTC) de l'inverseurINV1XL                  | 50 |

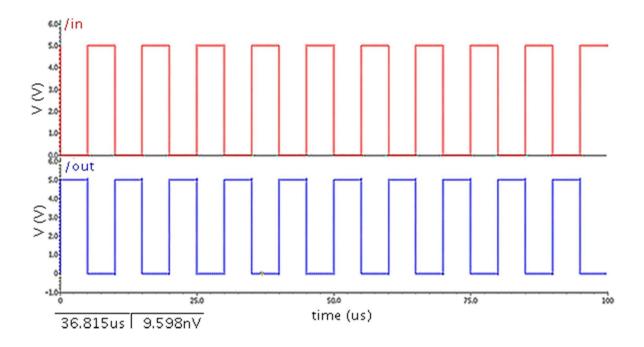

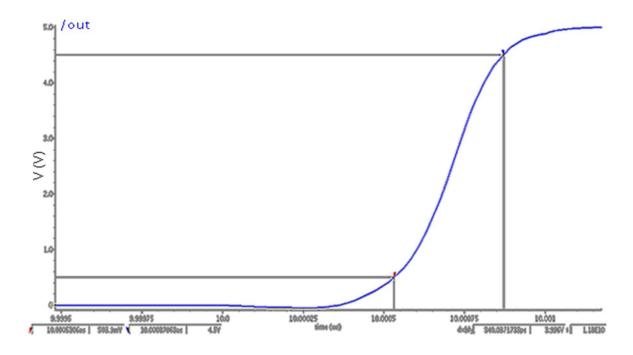

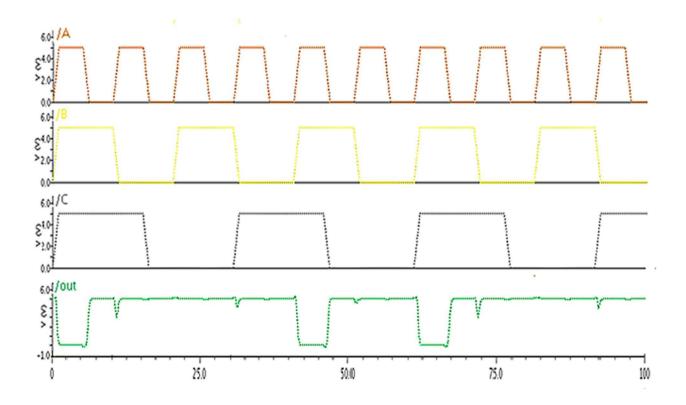

| Figure 3.9. Courbe de fonctionnement (INV1XL)                                          | 51 |

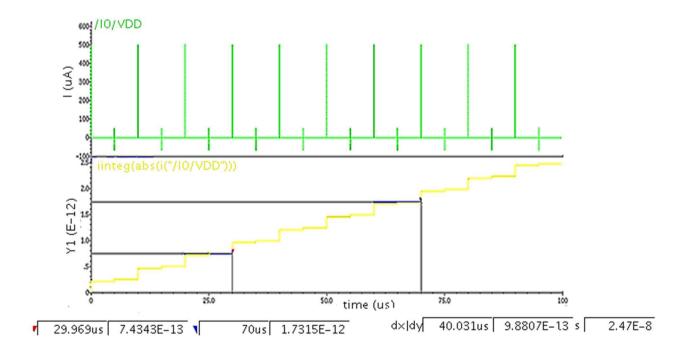

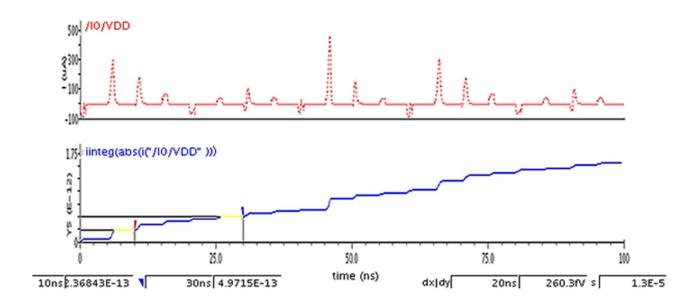

| Figure 3.10. Consommation de courant (INV1XL)                    | 51 |

|------------------------------------------------------------------|----|

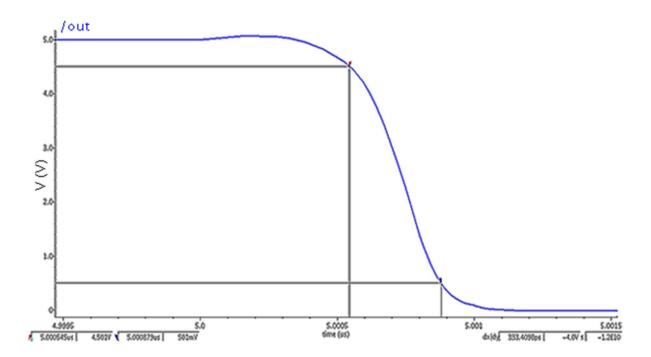

| Figure 3.11. Le temps de la descente td (falling time)           | 52 |

| Figure 3.12. Le temps de la montée tm (rising time)              | 53 |

| Figure 3.13. Le temps de propagation à la montée                 | 53 |

| Figure 3.14. Le temps de propagation à la descente               | 54 |

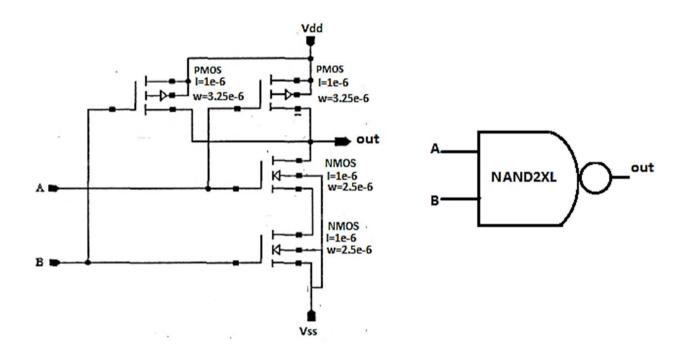

| Figure 3.15. Schéma électrique et le symbole de la porte NAND2XL | 57 |

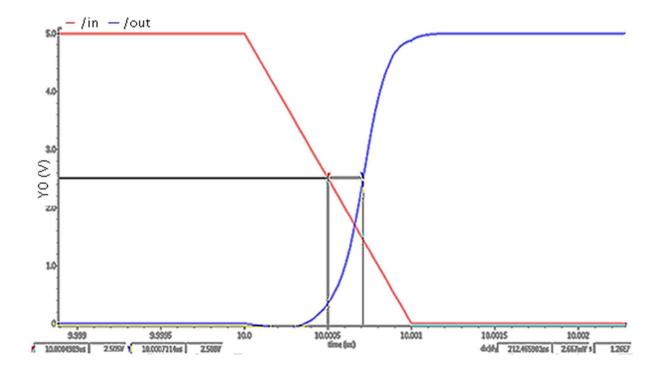

| Figure 3.16. Les courbes de transfert de tension (NAND2XL)       | 58 |

| Figure 3.17. Courbes de fonctionnement de la porte NAND2XL       | 58 |

| Figure 3.18. Consommation de courant(NAND2XL)                    | 59 |

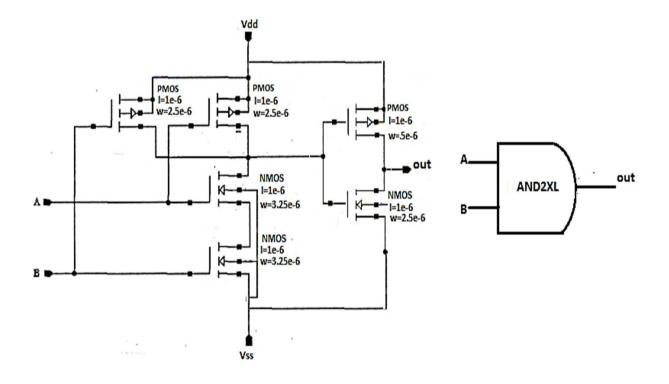

| Figure 3.19. Schéma électrique et le symbole de la porte AND2XL  | 60 |

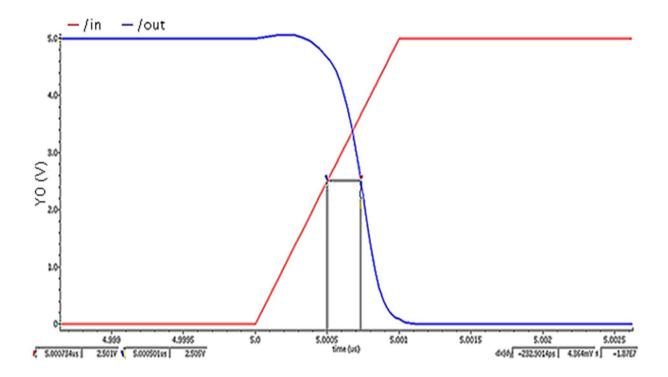

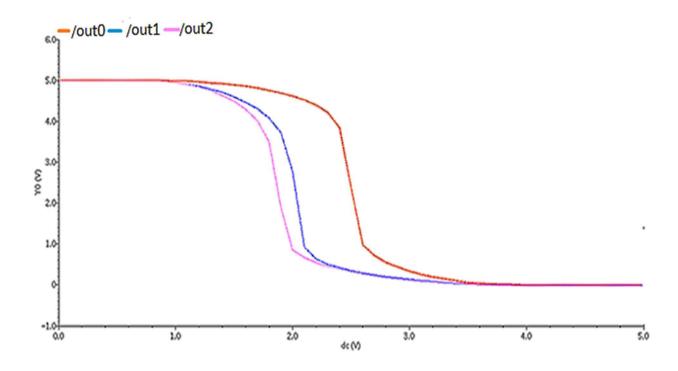

| Figure 3.20. Les courbes de transfert de tension (AND2XL)        | 61 |

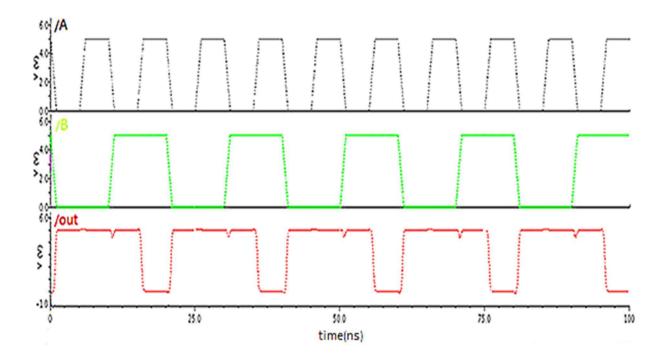

| Figure 3.21. Courbes de fonctionnement de la porte AND2XL        | 61 |

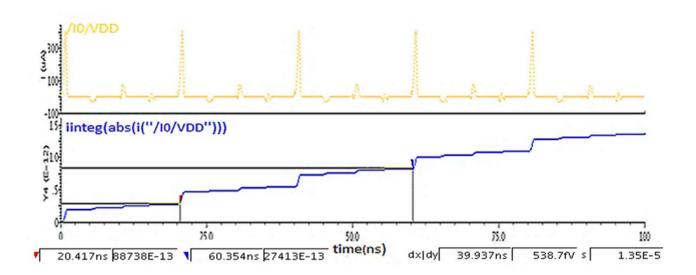

| Figure 3.22. Consommation de courant(AND2XL)                     | 62 |

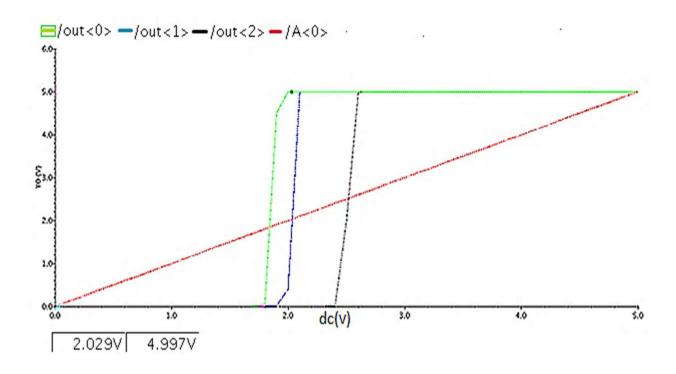

| Figure 3.23. Schéma électrique et le symbole de la porte NOR2XL  | 63 |

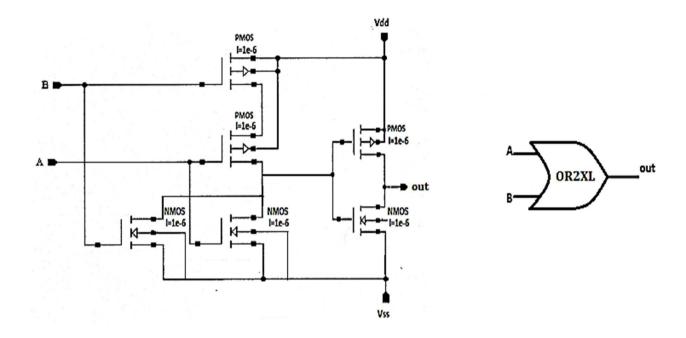

| Figure 3.24. Schéma électrique et le symbole de la porte OR2XL   | 65 |

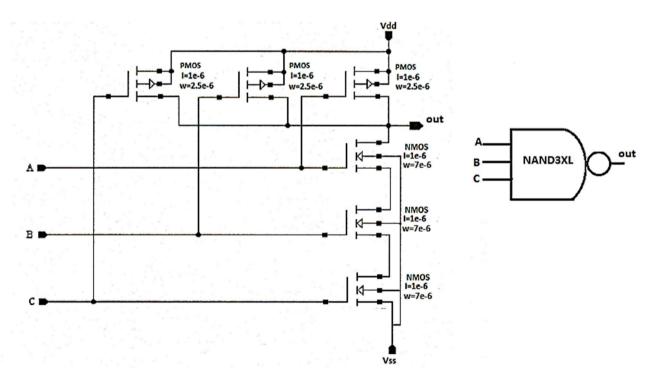

| Figure 3.25. Schéma électrique et le symbole de la porte NAND3XL | 66 |

| Figure 3.26. Courbe de transfert de tension (NAND3XL)            | 67 |

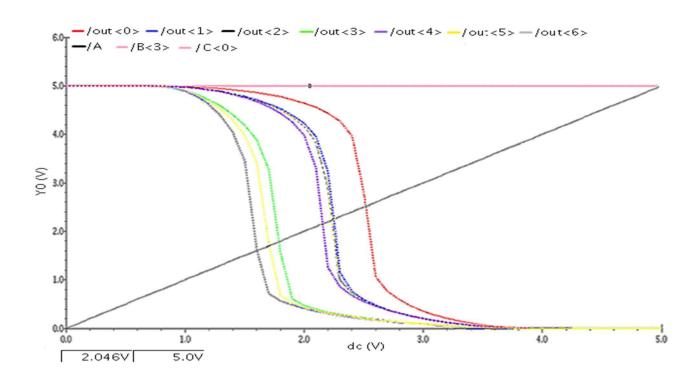

| Figure 3.27. Les courbes de transfert de tension (NAND3XL)       | 68 |

| Figure 3.28. Courbes de fonctionnement de la porte NAND3XL       | 68 |

| Figure 3.29. Consommation de courant(NAND3XL)                    | 69 |

| Figure 3.30.Les étapes des dessins des masques                   | 70 |

#### Listes des figures

| Figure 3.31.Loi des dessins de masque des différentes couches (active, poly-silicium, métal des |    |

|-------------------------------------------------------------------------------------------------|----|

| contacts)                                                                                       | 76 |

| Figure 3.32.La grille utilisée dans les Layout.                                                 | 77 |

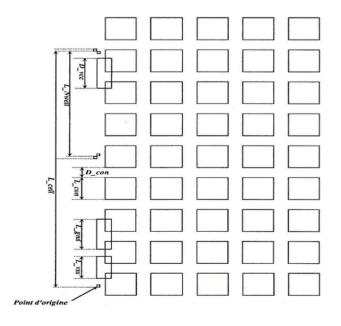

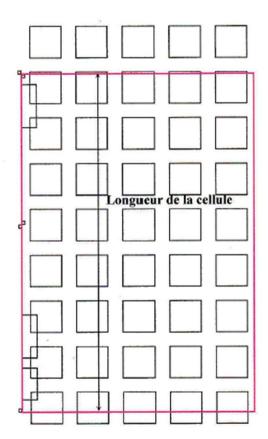

| Figure 3.33.Les limites de la cellule.                                                          | 78 |

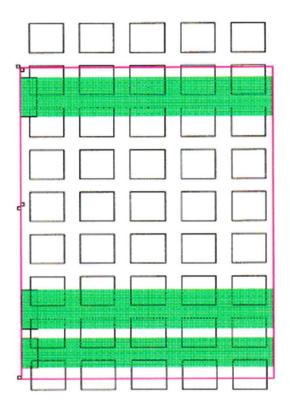

| Figure 3.34.Dessin des rails d'alimentation.                                                    | 79 |

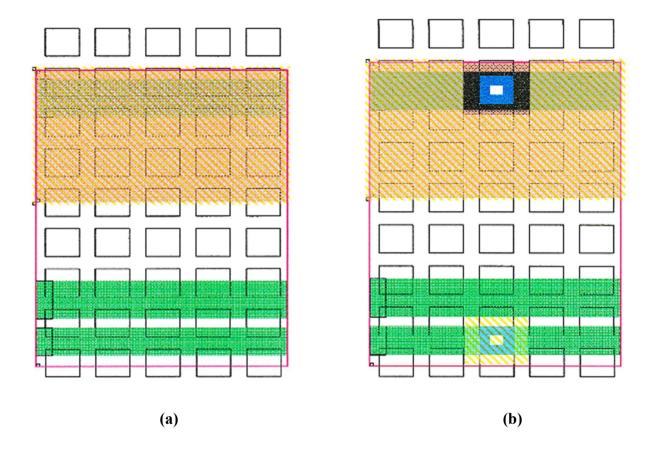

| Figure 3.35.Dessin des couches NWELL                                                            | 80 |

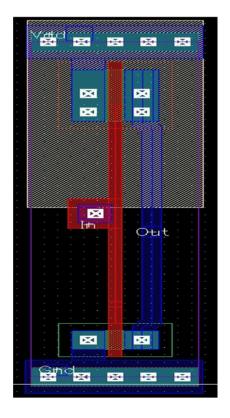

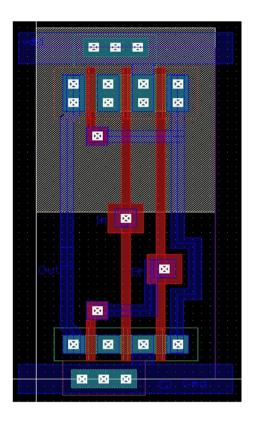

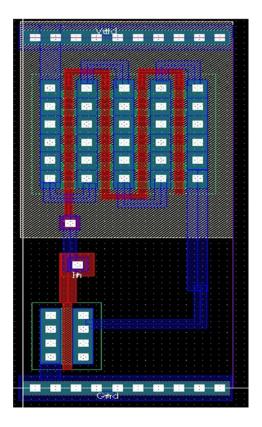

| Figure 3.36.Layout de l'inverseur INV1XL                                                        | 80 |

| Figure 3.37. Layout de l'inverseur INV3XL                                                       | 81 |

| Figure 3.38Layout de l'inverseur INV4XL                                                         | 81 |

| Tableau 2.1. Table de vérité d'un inverseur                                                   | 24  |

|-----------------------------------------------------------------------------------------------|-----|

| Tableau 3.1.Les caractéristiques d'inverseur INV1XL (fréquence 100 Hz)                        | 55  |

| Tableau 3.2. Les caractéristiques d'inverseur INV1XL (fréquence 100 MHz)                      | 56  |

| Tableau 3.3. Les caractéristiques de la porte NAND2XL                                         | 59  |

| Tableau 3.4. Les caractéristiques de la porte AND2XL                                          | 62  |

| Tableau 3.5. Les caractéristiques de la porte NOR2XL                                          | 64  |

| Tableau 3.6. Les caractéristiques de la porte OR2XL                                           | 65  |

| Tableau 3.7. Les caractéristiques de la porte NAND3XL                                         | 69  |

| Tableau 3.8. Représentation en couleur des différentes couches utilisées par Vertuoso cadence | e74 |

# Introduction générale

#### **Avant-propos**

Le domaine de la micro-électronique a connu un développement technologique sans pareil ces dernières années. Ainsi sont aujourd'hui intégrés sur une seule puce des systèmes électroniques réalisés auparavant sous forme de cartes. Cette tendance à l'intégration et à la miniaturisation des circuits est portée par le développement "explosif des applications multimédia, de télécommunications et automobiles. De tels systèmes comportent un nombre toujours croissant de modules pouvant appartenir à des domaines différents: des fonction numériques, prédominantes, qui sont fondées sur des microprocesseurs ou micro-contrôleurs, des mémoires et des blocs DSP de traitement de signal ("Digital Signal Processing"), mais aussi des fonctions analogiques d'amplification et de filtrage qui se trouvent en particulier dans les circuits de conversion analogique/numérique (CAN) en entrée, et numérique/analogique (CNA) en sortie.

Durant ces dernières années, beaucoup d'efforts ont été consacrés à la consommation des systèmes CMOS mixtes analogiques/numériques. Cela est dû principalement à la réduction de la taille des circuits intégrés. Les conséquences de ces réductions sont différentes selon la nature des circuits.

D'un côté, les circuits intégrés numériques peuvent facilement atteindre des qualités excellentes du point de vue fonctionnement (par exemple une très grande résolution et un bon rapport signal sur bruit).

De plus, la taille de la partie numérique est réduite radicalement avec la minimisation des tailles des blocs fonctionnelles.

D'un autre côté, les circuits intégrés analogiques avec de bonnes fonctionnalités sont très difficiles à réaliser. Par ailleurs, les circuits intégrés analogiques ne peuvent pas être conçus en utilisant des tailles minimales des transistors. La surface de la partie analogique ne peut donc pas être réduite radicalement avec la minimisation des tailles des fonctions à réaliser.

Bien que plusieurs parties analogiques puissent être remplacées par des parties numériques, la nécessité des circuits analogiques reste assez importante. Le monde réel étant analogique, il y aura en effet toujours besoin de convertisseurs pour convertir les données numériques des dispositifs électroniques en signal analogique (ex: signal audio) perceptible par l'homme.

D'autre part, les circuits intégrés analogiques peuvent réaliser des fonctions à haute fréquence (Radio Fréquence) contrairement aux circuits numériques. Les senseurs, les transmetteurs, les récepteurs sont ainsi souvent des composants analogiques.

La réalisation des éléments de la bibliothèque standard regroupant toutes les portes logiques qui peuvent être intervenir lors de la conception de la partie digitale d'un circuit intégré. Cette bibliothèque contient des cellules standard simples et complexes.

Les tests et les résultats dans ce projet se fait dans le centre de développement des technologies avancées (CDTA) de Baba Hassen, Algérie.

#### Plan de la thèse

La thèse est répartit sur trois chapitres. Dans le premier chapitre, on a donné des généralités sur les applications spécifiques (ASIC), ainsi que la fabrication des transistors CMOS, ainsi que le circuit CMOS dans le silicium, ainsi que les caractéristiques et les critères de sélection. Le deuxième chapitre résume l'étude théorique des portes logiques, dans ce chapitre, on a exposé un bref rappel théorique sur le transistor MOS, les différents temps caractérisant une porte logique et la conception CMOS des éléments essentiels d'une bibliothèque logique. Le troisième chapitre résume l'étude pratique des portes logiques, dans ce chapitre, on a donné les différents tests et résultats effectués (analyse DC et transitoire, courbe de transfert de tension, consommation du courant et timing simulation, Layout sur quelques cellules).

# **Chapitre 1**

### Conception des circuits intégrés

- 1.1 Introduction

- 1.2 Les ASICs (Application Spécifie Integrated Circuit)

- 1.3 Opérations élémentaires pour la fabrication des transistors CMOS

- 1.4 Circuit CMOS dans le silicium

- 1.5 Caractéristiques importantes et critères de sélection

- 1.6 Conclusion

#### 1.1. Introduction

Les progrès technologiques continus dans le domaine des circuits intégrés ont permis la réduction des coûts, de la consommation, et c'est maintenant un lieu commun d'affirmer que les circuits intégrés d'une application spécifiques ont permis une réduction de la taille des systèmes numériques ainsi que la réalisation de circuits de plus en plus complexes, tout en améliorant leurs performances et leur fiabilité. Ce chapitre va introduire les connaissances élémentaires ainsi que des règles et techniques qui pourront être utilisé dans la conception

#### 1.2. Les ASICs (Application Spécifie Integrated Circuit)

Les circuits ASIC constituent la troisième génération de circuits intégrés qui a vu le jour au début des années 80. En comparaison des circuits intégrés standards et figés proposés par les fabricants (IC TTL 7400), l'ASIC présente une personnalisation de son fonctionnement, selon l'utilisation, accompagnée d'une augmentation de la densité d'intégration et de la vitesse de fonctionnement. En outre sa personnalisation lui confère un autre avantage industriel, c'est évidemment la confidentialité. Ce concept d'abord développé autour du silicium s'est ensuite étendu à d'autres matériaux pour les applications micro-ondes ou très rapides (GaAs par exemple). [1]

#### 1.2.1. Définition

Les circuits ASIC regroupent tous les circuits dont la fonction peut être personnalisée d'une manière ou d'une autre en vue d'une application spécifique, par opposition aux circuits standards dont la fonction est définie et parfaitement décrite dans le catalogue de composants. Les ASIC peuvent être classés en plusieurs catégories selon leur niveau d'intégration, en fait un ASIC est défini par sa structure de base. [2]

#### 1.2.2. Méthode de conception

Les méthodes efficaces de conception d'ASICs reposent sur la méthodologie descendante « top down ». Cette méthodologie peut se considérer comme une « boite à outils » dans laquelle le concepteur trouve une variété d'outil approprié : modèles, solutions, méthodes. Reste au concepteur à trouver pour chaque situation l'outil approprié pour une résolution efficace de son problème.

#### ✓ La méthode descendante « top-down » [4] [5]

Cette approche est la méthode la plus populaire parmi les concepteurs des circuits intégrés ASICs. Par ailleurs, c'est une méthode « générique »ou les approches de conception viennent s'imbriquer.

L'approche descendante part du système en circuits puis sous circuits et évolue ainsi jusqu'au schéma composé de transistors. La méthode de conception descendante peut être définie comme suit :

✓ Le niveau système ou spécification système (system level en anglais)

A ce niveau, aucune architecture et séquencement des opérations ne sont définis.

✓ Le niveau comportemental et algorithmique

A ce niveau, le circuit est spécifié en terme de pas de calcul, sépare par des points de synchronisation ou des lectures/écritures des entrées/sorties.

✓ Le niveau transfert de registre (RTL)

A ce niveau, les opérateurs sont associés aux composants de librairie, les variables aux points mémoires pour obtenir une représentation en transfert de registre.

#### ✓ Le niveau physique

C'est le niveau le plus bas, il prend en considération les informations électriques du système, il possède le plus haut degré de précision dans le modèle.

Par ailleurs pour compléter le flot de la méthode descendante, il faut ajouter des étapes de validations.

#### 1.2.3. Avantages et inconvénients de l'utilisation d'ASIC

D'une manière générale l'utilisation d'un ASIC conduit à de nombreux avantages provenant essentiellement de la réduction de la taille des systèmes. Il en y sort :

✓ Réduction du nombre de composants sur le circuit imprimé. La consommation

et l'encombrement s'en trouvent considérablement réduits.

- ✓ Le concept ASIC par définition assure une optimisation maximale du circuit à réaliser. Nous disposons alors d'un circuit intégré correspondant réellement à nos propres besoins.

- ✓ La personnalisation du circuit donne une confidentialité au concepteur et une protection industrielle.

- ✓ Ce type de composant augmente la complexité du circuit, sa vitesse de fonctionnement et sa fiabilité.

L'inconvénient majeur réside dans le fait du passage obligatoire chez le fondeur ce qui implique des frais de développement élevés du circuit. En général le fondeur ne souhaite pas intervenir dans la phase de conception ; sa tâche est de réaliser le composant à partir des masques. Dans le but de réduire les surcoûts dus aux modifications, il s'avère nécessaire d'être rigoureux lors de la phase de développement de telle sorte que le circuit prototype fonctionne dès les premiers essais. [3][2]

#### 13. Operations élémentaires pour la fabrication des transistors CMOS

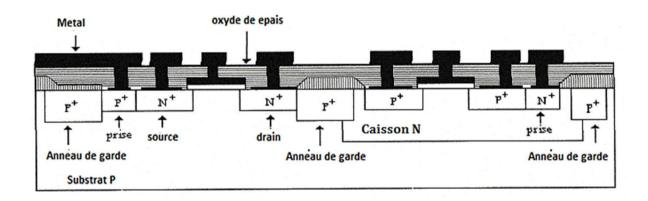

Une structure CMOS (Complementary Metal Oxyde Semi-conductor) composée d'un transistor de type P et d'un transistor de type N, est la superposition de différentes zones conductrices ou isolantes, crées a partir 1'application des différents précédés physiques et chimiques dans un ordre parfaitement établi: [6][7]

- ✓ Une fine couche de protection d'oxyde de silicium est déposée sur un substrat de type P (figure 1.1.a1).

- ✓ Le caisson N est diffuse (figure 1.1.a2).

a1. Oxydation

a2.Implantation du caisson N

Fig. (1.1). Réalisation du caisson N sur le substrat

✓ Les anneaux de garde séparant électriquement les transistors sont implantes (figure 1.2). Ceux-ci seront par la suite reliés au potentiel électrique le plus bas du circuit. Cette étape est suivie d'un dépôt d'oxyde épais.

Fig. (1.2). Fabrication des anneaux de garde et champ d'oxyde épais

Les grilles de silicium polycristallin sont déposées et les diffusions de type N sont implantées (figure 1.3). Ces grilles servant de masques, leur autoalignement sur la structure canal-source-drain est assure, on minimise ainsi le recouvrement grille-drain et grille-source générateur de capacité parasite structurelle. La prise de caisson, fortement dopée, en diminuant la résistance de contact permet de se prémunir contre le phénomène de latch-up.

Fig. (1.3). Fabrication des grilles poly-cristallines et des diffusions N

✓ Les diffusions de type P sont implantées (figure 1.4).

Fig. (1.4). Diffusions P

✓ Un premier niveau d'interconnexion (aluminium ou cuivre) est réalisé après isolation par une couche d'oxyde épais (quelques 0,1 ( $\mu$ m). Eventuellement les autres niveaux d'interconnexion métalliques sont ensuite successivement réalisés (figure 1.5).

Fig. (1.5). Premier niveau d'interconnexion

✓ L'étape finale de passivation complète du circuit est effectuée. Cette couche de protection est ensuite ouverte pour réaliser les connexions avec 1'extérieur (c'est le "packaging").

**Remarque :** Les étapes précédentes résument la fabrication d'un doublé de transistor NMOS et PMOS.

#### 1.4. Circuit CMOS dans le Silicium

Le masque optique est la composante principale de la fabrication .Il définit les motifs qui vont produire les différents éléments sur le circuit. Il y a donc des règles quant aux dimensions minimales et la séparation entre les éléments.

#### 1.4.1. Règles de dessin

Le processus de fabrication des circuits intégrés est sensible aux diverses dispersions spatiales. Les motifs issus du processus de fabrication différent de ceux dessinés sur masques et peuvent alors conduire au dysfonctionnement du circuit [8].

Ces différences sont principalement issues :

- ✓ Du désalignement des masques, plusieurs niveaux de masques sont superposes successivement avec une précision finie, le débordement (overlay) est aujourd'hui de 1'ordre de quelques dizaines de nanomètres entre deux niveaux de masques.

- ✓ De la tolérance des précèdes de photolithographie et gravure.

- ✓ De la diffusion des espèces implantées, notamment la diffusion latérale, qui, naturellement, change les distances entre jonctions par rapport à leurs distances sur masques.

Pour prévenir, l'apparition de structures géométriquement déformées, trop petites ou électriquement dangereuses, on définit, pour chaque technologie, un jeu (plusieurs dizaines, voire quelques centaines) de règles de dessin, qui précisent les dimensions et espaces minimaux et qui excluent les configurations interdites. [8]

L'importance des règles de dessin réside principalement dans les trois points suivants:

- ✓ Elles éliminent (ou réduisent fortement) le risque de dysfonctionnement du circuit, conduisant ainsi à des rendements de fabrication plus élevés.

- ✓ Elles permettent aux concepteurs, en définissant clairement les dimensions minimales, de prendre sans risque l'avantage des performances accrues pour de petits dispositifs.

- ✓ Elles sont la clef pour l'automatisation du processus de conception et de vérification du dessin, permettant ainsi de diminuer le cout de la conception et d'éviter de

nombreuses erreurs qui peuvent apparaître au cours de la conception de circuits complexes.

#### 1.4.2. Paramètres électriques

La fiabilité de la conception des circuits intégrés et la rapidité de la mise sur le marché des nouveaux circuits reposent sur la précision de la simulation électrique de leur fonctionnement. Cela permet d'atteindre avec exactitude la fonctionnalité voulue du circuit et d'éliminer les erreurs avant d'entrer en phase de fabrication.

La précision de la simulation est fonction de la qualité des modèles utilises et de la justesse des paramètres électriques spécifiques a la technologie de fabrication. Du fait de leur complexité, les modèles de composants électriques présentent des jeux de paramètres qui leur sont spécifiques. Le fabricant fournit, en général, les valeurs des paramètres électriques de sa technologie, relatives aux modèles standard utilises par les concepteurs.

Un modèle de base n'utilise qu'une dizaine de paramètres électriques, mais les modèles actuels en ont plusieurs dizaines (voire une centaine). C'est le résultat de nombreux effets correcteurs implémentes dans les modèles, qui sont indispensables pour simuler avec précision des circuits fabriques en technologie avancée. L'acquisition des valeurs des paramètres, vu leur nombre et leurs corrélations internes, peut être une tache très difficile, on peut énumérer trois approches principales a ce problème. [9] [10]

- Optimisation globale: un logiciel d'optimisation ajuste les valeurs des paramètres ayant pour critère la minimisation de l'écart par rapport aux caractéristiques électriques mesurées sur les dispositifs issus de la technologie en question. Du fait des corrélations entre certains paramètres, il y a souvent des compensations d'erreurs, au prix de valeurs non physiques de ces paramètres. L'autre inconvénient majeur est la puissance de calcul : vu le nombre de paramètres entrant en jeu, les capacités de calcul des ordinateurs peuvent être vite dépassées.

- ✓ **Optimisation locale :** on décompose le processus d'optimisation en une séquence d'étapes, dont chacune n'ajuste que quelques paramètres par rapport à un sousensemble de caractéristiques particulièrement sensibles aux valeurs des paramètres sélectionnés. On y gagne sur les deux fronts : la puissance de calcul devient abordable et le sens physique des paramètres est mieux préservé.

✓ Extraction directe: les procédures d'extraction directe pour chaque paramètre sont fournies avec le modèle : elles précisent les structures de tests, les mesures et calculs à effectuer pour établir la valeur du paramètre donné. C'est la méthode la plus rapide et assurant le mieux, le sens physique des paramètres, mais elle demande un investissement de départ pour l'élaboration des procédures d'extraction ; cela n'est d'ailleurs possibles qu'avec des modèles bien conçus et ayant eux-mêmes u sens physique des équations.

#### 1.4.3. Dispersion de paramètre

Différents types de dispersions peuvent intervenir au cours de la fabrication des circuits intégrés : dispersion en dimensions latérales, en dimensions verticales ou en concentration de dopants. La plus critique est certainement la dispersion de la longueur du canal.

Une dispersion  $\partial L$  de la longueur du transistor peut être tolérable vis-à-vis des transistors relativement longs, car elle n'implique pas de réduction de  $V_{th}$  et donc n'influence pas ou peu les caractéristiques du MOS. Concernant les transistors cours, une même dispersion  $\partial L$  est plus critique, car, à travers  $V_{th}$  elle peut conduire a des variations inacceptables des caractéristiques de sortie et sous le seuil. [10]

#### 1.4.4. Protection des entrées/sorties

En règle générale les entrées des circuits MOS sont connectées aux grilles des transistors MOS, qui représentent des capacités relativement faibles de l'ordre du femto-farad (10-15f). En autre, les oxyde de grille très minces, de l'ordre de quelques nanomètres ,ne supportent pas des tension supérieures de 5 à 10V. Cela implique que des charges aussi faibles que quelque femto-coulombs peuvent conduire au claquage de l'oxyde, sachant que les charges électrostatiques dont nous sommes porteurs (charges issues de frottement et d'autres phénomènes électrostatiques) peuvent largement dépasser le seuil de quelques femto-coulombs.

II en résulte que les circuits MOS sont très sensibles aux charges électrostatiques, une manipulation inattentive peut conduire à leur destruction. Afin de prévenir cet inconvénient, on implémente des circuits de protection aux entrées des circuits MOS. II est aussi de bon usage de les manipuler en utilisant des bracelets qui, par un fil conducteur, écoulent les charges électrostatiques à la terre. [10]

#### 1.5. Caractéristiques importantes et critères de sélection

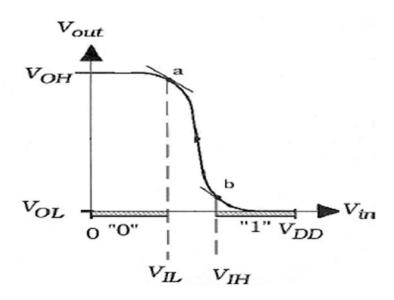

#### 1.5.1. Caractéristiques de transfert

La caractéristique de transfert en tension ne peut pas être fixée absolument pour un type de circuit donné. On spécifie cette donnée sous forme detolérances :

Fig. (1.6): Caractéristiques de transfert

Tensions d'entrée

$V_{IL}$ : Tension maximale reconnue comme un 0.

V<sub>IH</sub>: Tension minimale reconnue comme un 1.

Tensions de sortie

$V_{OL}$ : Tension maximale garantie pour un 0.

V<sub>OH</sub>: Tension minimale garantie pour un 1.

Chapitre 1: Conception des circuits intégrés

11

1.5.2. Marges de bruit

Comme la sortie d'un circuit logique est souvent connectée a l'entrée d'un autre, deux

grandeurs pertinentes sont la marge de bruit et la marge de tension parasite que

Marge de bruit pour le niveau haut :  $\Delta V_H = V_{OH} - V_{IH}$

Marge de bruit pour le niveau bas :  $\Delta V_L = V_{OL} - V_{IL}$

Ces marges de bruit sont bien sur spécifiées pour des familles logiques, avec des

tensions d'alimentation. L'interfaçage de différents familles logiques ne peut donner se faire

sans précautions particulières quant à ces marges, et plus généralement quant à l'ensemble

des caractéristiques des familles concernées.

1.5.3. Fan-in et fan-out

Pour un circuit donné, le fabricant spécifié le nombre de circuits du même type que l'on

peut placer en amont et en aval, sans détériorer les performances du système :

Fan-in: nombre maximum de portes pouvant débiter dans le circuit.

Fan-out: nombre maximum de portes pouvant charger le circuit.

1.5.4. Puissance dissipée

Que ce soit pour les circuits logiques ou analogiques, intégrés ou pas, la puissance

dissipée est toujours un paramètre important. L'alimentation des circuits doit être capable de

débiter le courant nécessaire.

1.5.5. Délais de propagation par porte

Le signal de sortie d'une porte logique accuse un certain retard par rapport à la

transition du signal d'entrée. Ce retard est lie à divers phénomènes dynamiques, et les

fabricants spécifient les délais de propagation en mesurant les signaux à mi- tension.

1.5.6. Produit puissance-délai

Au sein d'une famille logique, on peut dans certaines limites, concevoir des circuits à

faible délai au prix d'une consommation élevée ou réciproquement on peut diminuer leur consommation, si on se contente de rapidités moindres.

Remarquons que l'apparition de ce type de compromis est typique en électronique, où des impédances de sortie plutôt résistives se combinent avec des capacités parasites peu contrôlées : si on diminue la résistance de sortie R, le produit RC diminue, donc la rapidité du circuit augmente. Cela peut néanmoins se faire par le biais d'une augmentation de courant, donc de consommation.

#### 1.6. Conclusion

Dans ce chapitre, nous avant exposé, en premier lieu, la méthode de conception des circuits intégrés ASICs, et le processus de fabrication CMOS (transistors NMOS et PMOS sur le même substrat). Puis nous avant cité les paramètres à tenir en compte pendant la conception des circuits intégrés. Enfin, nous avant donné les caractéristiques et les critères de sélection des circuits logiques CMOS

# **Chapitre 2**

## Etude théorique des portes logiques

- 2.1 Introduction

- 2.2 Rappel théorique sur les transistors MOS

- 2.3 Inverseur CMOS

- 2.4 Portes logiques de base

- 2.5 Conclusion

#### 2. 1. Introduction

Aujourd'hui, la technologie CMOS est la technologie dominante pour la fabrication des circuits intégrés par rapport aux autres technologies, essentiellement bipolaire, Bicmos, c'est principalement parce qu'elle possède deux avantages : sa faible consommation et sa densité d'intégration qui ne cesse de croître, puisqu'en trente ans la longueur minimum des transistors a été divisée par un facteur supérieur à cent.

#### 2.2. Rappel théorique sur les transistors MOS [11] [12]

Le transistor MOS est le composant le plus employé de nos jours. Le Transistor à Effet de Champ Métal Semi-conducteur (MOSFET : Métal Oxyde Semi-conducteur Field Effect Transistor) à sa grille isolée du canal par une couche de dioxyde de silicium (SiO<sub>2</sub>). Le transistor MOS possède 4 électrodes : la Source (*Source*) S: point de départ des porteurs, le Drain (*Drain*) D : point de collecte des porteurs. La Grille (*Gate*) G et le Substrat (*Body*) B sont les électrodes de la capacité MOS qui contrôle le nombre de porteurs présents dans le canal.

L'intensité du courant circulant entre la source et le drain est commandée par la tension entre la grille du substrat. Très souvent les électrodes de source et de substrat sont électriquement reliées, on retrouve un composant à 3 électrodes dans lequel la courant entre le **D**rain et la **S**ource  $I_{DS}$  est commandé par une tension entre la **G**rille et la **S**ource (potentiel de source = potentiel de substrat) :  $V_{GS}$ .

Dans chaque type de MOSFET, on peut distinguer le MOSFET canal N (le courant provient du déplacement d'électrons) et le MOSFET canal P (le courant provient du déplacement de trous).

L'étude du transistor se fait dans le cas d'un MOS à canal N (NMOS), qui est le plus fréquent; le canal P a un fonctionnement identique en inversant les polarisations.

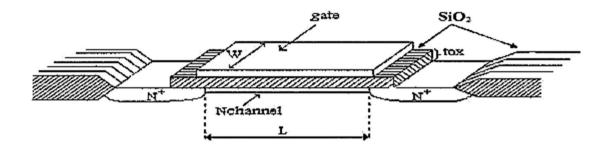

#### 2.2.1. Les dimensions importantes dans un MOS

Les transistors mos sont définis par leurs dimensions :

L: Longueur du canal, son minimum est défini par la technologie.

W: Largeur du canal.

t<sub>ox</sub>: L'épaisseur de l'oxyde.

Fig. (2.1): Dimensions dans un MOS

#### 2.2.2. Régimes de fonctionnement du transistor MOS

Le transistor MOS possède des régimes de fonctionnement différent sont :

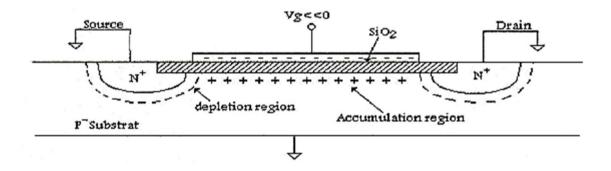

#### a. Le régime bloqué

Le transistor NMOS se comporte comme un interrupteur ouvert (bloqué) lorsque  $V_{GS} \le V_{th}(I_D=0)$ Lorsque la tension de grille est très inférieur à zéro ( $V_G << 0$ ), il y a création d'une zone d'accumulation des trous ( $p^+$ ) sous l'isolant, deux diodes PN polarisées en inverse, aucun courant ne circule entre le drain et la source.(fig.2.2)

Fig. (2.2): Le MOS en régime de blocage

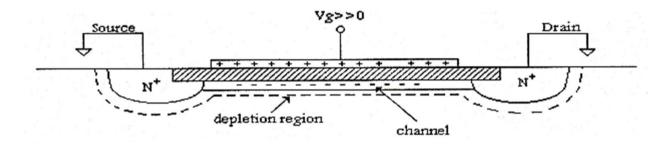

#### ✓ Condition de création du canal N

La Création du canal N se fait lorsque la tension de grille  $V_G$  est supérieure  $V_{th}/2$ .

V<sub>th</sub> (threshold voltage): Potentiel de grille pour lequel la densité de charge apportée sous la grille est le

double de la densité de charge du dopant à V<sub>G</sub>=0V (au-dessous de l'isolant).

#### ✓ Formation du canal du transistor NMOS

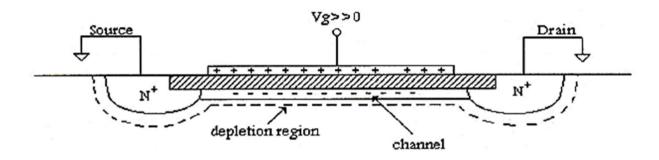

Lorsque  $V_G \gg 0$  et  $V_G \neq V_{th}$ , il y a création d'un canal N sous la grille, les électrons fournis par la source et le drain peuvent circuler librement, il y a création d'un courant entre la source et le drain.( Fig.2.3)

Fig. (2.3): Formation du canal en dessous de la grille

#### b. Le régime linéaire (ohmique)

Dans certaines conditions, le MOSFET se comporte comme une résistance, dont la valeur dépend de  $V_{GS}$ .

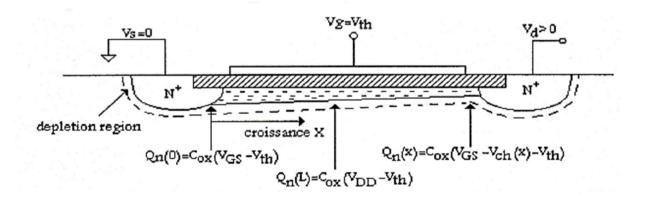

Lorsque  $V_G > V_{th}$  et  $V_D > 0$ : transistor en régime ohmique (Variation de la densité de charge le long du canal). La condition du régime ohmique est  $V_{GS} > V_{th}$  et  $V_{DS} < V_{GS} - V_{th}$ . (fig.2.4)

Fig. (2.4): Distribution des charges en régime ohmique

#### c. Le régime de saturation

Dans certaines conditions, le NMOS se comporte comme un générateur de courant commandé en tension  $V_{GS}$ .

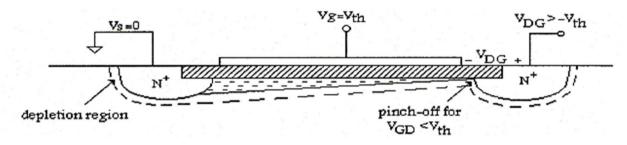

Lorsque  $V_G < V_{th}$  et  $V_D \gg 0$ , il y a pincement du canal, en première approximation, la densité de courant dans le canal reste constante et le courant ne croit plus avec  $V_{DS}$ . Condition du régime de saturation:  $V_{GS} > V_{th}$  et  $V_{DS} > V_{GS}$ - $V_{th}$ . (fig.2.5)

Fig. (2.5): Pincement du canal

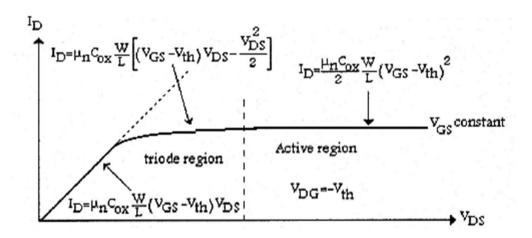

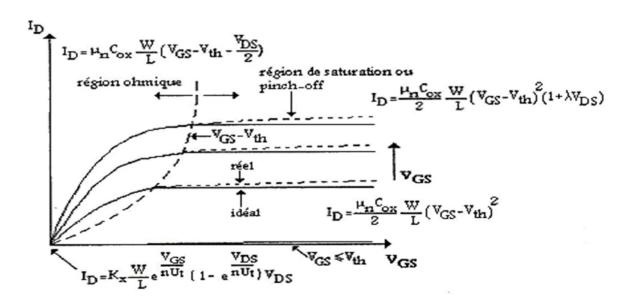

La figure (2.6) résume les régimes de fonctionnement du transistor NMOS et leurs équations de courants :

Fig. (2.6): L'expression du courant dans les régimes de conduction

$\mu_{n,p}$ : Mobilité des trous (ou des électrons). [cm<sup>2</sup>/v-sec]

$C_{OX} = \frac{t_{OX}}{\epsilon_{OX}}$ : Capacité d'oxyde. [F/cm<sup>2</sup>].

#### d. Le régime de forte saturation (effet de modulation du canal)

Pour  $V_{DS} = V_{GS} - V_{th}$ , appelé seuil de saturation, le champ généré au drain annule le champ crée

par le potentiel de grille. Il n y a plus de canal au niveau du drain, on dit qu'il y a pincement du canal. Lorsque le canal est pincé, la Longueur effective du canal diminue. La valeur du courant  $I_D$  est modulée par  $V_{DS}$ . (fig.2.7)

Fig. (2.7): L'effet de la modulation du canal

Pour tenir compte de cette modulation, on introduit le coefficient  $\lambda = \frac{1}{V_A}$

$$\text{avec} \;\; V_A = L_{eff} \left[ \frac{\partial X_d}{\partial V_{DS}} \right]^{-1} \text{et} \quad L_{eff} = L - X_d \quad (\; X_d \text{: La largeur de la zone de déplétion}).$$

L'équation du courant devient:

$$I_{D} = \frac{\mu_{n} C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^{2} [1 + \lambda (V_{DS} - V_{eff})]$$

Si  $V_{DS}$  continue à augmenter, il apparaît des effets de second ordre :

- ✓ Limitation de la vélocité, la vitesse des porteurs de charge n'augmente plus de manière linéaire avec le champ électrique.

- ✓ Saturation de la mobilité des porteurs.

#### e. Le régime de faible inversion

Pour  $V_{th}/2 < V_{GS} < V_{th}$ , le canal n'est pas complètement formé, mais un courant circule entre le drain et la source, c'est le régime de faible inversion. Le transistor MOS se comporte comme un transistor bipolaire:

$$I_{D} = K_{x} \left(\frac{W}{L}\right) e^{\frac{V_{GS}}{nU_{t}}} \left[1 - e^{\frac{V_{DS}}{nU_{t}}}\right]$$

U<sub>t</sub>: La constante kT/q.

$K_x$ : Dépend de la technologie et de  $U_t^2$ .

n: Coefficient de non idéalité.

Fig. (2.8): Régime de faible inversion

#### ✓ Le coefficient d'inversion

Il est important en conception analogique de connaître le régime de fonctionnement du transistor. Pour cela, on utilise le coefficient d'inversion  $I_C$  définit comme :

$$I_{C} = \frac{I_{D}}{2 K_{n} \frac{W}{I_{L}} U_{t}^{2}}$$

Si  $I_C \gg 1$ : régime de forte inversion.

Si  $I_C = 1$ : régime de moyenne inversion.

Si  $I_C \ll 1$ : régime de faible inversion.

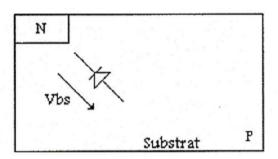

#### ✓ Effet du substrat

Le substrat peut avoir un impact sur la tension seuil.

Lorsque  $V_{bs}>0$ : Diode en directe, courant parasite important (détérioration du composant). Lorsque  $V_{bs}<0$ : Diode bloquée,  $V_{GS}$  est plus importante pour compenser l'effet du substrat. (fig.2.9)

Dans le cas où le substrat n'est pas au même potentiel que la source, $V_{th}$ est modifiée(effet de second ordre). On a :

$$V_{th} = V_{th0} + \gamma \left( \sqrt{V_{sb} + 2|\Phi_f|} - \sqrt{2|\Phi_f|} \right)$$

$\Phi_f$ : Tension de bande plate.

V<sub>th0</sub>: Tension de seuil à V<sub>sb</sub>=0 V (tension d'alimentation du substrat).

V<sub>sb</sub> La tension entre la source et le substrat.

$$\gamma = \frac{1}{C_{ox}} \sqrt{2qN_A \epsilon}$$

Fig. (2.9): Effet du substrat

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Fig. (2.10): Caractéristique du NMOS

#### 2.2.3. Modélisation du transistor MOS [11]

#### a. Modèles petits signaux en régime saturé

On distingue deux cas basses fréquences et hautes fréquences.

#### ✓ Basses fréquences

Elle permet de modéliser le comportement du MOS en présence de petites variations sur la source, la grille ou le drain. (figure2.11)

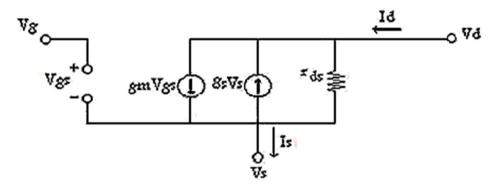

Fig. (2.11): Modèle petit signal a basse fréquence

$g_m$  (Transconductance du transistor): Elle représente l'action des variations de  $V_{GS}$

$$g_{\rm m} = \frac{\partial I_{\rm ds}}{\partial V_{\rm gs}} = \mu_{\rm n} C_{\rm ox} \; \frac{W}{L} (V_{\rm GS} - V_{\rm th}) = \frac{2 I_{\rm DS}}{V_{\rm GS} - V_{\rm th}} = \sqrt{2 \mu_{\rm n} C_{\rm ox} \; \frac{W}{L} I_{\rm D}} \label{eq:gm}$$

La tension  $V_{bs}$  joue sur la valeur de la tension de seuil, on introduisant une deuxième transconductance dans les modèles petits signaux  $g_{mb}$ :

$$g_{mb} = \frac{\partial I_D}{V_{bs}} = \frac{\gamma g_m}{2\sqrt{V_{sb} + 2|\Phi_f|}}$$

$$V_{th} = V_{th0} + \gamma \left( \sqrt{V_{sb} + 2|\Phi_f|} - \sqrt{2|\Phi_f|} \right)$$

Généralement, le terme  $\frac{g_{mb}}{g_m}$  est important en pratique, typiquement il est compris entre 0.1 à 0.3.

La résistance de sortie de transistor :

$$\frac{1}{r_{ds}} = g_{ds} = \frac{\partial I_D}{\partial V_{DS}} = \lambda I_D$$

La résistance de sortie dépend des paramètres technologiques dont la valeur est mal contrôlée.

#### ✓ Hautes fréquences

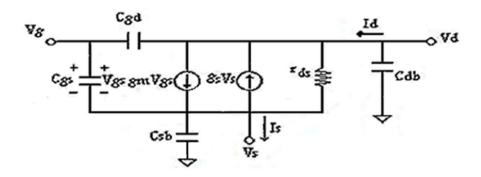

Fig. (2.12): Modèle petit signal à haute fréquence

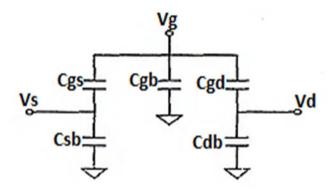

#### ✓ Capacité grille source

C'est la plus grande capacité. Elle est due à la variation de charge du canal du fait que la variation de V<sub>GS</sub>.

$$C_{gs} = \frac{2}{3} W L C_{ox}$$

Si on tient compte le recouvrement (OverLay) de la grille et de la source :

$$C_{gs} = \frac{2}{3} W C_{ox} \left( \frac{2}{3} L + L_{OV} \right)$$

#### ✓ Capacité source-substrat

C'est la deuxième plus grande capacité elle est due à la capacité de déplétion

$$C_{sb} = (A_s + A_{ch}) C_{js}$$

avec  $C_{js} = \frac{C_{j0}}{\sqrt{1 + \frac{V_{sb}}{\psi_0}}}$

Avec :  $A_s$  aire de la source,  $A_{ch}$  aire du canal.

C<sub>is</sub>: La jonction en inverse au niveau de la source.

## ✓ Capacité Grille-drain

Cette capacité est appelée aussi la capacité de MILLER. Elle est principalement due au chevauchement de la grille avec le drain.

$$C_{gd} = C_{ox} W L_{OV}$$

**Remarque :**  $C_{gs} + C_{gd} = Cte$  quel que soit le régime de conduction du transistor.

#### ✓ Capacité drain-substrat

Elle est due à la capacité de déplétion  $C_{jd}$  de la jonction en inverse au niveau du drain. Elle est plus petite que la capacité  $C_{sb}$  à cause du pincement du canal en régime de saturation.

$$C_{db} = A_d C_{jd}$$

avec  $C_{jd} = \frac{C_{j0}}{\sqrt{1 + \frac{V_{db}}{\psi_0}}}$

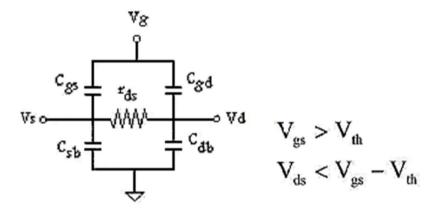

## b. Modélisation petits signaux en régime Ohmique

Le transistor est équivalent à une résistance commandée en tension

$$\frac{1}{r_{ds}} = g_{ds} = (V_{GS} - V_{th} - V_{DS})$$

Fig. (2.13): Modèle petit signal dans le régime ohmique

Les expressions suivantes donnent les différentes valeurs des capacités :

$$\begin{split} &C_{gs} = C_{gd} = \frac{A_{ch}C_{ox}}{2} = \frac{W \, L \, C_{ox}}{2} \\ &C_{sb} = \frac{C_{sb-0}}{\sqrt{1 + \frac{V_{sb}}{\psi_0}}} \quad \text{avec} \quad C_{sb-0} = C_{j0} \left( A_s + \frac{A_{ch}}{2} \right) \\ &C_{db} = \frac{C_{db-0}}{\sqrt{1 + \frac{V_{db}}{\psi_0}}} \quad \text{avec} \quad C_{db-0} = C_{j0} \left( A_d + \frac{A_{ch}}{2} \right) \end{split}$$

## c. Modélisation petits signaux en régime bloqué

On court-circuite généralement drain source et substrat pour utiliser le transistor comme capacité.

$C_{sb}$  et  $C_{db}$  sont négligeable, et  $C_{gs} = C_{gd} = W \ L_{OV} \ C_{ox}$

Fig. (2.14): Modèle petit signal dans le régime bloqué

## 2.3. Inverseur CMOS [10]

#### 2.3.1. Principe de fonctionnement

La fonction logique la plus simple est celle de l'inverseur. Elle peut être décrite par la table de vérité qui décrit l'état de sortie (OUT) en fonction de l'état d'entrée (IN) (table2.1). La figure (2.15) présente le symbole et l'implémentation de la fonction inverseur en technologies CMOS.

| IN | OUT |  |  |

|----|-----|--|--|

| 0  | 1   |  |  |

| 1  | 0   |  |  |

|    |     |  |  |

Table (2.1): Table de vérité d'un inverseur

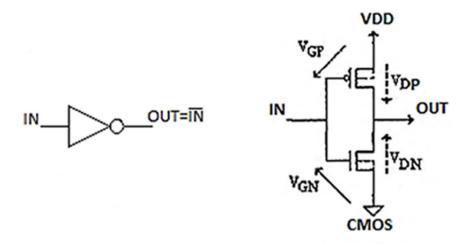

Fig. (2.15): Symbole et réalisation de l'inverseur en technologies CMOS

Lorsque IN est en état haut (V<sub>IN</sub>=V<sub>DD</sub>), la tension grille-source du PMOS est nulle :

$V_{GS} = V_{IN} - V_{DD} = 0$ , il est alors bloqué. En même temps, le NMOS est conducteur, car sa tension VGS est maximale :  $V_{GS} = V_{IN} - 0 = V_{DD}$ . La sortie est donc court-circuitée à la masse par le NMOS présentant une résistance très faible. A l'opposé, lorsque IN est en état bas, c'est le PMOS qui court-circuite la sortie de l'alimentation (état haut), le NMOS restant bloqué.

Ce principe de fonctionnement dégage tout de suite quelques particularités intéressantes de l'inverseur CMOS :

- ✓ La puissance dissipée en régime statique est nulle (dans le cas des technologies supérieurs exp : 1μm, 0.6um... pour les technologies inferieur, la consommation en statique devient importante vue que le courant de fuite et de la même grandeur que le courant de conduction); un des transistors restant toujours bloqué, il n'y a pas de passage de courant.

- ✓ Les transistors conduisent uniquement au cours des commutations, il s'ensuit que la dissipation de puissance dynamique augmentera avec la fréquence de commutation

- ✓ La marge de variation de la tension de sortie est maximale et égale à V<sub>DD</sub> et, par conséquent, l'immunité au bruit est meilleure. Par contre, le dessin de masque de l'inverseur, dit layout, consomme plus de surface de silicium en technologie CMOS. D'autres inconvénients sont les suivants : augmentation des capacités parasites et accroissement du nombre d'étapes technologiques. Ces inconvénients sont toutefois largement compensés par la réduction de la puissance dissipée et la meilleure immunité au bruit, ce qui explique la domination de la technologie CMOS.

#### 2.3. 2. Régime statique

Pour établir la caractéristique de transfert de l'inverseur, c'est-à-dire  $V_{out}$ =f ( $V_{in}$ ), donnant l'information sur tous les états statiques possibles, on considère le transistor PMOS comme charge du NMOS. Cela implique les relations suivantes :

- $\checkmark$   $V_{DN} = V_{out} = V_{DS} = 0$  du NMOS (polarisation drain-source).

- $\checkmark$   $V_{DP} = V_{out} V_{DD} = V_{DS}$  du PMOS (polarisation drain-source).

- $\label{eq:VGN} \checkmark \quad V_{GN} = V_{in} = V_{GS} = 0 \text{ du NMOS (polarisation grille-source)}.$

- $\checkmark$   $V_{GP} = V_{in} V_{DD} = V_{GS}$  du PMOS (polarisation grille-source).

Si, de plus, on suppose que l'inégalité entre les mobilités des trous et des électrons peut être compensée par la largeur du PMOS plus grande que celle du NMOS les caractéristiques de sortie des deux transistors seront symétriques. [13][10]

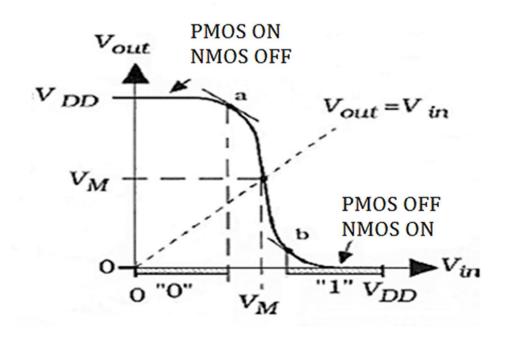

## 2.3.3. Caractéristiques de transfert dans un inverseur [10]

La caractéristique de transfert d'un inverseur est la tension de sortie en fonction de celle de l'entrée. La figure (2.16) représente la courbe de transfert de tension (VTC: Voltage Transfer Curve).  $V_M$  est le point milieu de la courbe, où Vout=Vin. Les points a et b sont des points où la pente de la courbe est -1. Ce sont des points qui définisse où un <0 »logique et un <1 »logique sont détectés.

Fig. (2.16): Caractéristiques de transfert d'un inverseur CMOS

Le seul de basculement est calculé par :

$$V_{\rm M} = \frac{V_{\rm DD} - V_{\rm thp} + KV_{\rm thn}}{1 + K}$$

avec

$$K = \sqrt{\frac{\beta_n \eta_p}{\beta_p \eta_n}}$$

ou

$$\beta_n = \mu_n C_{OX}(\frac{W}{L})$$

où  $\beta_n$  est la transconductance du dispositif.

**Remarque:** (Les indices n et p se rapportent aux NMOS et PMOS). Si les deux transistors sont identiques, on a  $V_M = \frac{V_{DD}}{2}$

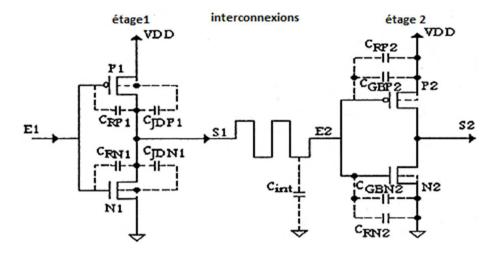

#### 2.3.4. Analyse en régime dynamique

L'analyse dynamique consiste à évaluer la réponse à un signal d'entrée donné. Cette réponse est fonction de la charge capacitive de sortie, cette charge est constituée de trois composantes principales :

- ✓ La capacité interne de sortie de l'inverseur considéré.

- ✓ La capacité d'entrée de tous les opérateurs attaqués.

- ✓ La capacité d'interconnexion.

La figure (2.17.a) montre toutes ces capacités pour le cas simple où la sortie de l'inverseur considéré est connectée à un seul inverseur de l'étage suivant. Dans un tel cas. On parle de condition minimale de charge (la sortance est de 1 (figure 2.17.c); pour 2 inverseurs connectés à la sortie, la sortance serait de 2, et ainsi de suite). Pour la représentation de la figure (2.17.b), la capacité totale de charge  $C_L$  s'écrit :

$$C_L = \underbrace{C_{RP1} + C_{RN1} + C_{JDP1} + C_{JDN1}}_{\text{Sortie étage 1}} + \underbrace{C_{int}}_{\text{cint}} + \underbrace{C_{RP2} + C_{RN2} + C_{GBP2} + C_{GBN2}}_{\text{entrée étage 2}}$$

#### a. Capacité de montage

Fig. (2.17): Capacité totale de charge de sortie d'un inverseur CMOS

Nous notons  $C_R$  la capacité de recouvrement d'un seul côté soit de la source soit du drain, en considérant que le CMOS est symétrique. On a donc :

- ✓ C<sub>RP1,2</sub> capacité de recouvrement du PMOS, respectivement étage 1 et 2.

- ✓ C<sub>RN1,2</sub> capacité de recouvrement du NMOS, respectivement étage 1 et 2.

- ✓ C<sub>IDP,N,1</sub> capacité de la jonction drain-substrat, respectivement du PMOS et NMOS, étage 1.

- ✓ C<sub>GBP,N,2</sub> capacité de grille-substrat, respectivement du PMOS et NMOS, étage 2.

La capacité de charge introduit des délais dans la commutation de l'inverseur.

Après un brusque changement d'état du signal d'entrée, il faut charger ou décharger la capacité CL pour que la sortie puisse se stabiliser au niveau correspondant au nouvel état de l'entrée. S'il n'y a pas de

nouvelle commutation à l'entrée, la sortie atteindra son état stable résultant de l'analyse statique après La capacité un délai dit temps de montée (s'il s'agit d'une montée de la tension de sortie) ou temps de descente (s'il s'agit d'une descente de la tension de sortie). On considère que le niveau bas est atteint si le signal de sortie est plus bas que 10% de  $V_{DD}$ , le niveau haut étant considéré atteint à partir de 90% de  $V_{DD}$ . [14][15]

## a. Temps de descente t<sub>d</sub>

C'est le parcours noté (1) sur les figures (2.18), le NMOS décharge la capacité C<sub>L</sub>. D'abord, il travaille en régime de saturation, puis il termine la décharge en régime linéaire.

Fig. (2.18) : Processus de chargement et de déchargement de la capacité de sortie d'un inverseur CMOS

Le temps de descente est alors calculé entre les niveaux 90% de  $V_{DD}$  et 10% de  $V_{DD}$ , la différence des charges entre ces deux niveaux vaut donc  $0.8C_LV_{DD}$ , et le courant moyen peut être estimé à  $0.5I_{DsatN}$ ; par conséquent, on a :

$$t_{d} = \frac{\Delta Q}{I} = \frac{8}{5} \frac{C_{L} V_{DD}}{I_{DsatN}}$$

L'analyse plus précise, sans recourir au courant moyen, montre que :

$$t_{d} = \frac{C_{L}(V_{thN} - 0.1 \text{ V}_{DD})}{I_{DsatN}} + \frac{C_{L}(V_{DD} - V_{thN})}{2I_{DsatN}} ln \left(2\frac{V_{DD} - V_{thN}}{0.1 \text{ V}_{DD}} - 1\right)$$

Où le premier terme résulte du régime saturé de NMOS et le deuxième du régime non saturé.

Il est intéressant de voir la répartition des valeurs entre ces deux termes ; si on pose  $V_{thN} = \frac{1}{4}V_{DD}$  (usuel pour les technologies actuelles), on obtient :

$$t_{d} = \frac{1}{4} \frac{C_{L} V_{DD}}{I_{DsatN}} + \frac{C_{L} V_{DD}}{I_{DsatN}} = \frac{5}{4} \frac{C_{L} V_{DD}}{I_{DsatN}}$$

Remarquons l'importance du terme associé avec le régime non saturé, ainsi que le bon accord avec l'estimation précédente.

# b. Temps de montée t<sub>m</sub>

C'est le parcours noté (2) sur les figures (2.18) ; le PMOS charge la capacité C<sub>L</sub>.D'abord, il travaille en régime de saturation, puis il termine la charge en régime linéaire.

Le temps de montée est alors calculé entre les niveaux 10% de  $V_{DD}$  et 90% de  $V_{DD}$ ; en appliquant le même raisonnement que pour le temps de descente, on obtient une estimation rapide de  $t_m$  sous la forme :

$$t_{\rm m} = \frac{\Delta Q}{I} = \frac{8}{5} \frac{C_{\rm L} V_{\rm DD}}{I_{\rm DsatP}}$$

L'analyse plus précise, sans recourir au courant moyen, donne :

$$t_{m} = \frac{C_{L}(|V_{thP}| - 0.1 \text{ V}_{DD})}{I_{DsatP}} + \frac{C_{L}(V_{DD} - |V_{thP}|)}{2I_{DsatP}} ln \left(2\frac{V_{DD} - |V_{thP}|}{0.1 \text{ V}_{DD}} - 1\right)$$

Où le premier terme résulte du régime saturé du PMOS et le deuxième du régime non saturé.

Comme précédemment, remarquons la répartition des valeurs entre ces deux termes et le bon accord avec l'estimation rapide ; si on pose  $V_{thP}=-\frac{1}{4}V_{DD}$  (usuel pour les technologies actuelles), on obtient :

$$t_{\rm m} = \frac{1}{4} \frac{C_{\rm L} V_{\rm DD}}{I_{\rm DsatP}} + \frac{C_{\rm L} V_{\rm DD}}{I_{\rm DsatP}} = \frac{5}{4} \frac{C_{\rm L} V_{\rm DD}}{I_{\rm DsatP}}$$

Dans ce cas, le terme associé avec le régime non saturé est, là aussi, plus important que celui dû au régime saturé.

La somme des temps de montée et de descente détermine la fréquence maximale de fonctionnement d'une porte logique sans que le signal soit déformé :

$$f_{\text{max}} = \frac{1}{t_{\text{d}} + t_{\text{m}}}$$

À cette fréquence, les niveaux bas et haut sont juste atteints.

Pour transmettre un signal à travers une porte, il suffit d'un temps inférieur au temps de descente ou à celui de montée ; en fait, il suffit que la sortie atteigne le seuil de commutation de l'étage suivant

Cela définit les temps de propagation d'une porte, soit le temps de propagation à la descente  $t_{pd}$ , soit le temps de propagation à la montée  $t_{pm}$ .

Pour des commutations à cette vitesse, le signal est déformé mais l'information passe, d'où l'importance de la notion de temps de propagation pour les circuits numériques

## c. Temps de propagation à la descente $t_{pd}$

C'est la moitié du parcours noté (1) sur les figures (2.18). Le NMOS décharge la capacité  $C_L$ , il travaille d'abord en régime de saturation, mais en approchant le niveau 50% de  $V_{DD}$ , il est légèrement non saturé. Le temps de propagation à la descente est alors calculé entre les niveaux  $V_{DD}$  et 50% de  $V_{DD}$ , la différence des charges entre ces deux niveaux vaut donc  $0.5C_LV_{DD}$ , et le courant moyen peut être estimé à  $I_{DsatN}$ , par conséquent, on a :

$$t_{pd} = \frac{\Delta Q}{I} = \frac{1}{2} \frac{C_L V_{DD}}{I_{DeatN}}$$

L'analyse plus précise, tenant compte des variations réelles du courant, montre que :

$$t_{pd} = \frac{C_{L}V_{thN}}{I_{DsatN}} + \frac{C_{L}(V_{DD} - V_{thN})}{2I_{DsatN}} ln \left(4 \frac{V_{DD} - V_{thN}}{V_{DD}} - 1\right)$$

Où le premier terme résulte du régime saturé du NMOS et le deuxième dv régime non saturé. La répartition des valeurs entre ces deux termes peut être obtenue

si on pose  $V_{thN} = \frac{1}{4}V_{DD}$  (usuel pour les technologies actuelles); on obtient :

$$t_{pd} = \frac{1}{4} \frac{C_L V_{DD}}{I_{DsatN}} + \frac{1}{4} \frac{C_L V_{DD}}{I_{DsatN}} = \frac{1}{2} \frac{C_L V_{DD}}{I_{DsatN}}$$

Remarquons que le terme associé au régime non saturé équivaut à celui dû au régime saturé, ainsi que l'accord avec l'estimation précédente.

## d. Temps de propagation à la montée t<sub>pm</sub>

C'est la moitié du parcours noté (2) sur les figures (2.18). Le PMOS charge la capacité  $C_L$ ; il travaille d'abord en régime de saturation, mais il termine en régime légèrement non saturé. Le temps de propagation à la montée est alors calculé entre les niveaux 0 et 0,5  $V_{DD}$ ; en appliquant le même raisonnement que pour le temps de propagation à la descente, on obtient une estimation rapide de  $t_{pm}$  sous la forme :

$$t_{pm} = \frac{\Delta Q}{I} = \frac{1}{2} \frac{C_L V_{DD}}{I_{DeatP}}$$

L'analyse plus précise, sans recourir au courant moyen, donne :

$$t_{pm} = \frac{C_{L}|V_{thP}|}{I_{DsatP}} + \frac{C_{L}(V_{DD} - |V_{thP}|)}{2I_{DsatP}} ln \left(4 \frac{V_{DD} - |V_{thP}|}{V_{DD}} - 1\right)$$

Où le premier terme résulte du régime saturé du PMOS et le deuxième du régime non saturé.

La répartition des valeurs entre ces deux termes (en supposant  $V_{thP} = -\frac{1}{4}V_{DD}$  établie ci-après :

$$t_{pm} = \frac{1}{4} \frac{C_L V_{DD}}{I_{DsatP}} + \frac{1}{4} \frac{C_L V_{DD}}{I_{DsatP}} = \frac{1}{2} \frac{C_L V_{DD}}{I_{DsatP}}$$

Dans ce cas, le terme associé avec le régime non saturé est aussi important que celui dû au régime saturé. On souligne le bon accord entre estimations rapide et précise.

Du fait que les temps de propagation t<sub>pd</sub> et t<sub>pm</sub> ne sont pas forcément égaux, on définit souvent le temps moyen de propagation, aussi appelé délai moyen de propagation, par :

$$t_{p} = \frac{1}{2} \left( t_{pd} + t_{pm} \right) = \frac{1}{4} C_{L} V_{DD} \left( \frac{1}{I_{DsatN}} + \frac{1}{I_{DsatP}} \right) = \frac{1}{4} (t_{ON} + t_{OP}) \frac{C_{L}}{C_{GB}}$$

où  $t_{ON}$  et  $t_{OP}$  sont les délais intrinsèques des transistors NMOS et PMOS et  $C_{GB}$  leur capacité grille-substrat (dans ce cas, supposée égale pour les deux transistors).

#### 2.3.5. Puissance dissipée

La puissance dissipée totale intègre trois composantes : La puissance dynamique, la puissance statique, la puissance de court-circuit. [16]

#### a. Puissance dynamique

Au cours d'un cycle T du signal d'entrée commençant au niveau bas, la capacité de charge est d'abord déchargée (ce qui ne consomme pas d'énergie de l'alimentation) et ensuite chargée par une charge :  $Q_{L=}C_{L}V_{DD}$  provenant de l'alimentation (ce qui consomme bien de l'énergie). La puissance dynamique s'écrit :

$$P_{\rm dyn} = V_{\rm DD}I_{\rm charge/decharge} = V_{\rm DD}\frac{Q_{\rm L}}{T} = V_{\rm DD}\frac{C_{\rm L}V_{\rm DD}}{T} = f_{\rm C}C_{\rm L}V_{\rm DD}^2$$

où  $f_C$  est la fréquence d'horloge  $(f_C = \frac{1}{T})$ .

#### **b.** Puissance statique

L'un des transistors est toujours bloqué, seul le courant sous le seuil  $I_0ff$  donne lieu à une consommation statique. En supposant que  $I_{offN} = I_{off}P = I_{off}$ , on a pour la puissance statique:  $P_{stat} = I_{off}V_{DD}$

#### c. Puissance de court-circuit

Au cours de chaque commutation, il y a un bref instant où les deux transistors sont passants.

Dans cet état, du fait de leurs résistances équivalentes faibles, ils court-circuitent l'alimentation à la masse.

C'est pour cela que la dissipation d'énergie associée à ce phénomène est dite puissance court-circuit  $P_{cc}$ . De manière très approximative, on peut considérer que l'on a :

$$P_{cc}=10\%P_{dyn}$$

#### d. Puissance totale

En toute rigueur, la puissance totale d'un inverseur est donc la somme de trois composantes :

$$P_{tot} = P_{dvn} + P_{stat} + P_{cc}$$

Mais en pratique, on commettra très peu d'erreur en considérant :

- ✓ Seulement P<sub>dyn</sub>et P<sub>cc</sub> pour le régime dynamique : c'est justifié par le fait que I<sub>off</sub> est de plusieurs ordres de grandeur plus faible que I<sub>on</sub>.

- ✓ Seulement P<sub>stat</sub>pour le régime statique (circuit au repos), dans un équipement portable alimenté par piles, la consommation statique détermine la durée de vie des piles.

Notons, enfin, que la puissance dynamique de l'oscillateur est proportionnelle à la fréquence d'horloge  $f_c$ ; cela explique pourquoi (sauf les cas particuliers de circuits fortement parallèles fonctionnant à une fréquence très élevée) les circuits CMOS dissipent moins de puissance que les circuits NMOS.

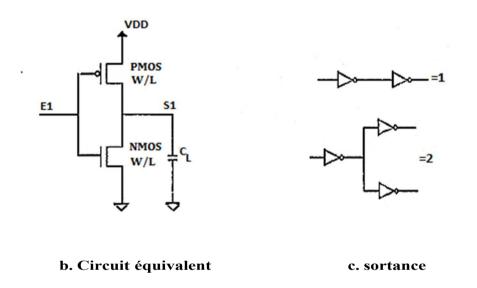

#### **2.4.** Portes logiques de base [16] [10] [17]

Les circuits logiques sont tous construits à partir des portes logiques de base et des circuits tampons d'entrée et de sortie assurant les communications avec l'environnement. Toutes les fonctions logiques peuvent être réalisées à partir des portes NAND et NOR, mais le nombre et les types de portes de base utilisées en pratique peut-être très grands. Ici nous passerons en revue les quelques exemples les plus représentatifs.

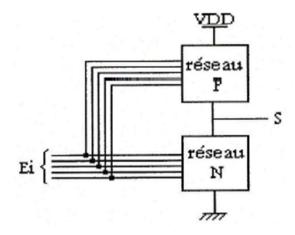

## ✓ Constitution des piles N et P

Pour réaliser une fonction plus complexe, nous allons remplacer chaque branche de l'inverseur par un réseau de plusieurs interrupteurs de même type, comme illustré dans la figure (2.19). Les règles globales sont les mêmes que pour l'inverseur, mais chaque branche N et P, sera constituée d'un réseau d'interrupteurs, montés en parallèle ou en série, tous reliés deux à deux (au moins) par leur grille, et respectant la condition de conduction d'une branche à l'exclusion de celle de l'autre.

Fig. (2.19) : Schéma de principe de la logique complémentaire

En logique complémentaire, un circuit est constitué de deux réseaux duaux :

- ✓ Un réseau N (Pile N), constitué exclusivement de transistors NMOS, branché entre la sortie et la masse.

- Un réseau P (Pile P), constitué exclusivement de transistors PMOS, branché entre la sortie et V<sub>DD</sub>.

Pour être duaux les deux réseaux doivent satisfaire les principes suivants :

- Etre commandés par les mêmes entrées Ei, chaque entrée Ei commandant au moins une paire d'interrupteurs (un N et un P).

- Quel que soit l'état des entrées Ei, un seul réseau doit être passant à la fois.

- II est toléré toutefois que les deux branches soient ouvertes en même temps.

La figure (2.20) représente le fonctionnement de la logique complémentaire.

Fig. (2.20) : Schéma du fonctionnement de la logique complémentaire

La fonction de sortie S est générée par :

- La fermeture au réseau N, pour obtenir S=0 soit \overline{S}.

- La fermeture du réseau P, pour obtenir S=l soit S.

#### ✓ Transition de signal des portes à entrées multiples

Dans les portes à entrées multiples, les transitions des signaux multiples produisent des changements de sortie.

Pour les portes à plusieurs entées (N- entrée en générale) avec M0 : les états de sortie bas et M1 : les états de sortie haut, on a :

- Transitions de sortie haut à bas =  $M0 \cdot M1$

- Transitions de sortie de bas à haut =  $M1 \cdot M0$

- Transitions totales à caractériser = 2·M0·M1

La courbe de transfert de tension (VTC : Voltage Transfer Curve) varie à chaque transition de la sortie des portes à plusieurs entrées. Le point milieu  $V_M$  de la courbe VTC varie aussi avec ces transitions.

Remarque : Ne pas tester / caractériser les cas sans transition de sortie.

#### ✓ Circuits équivalents en série / parallèles

- ❖ Un transistor avec un rapport de forme W1/L1 a une résistance proportionnelle à L1/W1 (la résistance diminue inversement avec W1).

- ❖ Deux transistors en parallèle avec des rapports de forme W1/L1 et W2/L2 sont équivalent à un seul transistor (W1/L1+W2/L2)/1.

- ❖ Deux transistors en série avec le facteur de forme W1/L1 et W2/L2 sont équivalent à un seul transistor 1/ (L1/W1+L2/W2).

Par exemple, un transistor avec un facteur de forme égale 3/1 en série avec un autre 3/1 est équivalent à 1/(1/3+1/3) ou 3/2. On peut utiliser la méthode suivante pour calculer la taille du transistor équivalent:

- Pour des transistors en parallèles, on remplace les longueurs par 1 et on additionne les largeurs.

- ❖ Pour des transistors en séries, on remplace les largeurs par 1 et on additionne les longueurs.

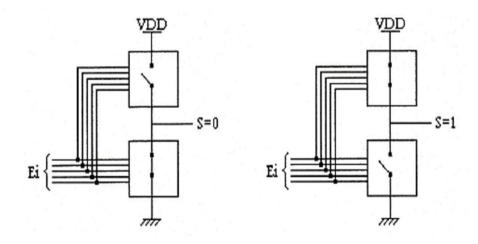

#### 2.4.1. Porte NAND

La sortie de la porte NAND n'est à 0 que si toutes les entrées sont à 1. La figure (2.21) présente un exemple d'une porte NAND à deux entrées en réalisation CMOS avec son symbole et sa table de vérité.

Les deux figures (2.22.a) et (2.22.b) présentent : le tableau de transition et les courbes de transfert de tension (VTC) d'une porte NAND à deux entrées. La courbe VTC varie à chaque transition (i, ii, iii).

#### **2.4.2. Porte AND**

La sortie de la porte AND ne passe à 1 que si toutes ses entrées sont à 1. Elle se compose d'une porte NAND avec, en plus, un inverseur intégré à la sortie. Cela implique que le délai d'une porte ET est la somme du délai de la porte NAND et du délai de l'inverseur. La porte ET, étant moins rapide et plus encombrante que la porte NAND, est donc bien moins souvent utilisée.

La figure (2.23) montre une porte AND à deux entrées en réalisation CMOS avec son symbole et la table de vérité correspondante:

#### **2.4.3. Porte NOR**

La porte NOR réalise l'opération complémentaire de celle de la porte NAND (figure2.21) : sa sortie passe à 0 dès qu'une des entrées passe à 1. C'est pour cela que sa structure ressemble à celle d'une NAND. La figure (2.24) présente la réalisation CMOS d'une porte NOR à deux entrées.

Les deux figures (2.25.a) et (2.25.b) présentent : le tableau de transition et les courbes de transfert de tension (VTC) d'une porte NOR à deux entrées. La courbe VTC varie à chaque transition (i, ii, iii).

Fig. (2.25): Transition du signal de la porte NOR

#### 2.4.4. Porte OR

La sortie de la porte OR passe à 1 dès que l'une des entrées passe à 1. Elle compose d'une porte NOR avec en plus un inverseur intégré à la sortie. Cela implique que le délai d'une porte OU est la somme du délai d'une porte NOR et du délai de l'inverseur. La porte OU, étant moins rapide et plus encombrante que la porte NOR, est bien moins souvent utilisée.

La figure (2.26) illustre une porte OR à deux entrées en réalisation CMOS avec son symbole et la table de vérité correspondante.

#### 2.5. Conclusion

Dans ce chapitre, nous avons présenté le transistor MOS. Puis, nous avons étudié théoriquement l'inverseur CMOS. Enfin, nous avons présenté les portes logiques de base de la bibliothèque de cellule standard.

# **Chapitre 3**

# Etude pratique des portes logiques

- 3.1 Introduction

- 3.2 Outil de conception Cadence

- 3.3 Bibliothèque des cellules

- 3.4 Tests et résultats des différents éléments de la bibliothèque

- 3.5 Vues géométriques (Layout)

- 3.6 Conclusion

#### 3.1. Introduction

Ce chapitre est consacré à 1'etude des caractéristiques principales des éléments conçus de la bibliothèque. Les tests et les résultats de fonctionnement des éléments de la bibliothèque sont réalisés sur logiciel Cadence. Cette bibliothèque est développée avec la technologie CMOS  $1\mu m$  de la salle blanche du CDTA.

#### 3.2. Outil de conception Cadence