ال<u>ي جمورية الجزاءري</u>ة الديمقراطية الش<u>عية</u> People's Democratic Republic of Algeria

وزارة النظور المعطلي و الدحث العطمي Ministry of Higher Education and Scientific Research

> ج المعة سعد دجلب الياليدة SAAD DAHLAB University of BLIDA

> > ڭلېة النئنولوجېا Faculty of Technology

وَسِمِ االلَّكَتَرَ وِ نَوْنَكَ Department of Electronics

## **Master memory**

Sector: Telecommunications

Specialty: Telecommunications Systems

**Presented by**

HOCEINE Amina & REDJALA Djihane

## **Realization of a simulation interface**

## prototype for wireless systems for SDR

## (Software Defined Radio)

Proposed by: AITSAADI Hocine College year 2020-2021

# Thanks

As a preamble, we thank ALLAH who has helped us and given us patience and courage throughout our years of study.

We would like to sincerely thank our promoter Mr. AITSAADI HOCINE, headmaster of the electronics department, for his listening and his availability throughout the realization of this end of studies project work. He is also thanked for the inspiration, the help and the time he was kind enough to devote to us and that without him this memoir would never have seen the light of day.

Our thanks also go to the honorable members of the jury who agreed to examine our modest work and sit in its defense.

Our high regard goes to all the teachers in our department for the monumental effort they put into making us who we are now.

*We do not forget our dear parents for their contribution, their support and above all their patience.*

*Finally, our warmest thanks go to the people who provided assistance and contributed to the development of this dissertation, as well as to the success of this wonderful academic year.*

# Dedication

I dedicate this modest work:

To my dearest mother,

who supported and encouraged me during these years of study;

To my very dear father,

who owes my life, my success and all my respect I hope this work reflects my gratitude and affection;

To my brothers and my sister,

who shared with me all the moments of emotion while carrying out this work;

To my partner,

for her moral support, her patience and its understanding throughout this project;

To all my best and true friends, each with their own name;

To all those I love, and to all those who are dear to me, I dedicate this work ...

### Amina

# Dedication

Life is an accumulation of experiences, good and bad, and today I am about to complete a new chapter in my humble life;

I am grateful to Allah for giving me the power and patience to stand here and say that I am on the verge of making the dream of a lifetime come true;

To My father,

how can words describe a galaxy ... you gave me life, courage and love, you were and you are my reason to continue;

My mother,

the one who believed in me even when I didn't, how can a princess be without a queen, I really am a version of you and I can't be more honored;

To my Sun,

you are the golden hour of a lifetime, to Chames El Assil;

To El Doctoura,

.. you are my full moon in a dark night, to Nesrine;

To my doctor,

you are the beauty in everything that ever existed, to Aya;

To my sweet baby,

you are a whole different story ... you taught me what a strong woman would look like ... but you will always be my little baby no matter how old you are ...to Soundous;

To My sixth sister,

you made me a better new version of me and i can say everything except how pure and beautiful you are, to Romaissa;

To the star of our life,

To the second version oh my hero, to my brother, no words will ever be enough to express my pride in you, to DhiaaEdine;

To my partner,

To the one I spent with my last 5 years ...the one i cried and laughed with, to Amina;

To all my teachers since i was 6;

To Blida ... To Tipaza ...

Thank you all for everything;

I love you and I dedicate this work to you;

### Djihane

## List of acronyms and abbreviations

- ADC: Analog-To-Digital Converter.

- ALU: Arithmetic and Logic Unit.

- ASIC: Specific Integrated Circuit.

- ASK: Amplitude Shift Keying.

- BPF: Band-Pass Filters.

- **BPSK:** Binary Phase Shift Keying.

- CMOS: Complementary Metal–Oxide–Semiconductor.

- CP: Cyclic Prefix.

- CUDA: Compute Unified Device Architecture.

- DAC: Digital-To-Analog Converter.

- DDC: Digital Down Converter.

- DFT: Discrete Fourier Transform.

- DFT: Discrete Fourier Transform.

- DPSK: Differential Phase Shift Keying.

- DSBSC: Double-Sideband Suppressed Carrier.

- DSP: Digital Signal Processor.

- DTH: Direct-To-Home.

- DUC: Digital Up-Converter.

DVT: Digital Video Broadcasting.

EM: electromagnetic.

FDD: Frequency Division Duplex.

FDM: Frequency Division Multiplexing.

FFT: Fast Fourier Transform.

FFT: Fast Fourier Transform.

FIR: First Information Report.

FLOPS: Floating Point Operations Per Second.

FPGA: Field Programmable Gate Array.

FSK: Frequency Shift Keying.

GNSS: Global Navigation Satellite System.

GOPS: Giga Operations Per Second.

GPP: General-Purpose Processor.

GPU: Graphical Processing Units.

GUI: Graphical User Interface.

HLS: High-Level Synthesis.

HPC: High-Performance Computing.

ICI: Inter-Carrier Interference.

IDFT: Inverse Discrete Fourier Transform.

IEEE: Electrical and Electronics Engineers.

IF: Intermediate Frequency.

IFFT: Inverse FFT.

LDPC: Low-Density Parity Check.

LNA: Low Noise Amplifier.

LOS: Line of Sight.

LOS: Line-Of-Sight.

LPF: low-pass filter.

LUT: look-up tables.

MAC: Multiplication And Accumulation.

MIMO: Multiple-Input and Multiple-Output

NFV: Network Function Virtualization

NLOS: No line of sight.

NRZI: Non Return to Zero Inverted.

OFDM: Orthogonal Frequency Division Multiplexing.

PAM: Pulse Amplitude Modulation.

PL: Path Loss.

PPL: Phase Locked Loop.

QAM: Quadrature Amplitude Modulation.

QPSK: Quadrature Phase Shift Keying.

RF: Radio frequency.

RFFE: Radio Frequency Front End.

RFID: Radio-Frequency Identification.

RTL: Register Transfer Level.

SDR: Software-Defined Radio.

SFDR: Spurious-Free Dynamic Range.

SNR: Signal-to-Noise Ratio.

SRC: Sampling Rate Conversion.

TDD: Time Division Duplex.

VHDL: VHSIC Hardware Description Language.

WiMAX: Worldwide Interoperability for Microwave Access.

WLAN: Wireless Local Area Network.

x-DSL: x Digital Subscriber Line.

ملخص :معايير الاتصالات اللاسلكية تتغير باستمرار وتتطور بسرعة. يشكل هذا تحديًا للباحثين والمصنعين ، الذين يجب أن يتكيفوا معه في عملهم. أدت الحاجة إلى طريقة وأجهزة للتعامل مع هذا التغيير المستمر إلى تعميم استخدام ومفاهيم النماذج الأولية السريعة ومنصات البرامج الراديوية القائمة على .(FPGA (SDR من الواضح أن بعض الأساليب والأدوات القائمة على هذا المفهوم ظهرت في برمجة برامج الراديو. وتتمثل خصائص كل هذه الأساليب في قدرتها على توفير وقت التطوير وسهولة تطبيقها. لم تعد الأدوات المقدمة تتطلب معرفة متعمقة بلغات برمجة الأجهزة أو الأجهزة المستهدفة. العمل الموصوف في هذه الأطروحة هو تطبيق أسلوب النموذج الأولي على منصة على SDR (USRP).

تُســتخدم أدوات البرامج هذه لإنشــاء بنية المقدّر ، والتي يتم تحويلها بعد ذلك إلى لغة أجهزة (HDL) وتنفيذها على النظام الأساسي (SDR (USRP) الهدف .

**Abstract:** Wireless telecommunications standards are constantly changing and evolving rapidly. This poses a challenge for researchers and manufacturers, who must adapt to it in their work. The need for a method and hardware to cope with this constant change has popularized the use and concepts of rapid prototyping and FPGA-based software radio (SDR) platforms. Obviously, some methods and tools based on this concept have appeared in the programming of software radio. The characteristics of all these methods are that they can save development time and are easy to apply. The provided tools no longer require indepth knowledge of hardware programming languages or target hardware. The work described in this thesis is the application of the prototype method on the SDR platform (USRP). This method does not require any lines of code because it is based on MATLAB/Simulink.

These software tools are used to create the estimator architecture, which is then converted into a hardware language (HDL) and implemented on the target SDR (USRP) platform.

**Résumé :** Les normes de télécommunications sans fil changent constamment et évoluent rapidement. Cela représente un défi pour les chercheurs et les industriels, qui doivent s'y adapter dans leur travail. Le besoin d'une méthode et d'un matériel pour faire face à ce

changement constant a popularisé l'utilisation et les concepts de prototypage rapide et de plates-formes de radio logicielle (SDR) basées sur FPGA. Evidemment, certaines méthodes et outils basés sur ce concept sont apparus dans la programmation de logiciels radio. Les caractéristiques de toutes ces méthodes sont qu'elles permettent de gagner du temps de développement et sont faciles à appliquer. Les outils fournis ne nécessitent plus une connaissance approfondie des langages de programmation matérielle ou du matériel cible. Le travail décrit dans cette thèse est l'application de la méthode prototype sur la plateforme SDR (USRP). Cette méthode ne nécessite aucune ligne de code car elle est basée sur Matlab/Simulink.

Ces outils logiciels sont utilisés pour créer l'architecture de l'estimateur, qui est ensuite convertie en un langage matériel (HDL) et implémentée sur la plate-forme SDR cible (USRP).

### Table des matières

| E  | BF | PSK: Binary Phase Shift Keying defined               |

|----|----|------------------------------------------------------|

|    | (  | General Introduction18                               |

|    |    | CHAPITRE I                                           |

| 1. |    | Introduction to the Software-Defined Radio           |

| 2. |    | Concepts and architecture                            |

| ļ  | ٩. | Antenna                                              |

| E  | 3. | RF Front End                                         |

| (  | 2. | Analogy-to-Digital and Digital-to-Analogy Conversion |

| [  | ). | Digital Front End                                    |

| E  |    | Signal Processing                                    |

| 3. |    | Design Approaches                                    |

| A  | ٩. | GPP-based                                            |

| E  | 3. | DSP-based                                            |

| (  | 2. | FPGA-based10                                         |

| [  | Э. | Hybrid Design (a.k.a., co-design)13                  |

| E  |    | Comparison1                                          |

| 4. |    | SDR's Application and operating principle10          |

| 5. |    | SDRs software18                                      |

| A  | ٩. | MATLAB and Simulink18                                |

| E  | 3. | Vivado HLS and SDSoC                                 |

| (  | 2. | GNU Radio19                                          |

| [  | ). | LabVIEW20                                            |

| E  | Ξ. | CUDA                                                 |

| 6. |    | Introduction to the USRP                             |

| 7. |    | NI 29xx USRPs applications22                         |

| 8. |    | CONCLUSION                                           |

| CH | AI | PITRE II24                                           |

| 1. |    | The Digital Communication Chain                      |

|     | Α.   | Introduction                                                                | 26 |

|-----|------|-----------------------------------------------------------------------------|----|

|     | В.   | The message source                                                          | 27 |

|     | C.   | Source coding                                                               | 27 |

|     | D.   | Channel coding                                                              | 27 |

|     | E.   | The issuer                                                                  | 28 |

|     | F.   | Transmission channel                                                        | 29 |

|     | G.   | The receiver                                                                | 29 |

| 2   | . D  | igital Modulation                                                           | 30 |

|     | Α.   | Definition                                                                  | 30 |

|     | В.   | Types of Digital Modulation                                                 | 30 |

| 1   | . T  | ypes of M-ary Techniques:                                                   | 46 |

| 3   | . v  | /ireless channels                                                           | 48 |

|     | Α.   | The types of wireless channels                                              | 48 |

|     | В.   | Propagation in the wireless channel                                         | 49 |

|     | C.   | Channel to fainting:                                                        | 51 |

|     | D.   | Specific models of wireless channels for large fading scale and small scale | 52 |

|     | E.   | Types of channels:                                                          | 53 |

| 4   | . 0  | FDM:                                                                        | 55 |

|     | Α.   | Definition                                                                  | 55 |

|     | В.   | Basic principles of OFDM:                                                   | 57 |

|     | C.   | working principle:                                                          | 59 |

|     | D.   | OFDM in systems                                                             | 60 |

| С   | HAPI | TRE III                                                                     | 65 |

| Imp | leme | ntation of the data link via the USRP type 2920 platform                    | 65 |

| 1   | . In | itroduction:                                                                | 66 |

| 2   | . N  | I 2920 USRPs installation:                                                  | 66 |

| 3   | . u  | sing MATLAB with USRP                                                       | 67 |

| 4   | . In | nplementation:                                                              | 68 |

|     | Α.   | Simulating Real FM reception:                                               | 68 |

|     | В.   | Simulating Real 16 QAM Transmission:                                        | 69 |

|     | C.   | Simulating Real QPSK Transmission:                                          | 88 |

| 5   | . C  | onclusion:                                                                  | 93 |

| General conclusion94 |

|----------------------|

|----------------------|

## List of Figures

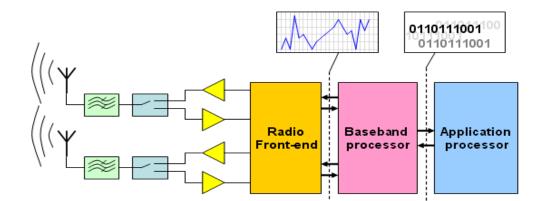

| Figure1. 1:Software-defined radio                                                                | 2  |

|--------------------------------------------------------------------------------------------------|----|

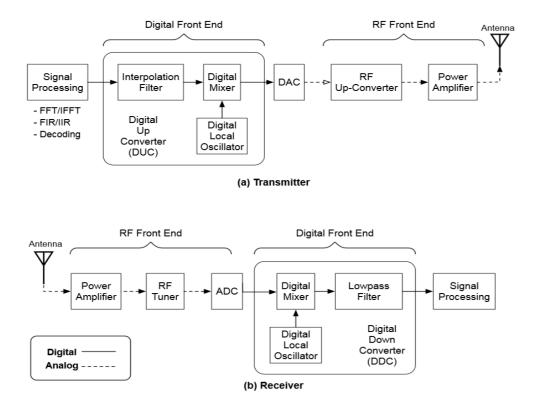

| Figure 1. 2:SDR architecture. Sub-figure (a) shows SDR from a receiver's point of view, and sub- |    |

| figure (b) shows SDR from a transmitter's point of view                                          | 7  |

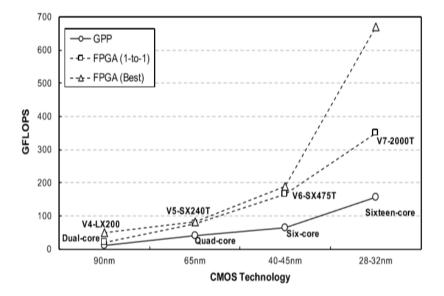

| Figure1. 3:Peak performance of GPPs versus FPGAs when performing 64-bit floating point           |    |

| operations                                                                                       | 11 |

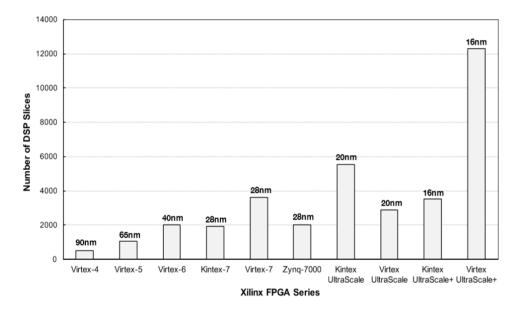

| Figure1. 4:Number of DSP Slices in Xilinx FPGAs. The values on top of the bars refer to the CMOS | 5  |

| technology used                                                                                  | 15 |

| Figure1. 5:MathWorks SoC design flow                                                             | 19 |

| Figure1. 6:Universal Software Radio Peripheral (USRP)                                            | 21 |

| Figure1. 7:USRP board architecture. RF daughterboard selection depends on the application        |    |

| specifications in terms of frequency coverage                                                    | 22 |

|                                                                                                  |    |

| Figure 2. 1: transmission chain.              | 26 |

|-----------------------------------------------|----|

| Figure 2. 2: simple model of a channel        | 29 |

| Figure 2. 3: ASK modulated output wave.       | 31 |

| Figure 2. 4: ASK generation method.           | 31 |

| Figure 2. 5: asynchronous ASK detector        | 32 |

| Figure 2. 6:synchronous ASK detector.         |    |

| Figure 2. 7:FSK Transmiter.                   | 34 |

| Figure 2. 8: Asynchronous FSK Detector.       | 35 |

| Figure 2. 9:synchronous FSK Detector.         | 36 |

| Figure 2. 10: BPSK Modulator.                 | 37 |

| Figure 2. 11: BPSK modulated output wave.     | 37 |

| Figure 2. 12: BPSK demodulator.               | 38 |

| Figure 2. 13: QPSK Modulator                  | 39 |

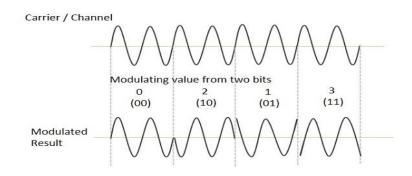

| Figure 2. 14: QPSK modulated output wave.     | 40 |

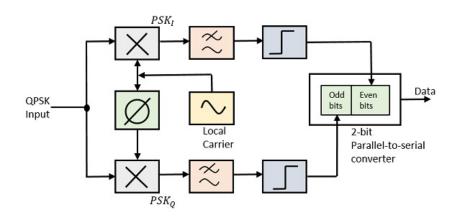

| Figure 2. 15: QPSK demodulator.               | 40 |

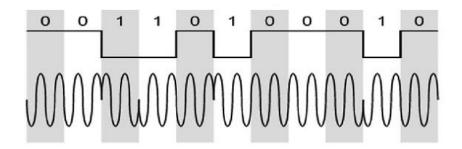

| Figure 2. 16: DPSK modulated output wave      | 41 |

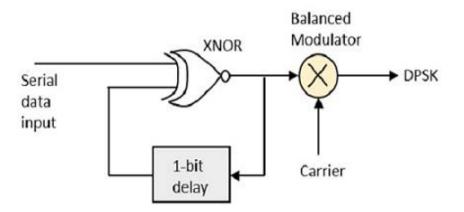

| Figure 2. 17: DPSK modulator.                 | 42 |

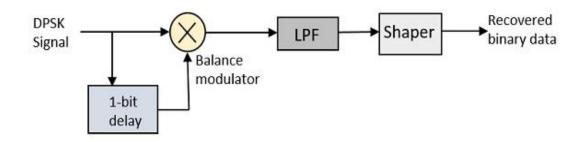

| Figure 2. 18: DPSK demodulator.               | 42 |

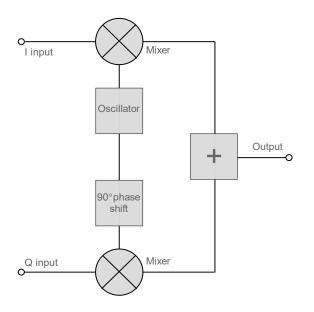

| Figure 2. 19: QAM modulator.                  | 44 |

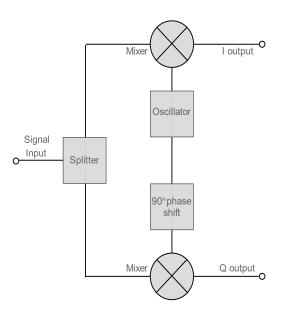

| Figure2. 20:QAM demodulator.                  | 44 |

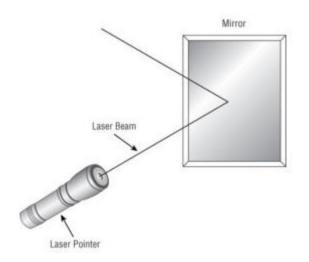

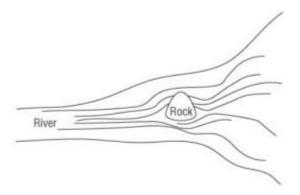

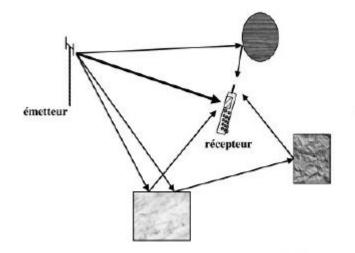

| Figure 2. 21: Reflection.                     | 50 |

| Figure 2. 22: Diffraction.                    | 50 |

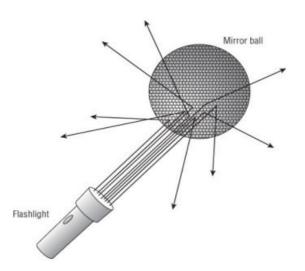

| Figure 2. 23: Scattering                      | 51 |

| Figure 2. 24: Gaussian channel.               | 53 |

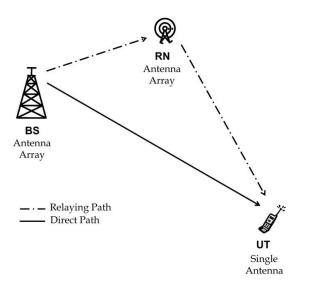

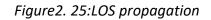

| Figure 2. 25:LOS propagation                  | 54 |

| Figure 2. 26: NLOS propagation.               |    |

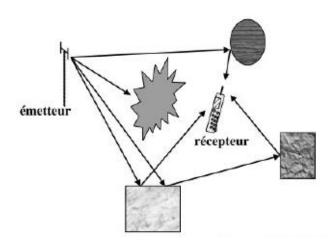

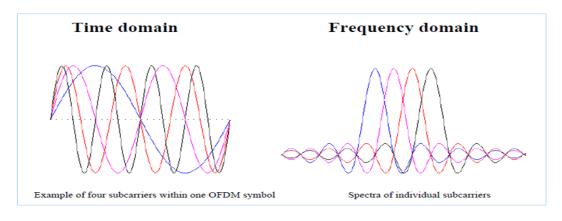

| Figure 2. 27: OFDM Orthogonality.             | 56 |

| Figure 2. 28: Frequency Domain Orthogonality. | 57 |

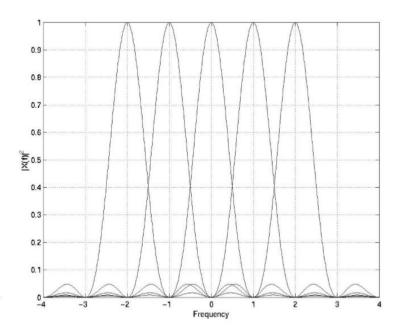

| Figure2. 29:OFDM spectra.                       | 58 |

|-------------------------------------------------|----|

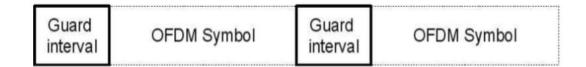

| Figure 2. 30: Remove ISI through guard interval | 59 |

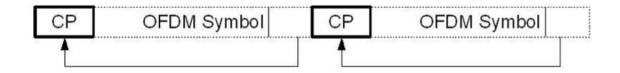

| Figure2. 31:Cyclic Prefix                       | 59 |

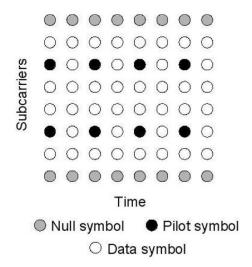

| Figure 2. 32: Example of OFDM signal pattern    | 62 |

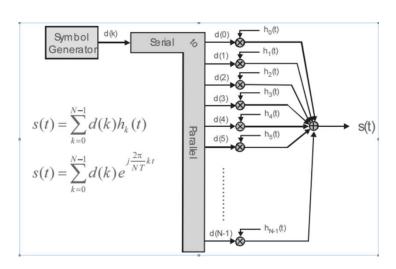

| Figure2. 33: OFDM modulator                     | 63 |

| Figure2. 34:OFDM demodulator.                   | 64 |

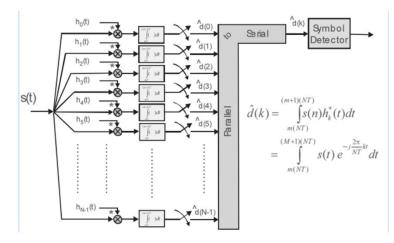

| Figure 3. 1: FM Broadcast Receiver with USRP (R) Hardware. | 68 |

|------------------------------------------------------------|----|

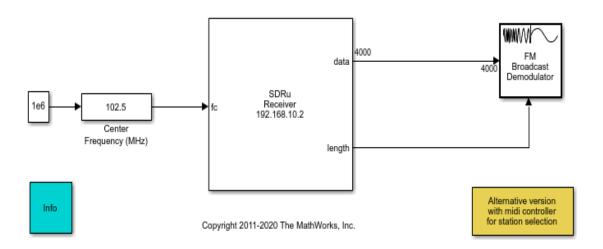

| Figure 3. 2: 16-QAM transmitter with USRP(R) Hardware      | 69 |

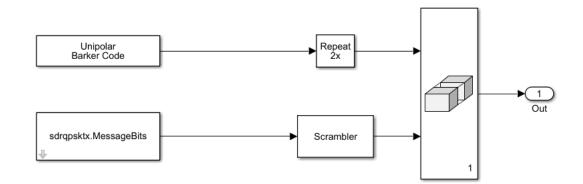

| Figure 3. 3: bits generations block                        |    |

| Figure 3. 4: Parameter of Rectangular 16-QAM               |    |

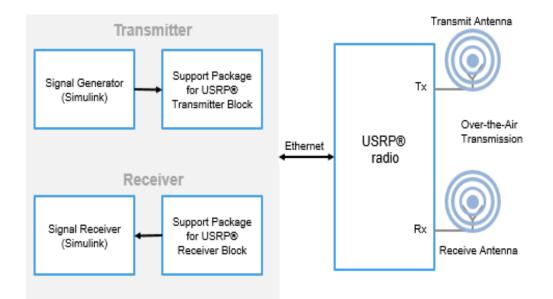

| Figure 3. 5: SDRu Transmitter-receiver blocks              | 72 |

| Figure 3. 6: Parameter of sdru transmitter                 | 73 |

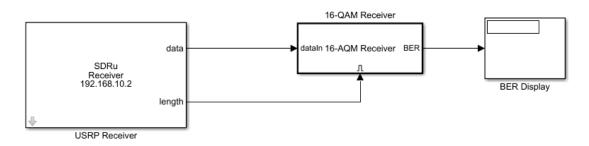

| Figure 3. 7: 16-QAM receiver withe USRP (R) hardware       | 74 |

| Figure 3. 2: Parameter of sdr receiver                     | 76 |

| Figure3. 9: Parameter of BER display                       |    |

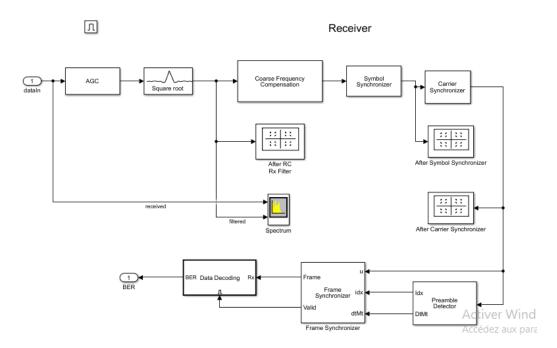

| Figure3. 10: sdru receiver blocks                          | 77 |

| Figure 3. 11: Parameters of DataIn                         |    |

| Figure 3. 12: Parameter of AGC block                       |    |

| Figure 3. 13: Parameter of Square root                     |    |

| Figure 3. 14: Parameter of samples per symbol              | 83 |

| Figure 3. 15: Parameter of Carrier Synchronizer            |    |

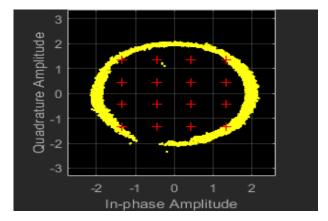

| Figure 3. 16: constellation diagram                        |    |

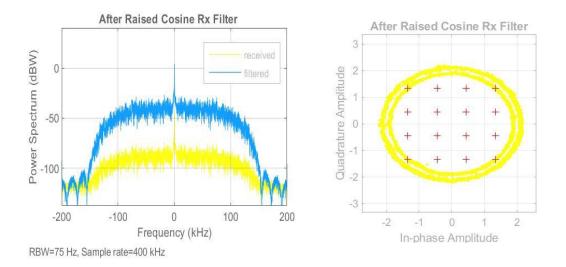

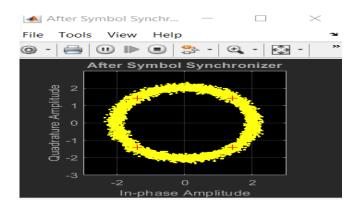

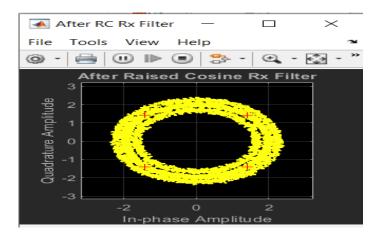

| Figure3. 17: after raised cosine Rx filter                 | 86 |

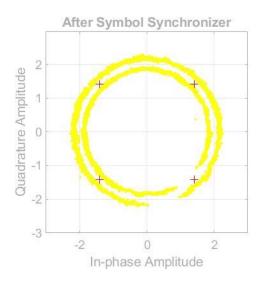

| Figure 3. 2: after symbol synchronizer                     | 86 |

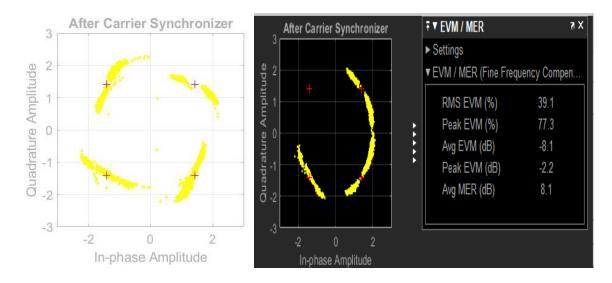

| Figure 3. 19: after carrier synchronizer                   |    |

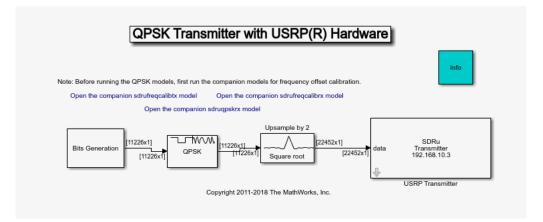

| Figure 3. 20: QPSK transmitter with USRP(R) hardware       | 88 |

| Figure 3. 21: Parameter of QPSK modulator                  | 89 |

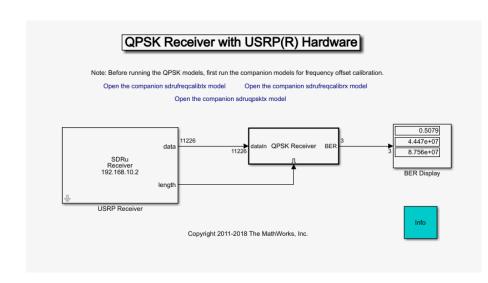

| Figure 3. 22: QPSK receiver with USRP(R) hardware          | 89 |

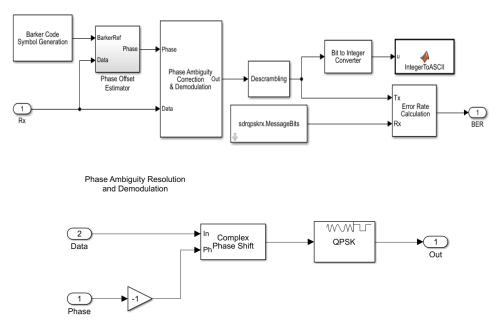

| Figure3. 23: QPSK receiver                                 | 90 |

| Figure 3. 24: parameters of QPSK Demodulator Baseband      | 91 |

| Figure3. 25: after Raised cosine Rx Filter                 | 91 |

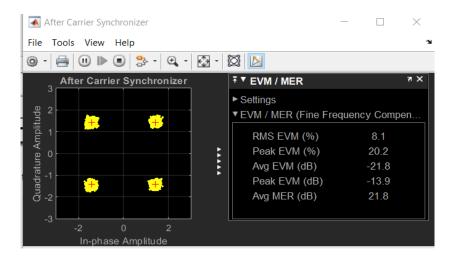

| Figure3. 26: after carrier synchronizer                    | 92 |

| Figure 3. 27: after symbol synchronizer                    | 92 |

| Figure 3. 28: after raised cosine Rx filter                | 93 |

## List of paintings

| Table1. 1:Comparison of FPGAs and FPGA-based SoCs | 12 |

|---------------------------------------------------|----|

| Table1. 2:Comparison of SDR design approaches.    | 16 |

|                                                   |    |

|                                                   |    |

| Table2. 1:Static IP Addresses                     | 67 |

## **General Introduction**

Various forms of communication have evolved over the millennia. The spoken word can be transmitted from one person, and heard or received by another. In modern times town criers hold an annual contest to discover who can shout a comprehensible message over the greatest distance.

However, while the world record is for loudest crier is 112.8 decibels, it can only be understood at less than 100 meters. The desire to communicate more effectively than shouting, is old as speech itself. With modern advances in computing technologies, digital signal processing and digital communication algorithms, artificial intelligence, radio frequency (RF) hardware design, networking topologies, and many other elements have evolved modern communication systems into complex, intelligent, high-performance platforms that can adapt to operational environments and deliver large amounts of information in real-time, error-free. The latest step in communication systems technology is the software-defined radio, or SDR, which adopts the most recent advances in all fields to yield the ultimate transmitter and receiver.

The need for affordable and efficient means to test new and improved transmission methods is endless. Due to the high cost of RF equipment and the limitations imposed by fixed parameter hardware, the idea of a highly dynamic system for testing new methods is seen as highly desirable.

Nowadays and thanks to SDR technologies the realization of transmission chains becomes easy accessible.

our goal through this memory is to exploit the SDR technology and to enter the world of rapid prototyping thanks to the hard soft compatibility offered by this future-oriented equipment and to show how reliable and efficient it is.

we are eager to test SDR prototyping techniques, we will present to you the main types and components of SDR, then we will detail everything about the transmission chains and the types of modulations, finally, we will use the USRP cards under several types of modulations to see their performance.

SDR is a very broad technology it contains many models and types

in this thsis, we will go into the heart of one of the most common SDR cards, the USRP 2920.

the first chapter will bring together all the definitions and concepts of SDR components starting of rf antennas, processors and their main qualities.

we will also see all the software options to better communicate with the cards (GNU radio, MATLAB etc ...).

the second chapter will touch on everything that goes into making a digital transmission chain, the types of digital modulation, we will discuss the propagation in the wireless channel and finally the OFDM modulation.

in the last chapter we will use USRP boards to implement three different types of modulation and observe the signal state and how it behaves

## **CHAPITRE I**

# Introduction to the SDR and USRP's technologies

### 1. Introduction to the Software-Defined Radio

Radio is a system with technology for wireless transmission of information through electromagnetic radiation. In the past, radios consisted of many discrete circuits and electronic devices, which had fixed functions and could not be modified after manufacture. For example, using a traditional radio cannot convert a commercial FM receiver into a digital radio receiver. However, now with software-defined radio (SDR), people can buy a USB DVB-T2 dongle to receive terrestrial TV in a computer and use it as a GPS receiver, or to decode ADS-B (Automatically Dependent Surveillance Broadcast) Signal and get the position of all nearby planes. This shows how SDR is superior to traditional radios in terms of flexibility and reconfigurability.[22]

Many definitions can be found to describe software-defined radio, also known as Software defined radio or SDR. SDR Forum, in cooperation with the Institute of Electrical Engineering and Electronic Engineers (IEEE) P1900.1 group, working to establish the definition of SDR This provides a consistent and clear overview of the technology and its related benefits. Simply put, software-defined radio is defined as 1: "Radio in which part or all of the physical layer functions are defined by software". [23]

Figure 1. 1:Software-defined radio

#### 2. Concepts and architecture

In this section, we will study the general architecture of SDRs, their main components, and their processing requirements. As mentioned in the previous section, SDR plays a vital role in the development of wireless standards due to its flexibility and programmability. This is because most digital signal processing and digital front ends (including channel selection and modulation/demodulation) occur in the digital domain.

This is usually performed in software running on a processor, such as GPP and DSP. However, it can also run-on programmable hardware (i.e., FPGA).

Generally speaking, from the perspective of the transmitter, it is necessary to generate the baseband waveform first, then the intermediate frequency (IF) waveform, generate the radio frequency waveform, and then send it through the antenna. From the receiver's perspective, this RF signal is sampled and demodulated, and then decoded.

In order to provide more details of the process, we study the receiving end of the system as follows. The RF signal from the antenna is amplified, and the tuned RF stage can amplify a certain range of frequency bands. This amplified radio frequency signal is then converted into an analog intermediate frequency signal. An analog-to-digital converter (ADC) digitizes this IF signal into digital samples. Then, it is sent to the mixer stage. The mixer has another input from the local oscillator, the frequency of which is set by the tuning control.

The mixer then converts the input signal to baseband. The next stage is essentially an FIR filter that allows only one signal. This filter limits the signal bandwidth and acts as a decimation low-pass filter. The digital down converter includes a large number of multipliers, adders and shift registers in the hardware to complete the above tasks.

Next, the signal processing stage performs tasks such as demodulation and decoding. This stage is usually handled by dedicated hardware (such as an application specific integrated circuit (ASIC)) or other programmable alternatives (such as FPGA or DSP). As shown in Figure 1 (a) and (b), at a higher level, a typical SDR transceiver includes the following components: signal processing, digital front-end, analog RF front-end, and antenna. [4]

3

#### A. Antenna

SDR platforms usually use multiple antennas to cover a wide range of frequency bands. Antennas are often called "smart" or "smart" because they can select frequency bands and adapt to mobile tracking or interference cancellation. In the case of SDR, antennas need to meet a specific list of requirements, such as self-adaptive (that is, flexibly tuned to Multiple frequency bands), self-alignment (i.e., beamforming capability) and selfhealing (i.e., interference suppression). [4]

#### **B. RF Front End**

This is a radio frequency circuit whose main function is to send and receive signals at various operating frequencies. Its other function is to change the signal to intermediate frequency (IF)/slave intermediate frequency (IF). The operation process is divided into two types, depending on the direction of the signal (i.e., Tx or Rx mode):

- In the transmission path, a digital-to-analog converter (DAC) converts digital samples into analog signals, which are then fed to the RF front-end. This analog signal is mixed with a preset radio frequency, modulated, and then transmitted.

- In the receiving path, the antenna captures radio frequency signals. The antenna input uses a matching circuit to connect to the RF front end to ensure the best signal power transmission. It then passes through a low noise amplifier (LNA) close to the antenna to amplify weak signals and minimize noise levels. This amplified signal is fed into the mixer along with the signal from the local oscillator (LO) to down-convert it to IF. [4]

#### C. Analogy-to-Digital and Digital-to-Analogy Conversion

As mentioned in the previous section, the DAC is responsible for generating the analog signal to be transmitted from the digital samples. On the receiver side, the ADC is located in the radio receiver and is an essential component. The ADC is responsible for converting

continuous-time signals into discrete-time binary coded signals. ADC performance can be described by various parameters, including:

(i) Signal-to-Noise Ratio (SNR): he ratio of signal power to noise power in the output, (ii) resolution: number of bits per sample, (iii) spurious-free dynamic range (SFDR): Carrier signal to the next strongest noise component or spur, and (iv) power consumption. Advances in SDR development have provided impetus for the improvement of ADC performance. For example, because the power consumption of the ADC affects the life of the battery-powered SDR, more energy-efficient ADCs have been developed. [4]

#### **D.** Digital Front End

The digital front end has two main functions [4]:

- Sampling rate conversion (SRC), which is a function to convert samples from one rate to another. This is necessary because the two communicating parties must be synchronized.

- Channelization, including up/down conversion at the transmitter and receiver respectively. It also includes channel filtering, where channels divided by frequency are extracted.

Examples include interpolation and low-pass filters, as shown in Figure 1.2. In the SDR transceiver, the following tasks are performed in the digital front end:

- At the transmitting end (Figure 1.2 (a)), a digital up-converter (DUC) converts the above-mentioned baseband signal to IF. The DAC connected to the DUC then converts the digital IF samples into analog IF signals. Then, the RF upconverter converts the analog IF signal to RF frequency.

- At the receiving end (Figure 1.2(b)), the ADC converts the IF signal into digital samples. These samples are then sent to the next module, the digital down converter (DDC).

DDC includes a digital mixer and a numerically controlled oscillator. DDC extracts the baseband digital signal from the ADC, and after processing by the digital front-end,

forwards the digital baseband signal to the high-speed digital signal processing module.[4]

#### E. Signal Processing

Signal processing operations such as encoding/decoding, interleaving/de-interleaving, modulation/demodulation, and scrambling/descrambling are performed in this block. The coding of the channel is used as an error correction code. Specifically, the encoded signal includes redundancy, and the receiver's decoder uses the redundancy to reconstruct the original signal from the damaged received signal. Examples of error correction codes include convolutional codes, turbo codes, and low-density parity check (LDPC). Due to the data transmission and storage scheme, the decoder constitutes the most computationally intensive part of the signal processing block. The second part considered to be very complex and expensive (in terms of area and power) is the Fast Fourier Transform (FFT) and Inverse FFT (IFFT) as part of the modulation stage. [4]

The signal processing block is usually called the baseband processing block. When discussing SDR, the baseband module is the core of the discussion, because it constitutes most of the digital domain of the implementation. This implementation runs on hardware circuits that can effectively process signals. Examples include ASIC, FPGA, DSP, GPP, and GPU. The second part of the implementation is software, which provides functions and high-level abstractions to perform signal processing operations. In the next section, we will examine the above hardware platforms and analyze various design methods in detail.

[4]

6

Figure 1. 2:SDR architecture. Sub-figure (a) shows SDR from a receiver's point of view, and sub-figure (b) shows SDR from a transmitter's point of view

#### 3. Design Approaches

In this section, we discuss the classification of various SDR design methods for baseband processing blocks, namely GPP, GPU, DSP, FPGA, and methods based on co-design. In this classification, we analyze and compare SDR platforms based on a set of performance indicators in the standards we introduced. The standard includes [4]:

- Flexibility and reconfigurability. Modulation and air interface algorithm and protocol development capabilities, only need to load new software onto the platform

- Adaptability. The SDR platform can adjust its functions as the network or traffic operation requirements change.

- Calculate ability. The processing rate of the SDR platform is Giga Operations per second (GOPS).

- Energy efficiency. Total power consumption (usually within a few hundred milliwatts), especially for mobile and IoT deployments. [4]

- Cost. The total cost of the SDR platform, including time to market, development and hardware costs. [4]

#### A. GPP-based

The first way to implement the SDR platform is to use a general-purpose processor (GPP), or well-known general-purpose computer microprocessor, such as x86/64 and ARM architecture. Examples of SDR platforms that use GPP include Sora, KUAR, and USRP.[4]

#### a. Definition and use:

GPP is a clock-driven and register-based digital circuit that can handle different functions and operate on the data stream expressed in binary.

These GPPs can be used for a variety of purposes, making them ideal for an unlimited number of applications, eliminating the need to build application-specific circuits, thereby reducing the overall cost of running applications. [4]

GPP is usually the preferred hardware platform for academic researchers because of their flexibility, richness, and programmability, which is one of the main requirements of the SDR platform.

In addition, compared with DSP and FPGA, researchers prefer GPP because they are more familiar with GPP and its software framework. From a performance point of view, GPP is rapidly increasing, not only due to technological advancements in CMOS technology, but also due to the increase in the average number of instructions processed per clock cycle. The latter is achieved in different ways, especially using parallelism within and between processors. This led to the development of multi-core GPP. [4]

#### b. Adoption and GPU:

Architecturally, GPP's instruction set includes instructions for different operations, such as arithmetic and logic unit (ALU), data transfer, and I/O. GPP processes these commands

8

in order. Due to sequential processing, GPP is not convenient for high-throughput calculations with real-time requirements (i.e., high throughput and low latency).

For example, using GNU Radio to implement the IEEE 802.11 standard (which requires a 20MHz sampling rate) will be challenging because GNU Radio is limited by the limited processing power of GPP. This will cause the GPP core (of the connected PC) to reach saturation, and the frame will be corrupted and discarded. In addition, wireless protocols require predictable performance to ensure that timing constraints are met.

However, the conditional branch instructions in the GPP instruction set can cause out-oforder execution, which makes it infeasible to achieve predictability. [4]

#### **B.** DSP-based

DSP-based solutions can be considered as special cases of GPP-based solutions, but due to its popularity and unique processing characteristics, it is worth discussing separately. An example of DSP-based SDR is the Atomix platform using TI TMS320C6670 DSP [4].

#### a. Definition and use:

DSP is a special type of microprocessor, optimized to process digital signals. In order to help understand the difference between DSP and GPP, we should first notice that both can implement and handle complex arithmetic tasks.

Tasks such as modulation/demodulation, filtering, and encoding/decoding are usually and often used in applications such as speech recognition and image processing., And communication system.

However, because the DSP architecture (for example, RISC-like architecture, parallel processing) is specifically optimized for arithmetic operations (especially multiplication), they can be implemented faster and more efficiently. Because DSPs can provide high performance with lower power consumption, they are more suitable for deploying SDRs than GPPs. The DSP examples specially designed for the SDR platform are TITMS320C6657 and TMS320C6655.

These DSPs are equipped with hardware accelerators for complex functions, such as Viterbi and Turbo decoders.

9

#### b. Adoption:

As mentioned in the previous section, GPP provides average performance for a wide range of applications. Needless to say, this level of performance may be sufficient for research and academia, but if the system is to be commercially deployed, certain performance requirements must be met. For this reason, compared with GPP, DSP is tailor-made for effective processing of digital signals, using functions such as combined multiplication and accumulation (MAC unit) and parallelism. DSP manufacturers usually sell these products in two ways: optimizing performance and optimizing energy. Therefore, when used for SDR, high-performance and energy-efficient products can be used for BS and edge devices, respectively. [4]

#### C. FPGA-based

Another way to implement SDR is to use programmable hardware, such as FPGAs. An example of an FPGA-based SDR platform is Airblue, based on Xilinx Zynq's IEEE 802.11ah implementation, which uses the same FPGA board to implement a complete communication system with channel coding. [4]

#### a. Definition and use:

FPGA is a group of programmable logic blocks, such as general logic, memory and multiplier blocks, which are surrounded by wiring structures, which are also programmable.

The circuit has the ability to implement any design or function and is easy to update. Although FPGAs consume more power and occupy more area than ASICs, the programmable features are the reason for their increasing adoption in a wide range of applications. In addition, when the reconfiguration delay is in the millisecond level, SDR can seamlessly switch between different modes and protocols.

Another major difference is that ASICs are expensive to manufacture (at least tens of thousands of dollars) and take several months, while FPGAs can be reprogrammed quickly, and the cost is between tens to thousands of dollars, at most. Compared with processors such as GPP and DSP, low-end product cycles and attractive hardware

processing advantages (such as high-speed performance, low power consumption, and portability) make FPGAs a contender that offers the best of both worlds. [4]

Figure 1. 3: Peak performance of GPPs versus FPGAs when performing 64-bit floating point operations

#### **b.** Adoption:

In the past ten years, FPGAs have significantly improved and become more computationally powerful, and now exist in many different versions, such as Xilinx KintexUltraScale and Intel Arria 10.

In addition, the availability of various tool sets makes FPGAs more accessible, which provides them with advantages. This is due to the availability of compilers that can generate register transfer level (RTL) code from high-level programming languages, such as Verilog and VHDL, which need to run on the FPGA. This process is commonly referred to as high-level synthesis (HLS). Examples of such compilers include HDL Coder for MATLAB code and Xilinx HLS or Altera Nios II C2H compilers for C, C++, and System C. HLS allows software engineers to use familiar programming languages to design and implement applications on FPGAs, such as SDR code, namely C, C++, System C, and

MATLAB, without the need for a priori rich knowledge of the target hardware architecture.

These compilers can also be used to speed up or speed up part of the software code running on GPP or DSP, which can slow down or frustrate overall performance. In addition, FPGAs can achieve high performance while still consuming less energy than the previously discussed processors (for example, Intel Stratix 10 FPGAs can achieve up to 100 GFLOPS/W, while NVIDIA GeForce GTX 980 Ti can achieve 23 GFLOPS/W. In addition, Power consumption can be further reduced through the implementation of multiple technologies. These techniques can be at the system, device, and/or architecture level, such as clock gating and glitch reduction. Table I summarizes the widely used FPGA platforms.[4]

|                | FPGA only                    |                               |                           | SoC                                           |                                     |                                   |

|----------------|------------------------------|-------------------------------|---------------------------|-----------------------------------------------|-------------------------------------|-----------------------------------|

|                | Xilinx Kintex-<br>7(XC7K70T) | Intel<br>Cyclone V<br>GX (C5) | Lattice<br>ECP3-<br>70EA) | Xilinx<br>Zynq-<br>700(Z-<br>7020<br>XC7Z020) | Intel<br>Cyclone<br>V SE<br>SoC(A5) | Micro semi<br>SmartFuion2(M2S090) |

| Logic Cells(K) | 65.6                         | 77                            | 67                        | 85                                            | 85                                  | 86.31                             |

| Memory (Mb)    | 4.86                         | 4.46                          | 4.42                      | 4.9                                           | 3.97                                | 4.488                             |

| DSP Slices     | 240                          | 150                           | 128                       | 220                                           | 87                                  | 84                                |

| Cost (USD)     | 130                          | 185                           | 80                        | 110                                           | 110                                 | 155                               |

| Soft Core      | N/A                          | N/A                           | N/A                       | Dual-core<br>ARM<br>Cortex-A9                 | Dual-core<br>ARM<br>Cortex-<br>A9   | ARM Cortex-M3                     |

Table 1. 1: Comparison of FPGAs and FPGA-based SoCs

#### D. Hybrid Design (a.k.a., co-design)

The fourth way to implement SDR is a hybrid approach, combining hardware and software-based technologies into one platform. This is often referred to as a collaborative design or hybrid approach. Examples of SDRs that use co-design methods include WARP and CODIPHY. [4]

#### a. Definition:

Hardware/software co-design has existed as a concept for more than a decade, and it has developed at a faster rate in the past few years because people are increasingly interested in new and different methods to solve integrated circuit design problems. Even if GPP becomes more powerful than ever and adopts a multi-core design, it is obvious that in order to achieve higher performance and realize applications that require real-time processing, designers have to turn their attention to new hardware solutions. On the design scheme, namely, FPGA and ASIC. Co-design means using hardware design methods represented by FPGA architecture and software design methods represented by processors. As more and more applications (such as automobiles, communications, and medical) become more complex and larger, it has become a common practice to design systems that integrate software (such as firmware and operating systems) and hardware. In recent years, due to advances in advanced synthesis and development tools, these tools can not only generate efficient RTL from software code, but also define the interface between the two parties, which makes this feasible. The industry has realized the huge market for collaborative design and has provided various SoC boards, which include multiple processors in addition to the FPGA architecture. For example, the Xilinx Zynq board includes an FPGA structure and two ARM Cortex-A9 processors. In addition to the above advantages, there are other reasons that make co-design more interesting, including faster time to market, lower power consumption (when optimized for this), flexibility, and higher processing speed. The typical hardware system is used as the acceleration software bottleneck. [4]

13

#### b. Adoption:

SDR can be considered as an inherently hybrid or heterogeneous system, which means that hardware and software blocks are required. This is because the control part is usually processed by a general-purpose processor, while other functions, such as signal processing, are handled by a dedicated processor (such as DSP), and sometimes dedicated hardware (such as FPGA) is used for acceleration. This design method fits well with SDR and can be fully utilized to meet certain requirements related to its attractive features. For example, moving part or all of the acceleration module to the FPGA architecture helps push the processing time to the limit to achieve the real-time performance of the actual deployment.

In addition, by carefully implementing RTL optimization techniques, it is possible to develop energy-saving systems for mobile and IoT applications. On the other hand, running most of the MAC layer operations on one processor or multiple processors can facilitate easy reconfiguration. Therefore, different partitioning schemes can be adopted to meet the requirements of the application at hand. It is worth noting that due to the growing demand for such devices, FPGA vendors, namely Intel and Xilinx, are expanding their product base with more SoCs and multi-processor SoCs (MPSoCs).

An example of implementing SDR on MPSoC is. In the white paper, National Instruments (the company that owns USRP) predicts that the future of SDR is essentially a collaborative design implementation, especially with the introduction of FPGAs, which are equipped with a large number of DSP Slice is used to handle intensive signal processing tasks, as shown in Figure 2.3. This can also be seen from the USRPE310 model, which contains a Xilinx ZynqSoC. [4]

14

Figure 1. 4:Number of DSP Slices in Xilinx FPGAs. The values on top of the bars refer to the CMOS technology used.

#### E. Comparison

When we choose different design methods and hardware platforms for a wide range of SDR platforms, we plan to use a cross-platform implementation of one of the wireless communication protocols to perform a one-to-one analysis and comparison. Instead, what is available in the literature is a series of abstract comparisons using a set of benchmarks for high-performance computing (HPC) rather than SDR applications. It is difficult to draw conclusions from these figures alone, because performance comparisons in the SDR field need to be tested in real life.

In Table II, we provide a high-level comparison between the three main design methods as a guide for designers to choose the method that best meets their application specifications. In this comparison, we focus on features that are important to SDR design. However, we do not make assumptions about the best approach and believe that developers are responsible for making their best judgments Depends on the application area. Note that we did not include GPUs in this table because they usually act as coprocessors for GPP, and their addition usually improves performance. We also do not include co-design because it combines GPP and FPGA. [4]

|                    | GPP                      | DSP                         | FPGA                    |

|--------------------|--------------------------|-----------------------------|-------------------------|

| Computation        | Fixed arithmetic engines | Fixed arithmetic<br>engines | User configurable logic |

| Execution          | Sequential               | Partially parallel          | Highly parallel         |

| Throughput         | Low                      | Medium                      | High                    |

| Data rate          | Low                      | Medium                      | High                    |

| Data width         | Limited by bus width     | Limited by bus width        | High                    |

| Programmability    | Easy                     | Easy                        | Moderate                |

| Complex algorithms | Easy                     | Easy                        | Moderate                |

| l/o                | Dedicated ports          | Dedicated ports             | User configurable ports |

| Cost               | Moderate                 | Low                         | Moderate                |

| Power efficiency   | Low                      | Moderate                    | High                    |

| Form factor        | Large                    | Medium                      | Small                   |

Table 1. 2: Comparison of SDR design approaches.

# 4. SDR's Application and operating principle

Software-defined radio (SDR) has been continuously evolving since its inception to provide communication and signal processing capabilities to meet multiple fields and needs from amateur radio to mission-critical wireless systems.

SDR transmits and receives radio data, and quickly and accurately converts between the analog domain and the digital domain on multiple frequency bands, and has functions that are implemented in software rather than hardware. [1]

SDR can be easily integrated into existing or new systems, replacing multiple individual products, and its application can be modified by changing the FPGA or through software on the host.

These modifications are to adapt to technological changes rather than obsolescence. With a powerful long-term investment product, you can share the cost over a longer period of

time, because the service life of the system is usually much longer than that of traditional pure hardware solutions.

With SDR, you only need to upgrade/repair with one supplier, compile all components in a fully integrated boxed platform, save valuable space, and provide a more simplified, user-friendly interface and front-end. [1]

One of the key components that make SDR a technological powerhouse is FPGA (Field Programmable Gate Array); this allows the system to take on new roles, receive updates, and adjust performance parameters for unique environments and conditions. In addition, the system includes signal filtering, mixing, signal amplification, modulation/demodulation, and other forms of digital signal processing (DSP) to ensure that the platform is fully utilized and meets all requirements related to different wireless applications. [1]

The following are some applications/fields of using SDR and unique overall advantages.

In low-latency applications, you can perform all necessary modulation and demodulation on the FPGA to reduce the overall system delay, and adjust the transaction between delay and reliability according to the strategy that best suits the given requirements and highfrequency conditions. [1]

For radar applications, SDR has a configurable radio front end, which allows the same platform to be used for different radar applications because it can operate on different frequency bands of the radio spectrum. For example, airport surveillance radars operate on S-band, while oceans operate on X-band. An SDR platform at a maritime airport can be used to monitor both.

The overall reduction in complexity can save space, cost, time to market and reduce supply chain barriers. Smaller, more efficient platforms allow SDRs to be installed in more environments because they are more compact and easier to use and maintain than traditional hardware-centric options.

In GNSS applications, SDR can receive signals of various frequencies from multiple satellite constellations, which means that a single device can access different navigation systems and can be updated to connect to new satellites launched in the future. [1]

17

# 5. SDRs software

In this section, we will review the existing software tools used for SDR development. For each design method, we discuss compatible development tools and list their functions. [4]

# A. MATLAB and Simulink

MATLAB is widely used in all fields of applied mathematics, university education and research, and industry. MATLAB stands for Matrix Laboratory, and the software is built around vectors and matrices. Therefore, this makes the software particularly useful for solving linear algebra problems, but also very useful for solving algebraic and differential equations and numerical integration. MATLAB has a series of graphics tools that can generate advanced GUI and data graphs in 2-D and 3-D. MATLAB also has multiple toolboxes that can be used to perform communications, signal processing, image processing, optimization, and other professional operations.

MathWorks has created an excellent online tutorial to review basic and advanced concepts, and provides instructor-led tutorials to demonstrate the various features of MATLAB. Most designers start by modeling and simulating the system using MathWorks MATLAB and Simulink.

Through the availability of a wide range of built-in functions and toolboxes, especially for signal processing and communication, developing and testing applications have become very common and widely adopted. However, in order to use these models on different platforms, developers need to use MATLAB Coder and Simulink Coder to generate C/C++ code.[4]

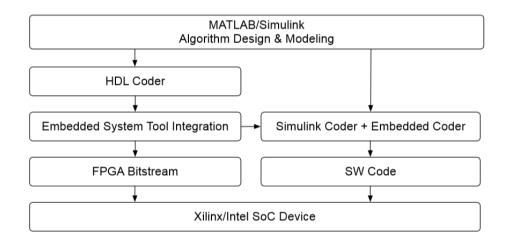

Figure 1. 5: MathWorks SoC design flow.

#### B. Vivado HLS and SDSoC

Xilinx Vivado HLS [86] is a design environment for advanced synthesis. This tool provides a variety of functions to adjust and improve the RTL netlist output compatible and optimized with Xilinx FPGA boards. It accepts input specifications described in multiple languages (such as C, C++, System C, and OpenCL), and generates hardware modules in Verilog or VHDL. Developers can optimize regional and timing solutions by using instructions (optimization process guidelines) and RTL optimization pragmas. These optimizations include loop unrolling, loop pipeline, and operation linking. SDSoC is another tool from Xilinx.

The main difference between these two tools is that the latter has the ability to provide solutions for SoC. SDSoC is built on Vivado HLS and has the same C to RTL conversion capability. The main advantage of using SDSoC is that it will automatically generate a data mover, which is responsible for transferring data between the software on the processor and the hardware on the FPGA. An open-source tool similar to SDSoC is LegUP. [4]

#### C. GNU Radio

It is an open-source software development kit that provides signal processing modules to implement SDR. It runs on a desktop or laptop computer, plus simple hardware, such as USRP B200, can build a basic SDR. It is often used by academia and research communities for simulation and quick setup of SDR platforms. Similar to the System Generator tool and Simulink, it includes different types of blocks such as decoders, demodulators, and filters. It can also connect these blocks in a reliable way and manage data transfer. In addition, it also supports the USRP system. One of the attractive features of GNU Radio is the ability to define and add new blocks. This can be done by programming in C++ or Python. [4]

#### **D. LabVIEW**

A widely used tool from National Instruments that provides a visual programming environment for test, automation, and control applications used by industry and academia. It is similar to GNU Radio and Simulink, and the design can be implemented schematically by connecting chains of various blocks, each of which performs a specific function. It also provides comp5lete support for USRP, enabling rapid prototyping of communication systems. You can use high-level languages (such as C or MATLAB) or use graphical data streams to design the different blocks of the system. [4]

#### E. CUDA

Developed by NVIDIA, it publishes and manages computing platforms and programming models for data parallel computing on GPUs. When the GPU is used as a coprocessor as part of the processing architecture, developers usually use CUDA and hope to take full advantage of its capabilities by accelerating applications.

In order to identify the application components that should run on GPP and the parts that should be accelerated by the GPU, we need to look at the task at hand. The programming languages that can be used in CUDA include C, C++, Python, Fortran, and MATLAB. In addition to a rich library for GPU-related acceleration functions, the toolkit also includes compilers, development tools, and CUDA runtime for developing applications and optimizing them for systems that include GPUs. [4]

## 6. Introduction to the USRP

The Universal Software Defined Radio Peripheral USRP N series (USRP) is the most common SDR platform known to the developer community. It provides a hardware platform for the GNU Radio project.

20

Two generations are available: USRP1 and USRP2. USRP1 (released in 2004) connects to a general-purpose computer via USB and adds a small FPGA. The FPGA board has two functions: routing information and limited signal processing. Due to the limitation of USB 2.0, this generation can support ~ 3MHz bandwidth. The second generation of USRP2 was released in 2008, using Gigabit Ethernet to support 25MHz bandwidth. It includes a Xilinx Spartan 3 FPGA for local processing operations. [4]

Figure 1. 6: Universal Software Radio Peripheral (USRP).

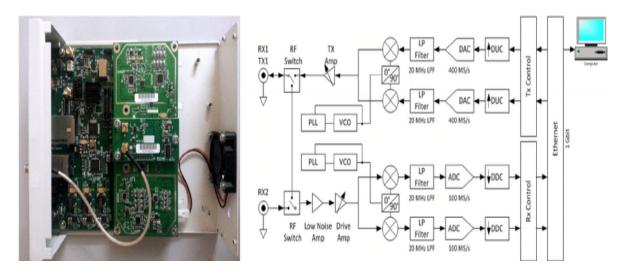

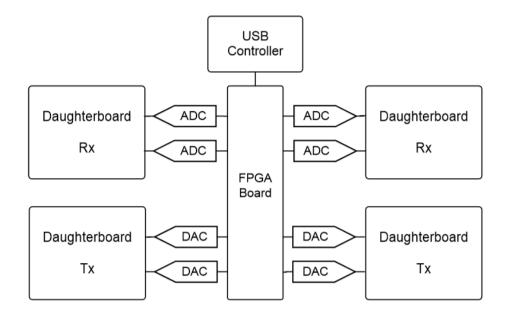

USRP, generally speaking, is a board with ADC and DAC, RF front end, PC host interface and FPGA. The board consists of a motherboard and four daughter boards (two transmitters Tx and two receivers Rx), as shown in Figure 1.6.

The daughter board handles analog operations such as filtering and up/down conversion. They are modular, so they can handle applications running at frequencies up to 6GHz. The FPGA board, depending on the USRP series, handles some signal processing operations, and most of the operations are offloaded to the connected host system.

The USRP platform can be easily set up and used. However, although their performance is suitable for research experiments and rapid prototyping, these platforms do not necessarily meet the requirements of communication standards. In fact, the minimum bandwidth of the used RF, PC host or FPGA components will affect the throughput and timing characteristics of the platform. [4]

Figure 1. 7: USRP board architecture. RF daughterboard selection depends on the application specifications in terms of frequency coverage.

# 7. NI 29xx USRPs applications

Each USRP is equipped with a VERT900 omnidirectional whip antenna, which is a dualband antenna with rated frequencies of 824-960 MHz and 1710-1990 MHz [4]. Softwaredefined radio equipment USRP — USRP-2920 is a tunable radio frequency transceiver with high-speed analog-to-digital converter and digital-to-analog converter for streaming baseband I and Q signals to Host PC. [7]

We use USRP-2920 for the following applications :

Facilitate the interaction between the computer and the user to obtain, analyze, process and present measurement data. It is either a pre-built application with predefined functions or a programming environment for building applications with custom functions. Custom applications are usually used to automate multiple functions of equipment, execute signal processing algorithms, and display custom user interfaces. [6]

Also used for blanks; broadcast FM; public safety; land mobile, low-power unlicensed devices on the industrial, scientific, and medical (ISM) band; sensor networks; cell phones; amateur radio; or GPS. [6]

# 8. CONCLUSION

Software-defined radio has a wide range of advantages and functions and has attracted researchers in the past few years. Because of their modularity, versatility and Digital in nature, many new radio systems are developed in software instead of hardware. Composed of general front-end hardware modules, signal processing SDR is usually performed in a general-purpose processor with a computer. As front-end hardware and general-purpose CPUs continue to become more powerful, developers will continue to implement more advanced software radios. Therefore, in the next few years, SDR will become a more important and influential part of society. In this article, we give a comprehensive overview of the various design methods and hardware platforms used in the SDR solution. This includes GPP, GPU, DSP, FPGA and co-design. We explained the basic architecture and analyzed their advantages and disadvantages. Due to the different characteristics of the design method. [8]

# **CHAPITRE II**

# **The Digital Communication Chain**

# 1. The Digital Communication Chain

## A. Introduction

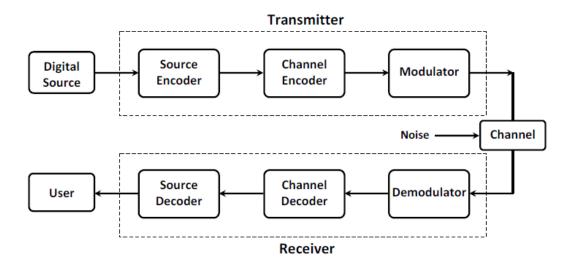

In order to transmit information over long distances, the information needs to be placed in an appropriate form and "carried" by physical media: electromagnetic waves, electrical signals, light, sound waves, etc.

This format requires non-zero duration for data transmission.

In addition, the signal conveying the information may be distorted, and its harmful consequences must be minimized as much as possible. The principal diagram of the digital transmission chain is shown in Figure 2.1. We can distinguish: the source of the message, the transmission medium and the receiver are the problematic data. Source coding and decoding, channel coding and decoding, transmitters and receivers represent the freedom of the designer to implement the transmission system. We will now describe the different elements that make up the transmission chain. [6]

Figure 2. 1:transmission Chain.

#### B. The message source

To achieve digital transmission, the message to be transmitted must be in digital form. If the source delivers an analog message such as the speech (output from a microphone) or the image signal (output from a camera), it must be digitize by sampling the analog message and then quantifying the samples obtained. Each quantified sample is then encoded on M elements binary (traditionally called bits). [6]

#### C. Source coding

The source code encoding principle that found its foundation in the information purpose theory is to eliminate less important binary elements from the message. The latter is a succinct form, consisting of a series of mutually independent binary elements, with values of 0 and 1, and probabilities of 0 p and 1 p. To achieve digital transmission, the message to be transmitted must be in digital form. If the source transmits an analog message, such as voice (microphone output) or image signal (camera output), it must be digitized by sampling the analog message and then quantizing the obtained samples. Then encode each quantized sample into M binary elements (traditionally called bits). [6]

$$D = \frac{1}{Tb} (bit. S^{-1})$$

(2.1)

#### D. Channel coding

Channel coding, also called detector and/or error correction coding, is a specific function of digital transmission and is not equivalent in analog transmission. The purpose of this operation is to improve the transmission quality by inserting so-called redundant binary elements in the message according to the given rules. The disadvantage is that it limits the amount of information that can be used for transmission. A channel decoder that knows the coding rule used in transmission checks whether the rule is still complied with in reception. If this is not the case, it will detect the existence of transmission errors and correct these errors under certain conditions Note: The channel coding function is not always used because it increases the complexity of the transmission equipment, thereby increasing their cost. [6]

#### E. The issuer

The digital message as a sequence of binary elements is abstract. Therefore, in order to transmit this message, it must be associated with a physical representation (in the form of an electrical signal). This is the main function of the transmitter and is usually referred to as modulation operation. More precisely, modulation includes the signal Si (t), i = 1... M, duration T = n Tb associated with each word of n elements output from the message binary output from M = n 2 Select among signals. Therefore, the bit rate D binary message is represented by a signal, and then we define the modulation speed R (in baud), for example the number of signals sent by the modulator per unit time:

$$R = \frac{1}{\tau} (Bauds)$$

(2.2)

Then we talked about multi-ary transmission. In this case, the modulation speed R can be expressed as a function of the bit rate D, and the relationship is as follows:

$$R = \frac{D}{\log_2 M} \tag{2.3}$$

The choice of signal type depends of course on the physical characteristics of the transmission medium through which the signal will pass; therefore, the issuer also ensures that the modulated signal is adapted to the function of the transmission medium. From the processing performed by the transmitter, we can refer to the filtering of the modulated signal to limit its frequency band, thereby allowing multiple users to share the same medium for transmission without the risk of interference

The choice of signal type depends of course on the physical characteristics of the transmission medium through which the signal will pass; therefore, the issuer also ensures that the modulated signal is adapted to the function of the transmission medium. From the processing performed by the transmitter, we can refer to the filtering of the

28

modulated signal to limit its frequency band, thereby allowing multiple users to share the same medium for transmission without the risk of interference. [6]

#### F. Transmission channel

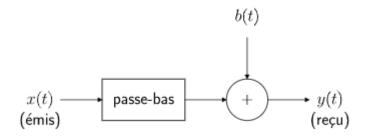

Since channels are physical devices, the signals flowing through them are always analog, even if the information is still encoded by digital messages. Transmission is often interfered by two phenomena that limit the amount of data that can be transmitted: noise, which can be electronic (generated by components), electromagnetic (due to cosmic rays) or interfere with other signals (crosstalk phenomenon); due to physical limitations of the channel or equipment Distortion caused by defects: Signal attenuation, amplitude and phase distortion, echo (multipath), limited channel bandwidth. [7] For these reasons, as the first method, the channel is usually modeled by a low-pass filter and additional noise:

Figure 2. 2: simple model of a channel.

#### G. The receiver

The receiver has the function of reconstructing the message sent by the source from the received signal, including amplification, frequency conversion and demodulation circuits for carrier transmission, filtering, sampling and tapping. Make a decision. Changes in frequency and demodulator can bring the modulated signal back to baseband. In order to minimize the influence of noise, which is an important source of transmission errors, the baseband signal is then filtered and then sampled at the characteristic time. Finally, the decision circuit identifies the value of the binary element transmitted from the received

sample. The choice made by the decision circuit is binary, decision 0 or decision 1, which corresponds to the so-called "detection" operation. [6]

# 2. Digital Modulation

# A. Definition

Modulation is defined as a process in which certain characteristics of the carrier wave change according to the modulating wave. In digital communication, the modulated wave is composed of binary data or its M-ary coded version, and the carrier is a sine wave. Provide greater information capacity, higher data security, faster system availability, and high-quality communications. Therefore, compared with analog modulation technology, digital modulation technology has greater demand because they can transmit a larger amount of data.

According to needs, there are many types of digital modulation techniques and their combinations. Among them, we will discuss the prominent ones. [8]

# **B.** Types of Digital Modulation

## a. ASK – Amplitude Shift Keying

Amplitude shift keying ASK is a kind of amplitude modulation, which represents binary data in the form of signal amplitude changes.

Any modulating signal has a high-frequency carrier. When the binary signal is in ASK modulation, it provides a zero value for the low input, and provides a carrier output for the high input.

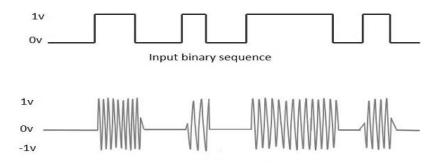

The following figure shows the ASK modulation waveform and its input. [9]

Figure 2. 3: ASK modulated output wave.

In order to find the process of obtaining this ASK modulated wave, let us understand the working principle of the ASK modulator.

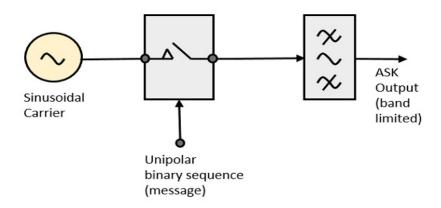

#### ASK Modulator:

The block diagram of the ASK modulator includes a carrier signal generator, a binary sequence from the message signal, and a band-limit filter. The following is the block diagram of the ASK modulator.

*Figure2. 4: ASK generation method*.

The carrier generator sends a continuous high frequency carrier. The binary sequence from the message signal makes the unipolar input high or low. The high signal turns off the switch, allowing the carrier. Therefore, the output will be the carrier signal at high input. When the input is low, the switch opens and no voltage is allowed. Therefore, the output will be very low. The band limit filter shapes the pulse according to the amplitude and phase characteristics of the band limit filter or pulse shaping filter. [9]

#### ASK Demodulator

There are two types of ASK Demodulation techniques. They are:

- Asynchronous ASK Demodulation/detection.

- Synchronous ASK Demodulation/detection.

When the clock frequency of the transmitter matches the clock frequency of the receiver, it is called a synchronization method because the frequency will be synchronized. Otherwise, it is called asynchronous.[9]

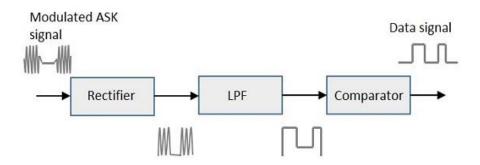

## 1. Asynchronous ASK Demodulator:

Figure 2. 5: asynchronous ASK detector.

The asynchronous ASK detector consists of a half-wave rectifier, a low-pass filter and a comparator. The following is the same block diagram.

The modulated ASK signal is provided to the half-wave rectifier, which provides a positive half output. The low-pass filter suppresses higher frequencies and provides an envelope detection output from which the comparator provides a digital output. [9]

## 2. Synchronous ASK Demodulator:

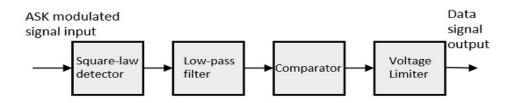

The synchronous ASK detector consists of a square law detector, a low-pass filter, a comparator and a voltage limiter. The following is the same block diagram.

*Figure2. 6:synchronous ASK detector.*

The ASK modulated input signal is provided to the square law detector. The output voltage of the square law detector is proportional to the square of the amplitude modulated input voltage. The low-pass filter minimizes higher frequencies. The comparator and voltage limiter help to obtain a clean digital output. [9]

#### b. Frequency Shift Keying

FSK is a digital modulation technique in which the frequency of the carrier signal changes with the change of the digital signal. FSK is a frequency modulation scheme. The output of FSK modulation wave is high for binary high input frequency and low for binary low input frequency. The binary ones and zeros are called marker frequency and spatial frequency.

The figure below is a schematic diagram of FSK modulation waveform and its input. To find the process of obtaining this FSK modulated wave, please let us understand the working principle of the FSK modulator. [9]

#### **FSK Modulator:**

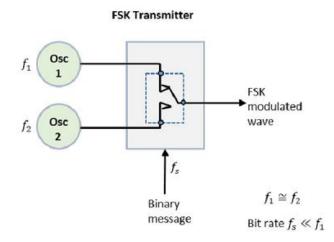

The FSK modulator block diagram includes two oscillators with a clock and input binary sequence. Below is its block diagram.

Figure 2. 7:FSK Transmiter.

Two oscillators that generate higher and lower frequency signals are connected to the switch along with the internal clock. To avoid sudden phase discontinuities of the output waveform during message transmission, the clock is internally applied to the two oscillators. The binary input sequence is applied to the transmitter to select the frequency based on the binary input. [9]

#### **FSK Demodulator:**

There are different ways to demodulate FSK waves. The main methods of FSK detection are asynchronous detectors and synchronous detectors. Synchronous detectors are coherent detectors, while asynchronous detectors are non-coherent detectors. [9]

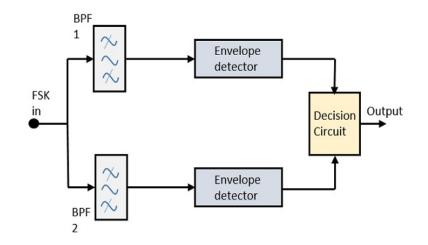

1) Asynchronous FSK Detector:

The block diagram of the asynchronous FSK detector consists of two band-pass filters, two envelope detectors and a decision circuit. The following is a schematic diagram.

Figure 2. 8: Asynchronous FSK Detector.

The FSK signal passes through two band-pass filters BPFs BPF, tuned to the spatial and marker frequencies. The output of these two BPFs looks like an ASK signal, which is provided to the envelope detector. The signal in each envelope detector is asynchronously modulated. The decision circuit selects the more likely output and selects it from any envelope detector. It also reshapes the waveform into a rectangle. [9]

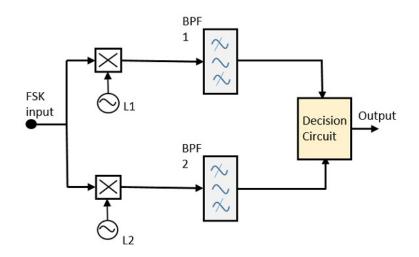

#### 2. Synchronous FSK Detector:

The block diagram of the synchronous FSK detector consists of two mixers with local oscillator circuits, two bandpass filters, and a decision circuit. The following is a schematic diagram.

Figure 2. 9: synchronous FSK Detector.

The FSK signal input is provided to two mixers with local oscillator circuits. These two are connected to two bandpass filters. These combinations act as demodulators, and the decision circuit selects the more likely output and chooses from any one of the detectors. These two signals have the smallest frequency separation.

For two demodulators, the bandwidth of each demodulator depends on their bit rate. This synchronous demodulator is slightly more complicated than the asynchronous demodulator. [9]

#### c. Phase Shift Keying PSK

PSK is a digital modulation technique that changes the phase of the carrier signal by changing the sine and cosine inputs at a specific time. PSK technology is widely used in wireless local area networks, biometrics, contactless operations, and RFID and Bluetooth communications. There are two types of PSK, depending on the phase of the signal offset. They are:

#### 1. Binary Phase Shift Keying BPSK:

This is also called 2-phase PSK or phase reversal keying. In this technique, the sine wave carrier requires two phase reversals, such as 0° and 180°. BPSK is basically a double-

sideband suppressed carrier DSBSC modulation scheme, because the message is digital information. [9]

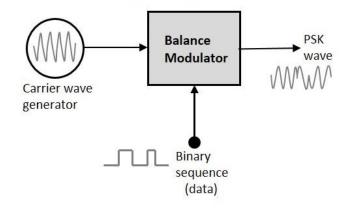

BPSK Modulator: he block diagram of binary phase shift keying consists of a balanced modulator that takes a carrier sine wave as one input and a binary sequence as the other input. The following is a schematic diagram.

Figure 2. 10: BPSK Modulator.

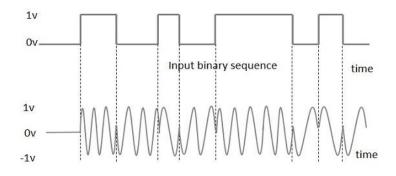

The modulation of BPSK is done using a balanced modulator, which multiplies the two signals applied to the input. For a zero binary input, the phase will be 0°, and for a high input, the phase will be reversed to 180°. The following is an illustration of the BPSK modulated output wave and its given input. [9]

Figure 2. 11: BPSK modulated output wave.

The output sine wave of the modulator will be the direct input carrier or the reverse 180° phase shift 180° phase shift input carrier, which is a function of the data signal. [9]

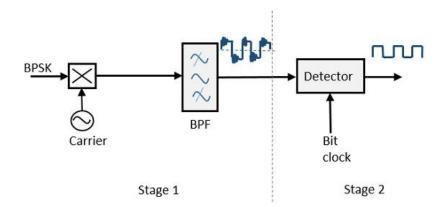

BPSK Demodulator: The block diagram of the BPSK demodulator consists of a mixer with a local oscillator circuit, a band-pass filter, and a two-input detector circuit. The schematic diagram is as follows.

Figure 2. 12: BPSK demodulator.

By recovering the band-limited message signal, with the help of the mixer circuit and the band-pass filter, the first stage of demodulation is completed. Obtain a band-limited baseband signal, which is used to regenerate the binary message bit stream. In the next stage of demodulation, the bit clock rate is determined at the detector circuit to generate the original binary message signal. If the bit rate is a divisor of the carrier frequency, then the bit clock regeneration is simplified. In order to make the circuit easy to understand, you can also insert a decision circuit in the second stage of the test. [9]

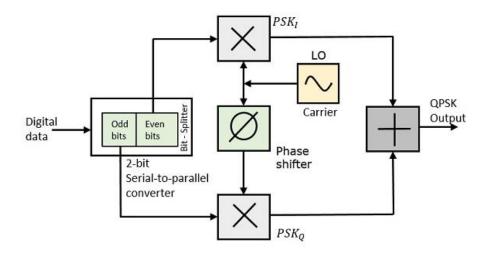

#### 1. Quadrature Phase Shift Keying QPSK:

This is the phase shift keying technology, in which the sine wave carrier undergoes four phase inversions of 0°, 90°, 180° and 270°. If this technique is further expanded, PSK can also be completed with eight or sixteen values, depending on the requirements Quadrature Phase Shift Keying QPSK is a variant of BPSK, and it is also a double-sideband suppression carrier DSBSCDSBSC modulation scheme, which sends two-digit information