#### UNIVERSITE DE SAAD DEHLEB DE BLIDA

## Faculté des sciences Département d'informatique

# **MEMOIRE DE MAGISTER**

Option: Ingénierie des systèmes et de la connaissance

# DEVELOPPEMENT D'UNE APPROCHE DE COSYNTHESE D'INTERFACES DE COMMUNICATIONS POUR LE CODESIGN

Par

#### **BERRHAIL Fouaz**

## Devant le jury composé de :

| Mme H. ABED       | Maître de Conférences Université de Blida | Présidente   |

|-------------------|-------------------------------------------|--------------|

| Mlle K. BENATCHBA | Maître de Conférences INI, Alger          | Examinatrice |

| Mme F. SITAYEB    | Docteur INI, Alger                        | Examinatrice |

| Mme S. OUKID      | Maître de Conférences Université de Blida | Invitée      |

| M.M. KOUDIL       | Maître de Conférences INI, Alger          | Rapporteur   |

Blida 2006

A ma très chère mère. A mon cher père.

#### ملخص

مع ارتفاع نسبة تعقد الأنظمة المختلطة، فان توليد وسائط الاتصال في سير التصميم المتنافس (Codesign) أصبح عملية معقدة ولقد أصبح من الضروري إيجاد طرق آلية جديدة ذات مستوي عالي، تسمح بالتحكم في التعقيد، وتساعد المصممين في توليد وسائطهم.

في الأنظمة المختلطة (برنامج/عتاد) يمكننا تمبيز ثلاثة أنواع من الاتصالات: اتصال بين برنامج وبرنامج، اتصال بين عتاد وعتاد، اتصال بين برنامج وعتاد. النوع الأول و الثاني يطرحان اشكالات قليلة لأنهما يتطلبان آلية بسيطة من اجل الاتصال. على العكس النوع الأخير فانه يطرح عدة إشكالات، بسبب عدم تجانس المركبات المستعملة في القسمين (عتاد/برنامج)، طبيعة المعالجات، اختلاف السرعات...الخ. إشكال آخر يطرح من اجل عملية توليد الوسائط و المتمثل في عدم معرفة بعض تفاصيل الوسيطة إلا بعد إجراء التقسيم.

أ ردنا من خلال هذه الرسالة تقديم طريقة آلية ذات مستوى عالي تسمح بتوليد وسائط الاتصال لأجل التصميم المتنافس، و التي تتمثل في إجراء تصفيات متتالية لنص تمييز .Java ولقد قمنا بحل بعض الإشكالات التي صادفناها خلال هته العملية، حلول اقترحت: من اجل تحليل نص التمييز، وصف المركبات البنيوية، و مختلف مراحل توليد الوسائط.

الكلمات الرئيسية: Codesign, Cospecification, Analysis, Interface cosynthesis

#### **RESUME**

Au fur et à mesure que la complexité des systèmes mixtes croît, la cosynthèse d'interfaces de communication pour le codesign devient un processus complexe. Il devient nécessaire de définir de nouvelles méthodes automatiques de haut niveau permettant de maîtriser la complexité et d'aider les concepteurs à synthétiser ses interfaces.

Dans les systèmes mixtes (matériel/logiciel), il est possible de distinguer trois types de communication: communication logiciel/logiciel, communication matériel/matériel, et communication logiciel/matériel. Le premier et le deuxième type de communication posent moins de problèmes puisqu'ils nécessitent un mécanisme simple pour la communication. Par contre, le dernier type pose plus de problèmes, en raison de l'hétérogénéité des composants utilisés pour les deux parties, la nature des traitements, les différences de vitesses, etc. Un autre problème posé par l'étape de cosynthèse d'interface est dû au fait que certains détails de l'interface ne sont connus qu'à l'issue de l'étape de partitionnement.

Le présent mémoire introduit une approche automatique de haut niveau pour la cosynthèse d'interfaces de communication dans le codesign, elle consiste à procéder par affinements successifs sur le code de cospécification Java. Nous tentons de résoudre un certain nombre des problèmes rencontrés durant la cosynthèse. Des solutions sont proposées pour l'analyse de code, la description des composants architecturaux, et les différentes étapes de cosynthèse d'interfaces.

Mots clés: Codesign, Cospécification, Analyse, Cosynthèse d'interfaces.

**ABSTRACT**

As the complexity of the mixed systems grows, communication interface synthesis during the

codesign process gets harder and harder. It becomes necessary to define new high-level

automated methods that allow mastering complexity and helping designers to synthesize their

interfaces.

In mixed systems (made of hardware and software), it is possible to distinguish three types of

communication: communication between software and software, communication between

hardware and hardware, and communication between software and hardware. The first and the

second communication types raise less problems since they require simple communication

mechanisms. The last type raises more problems, because of the heterogeneity of the components

used for the two parts, the nature of the treatments, the differences of speeds... Another problem

in interface cosynthesis is due to the fact that some interface details are only known at the end of

the partitioning process.

This document introduces a high-level automatic approach for the communication interface

synthesis in Codesign. It proceeds by successive refinements on the Java code of the

cospecification. We tried to solve some of the synthesis problems. Solutions are proposed for:

code analysis, architectural component description, and the different phases of interface

cosynthesis.

Keywords: Codesign, Cospecification, Analysis, Interface cosynthesis.

#### REMERCIEMENTS

Je tiens à remercier en premier lieu mon dieu « *ELLAH* » tout puissant qui m'a accordé la volonté et le courage pour la réalisation de ce projet.

Je tiens à remercier chaleureusement monsieur KOUDIL Mouloud, Maître de conférences à l'institut national d'informatique d'Alger, mon promoteur et le directeur de ce travail, pour ses larges expériences dans le domaine de codesign, son gentiment et amabilité, ses conseils et disponibilité, et pour avoir accepté de diriger ce travail et de corriger ce document.

J'adresse mes remerciements à Mme H. ABED, Maître de Conférences à l'Université de Blida, de m'avoir fait l'honneur de présider mon jury de mémoire.

Pour m'avoir fait l'honneur de participer au jury de mémoire, je remercie Mlle K. BENATCHBA Maître de Conférences à l'Institut National d'Informatique Alger, Mme F. SITAYEB Docteur à l'Institut National d'Informatique d'Alger, Mme S. OUKID Maître de Conférences à l'Université de Blida, la directrice du laboratoire de recherche et de développement des systèmes informatisés (LRDSI).

Je remercie aussi monsieur Benaouda Abd el hafid, mon promoteur de PFE et le directeur de centre de calcul de l'Université de Ferhat Abbas Sétif, de son encouragement et soutien.

Un immense merci à mes parents (ma mère et mon père), mes frères, mes sœurs et mes proches qui m'ont apporté leur encouragement et soutien tout au long de mes études.

Je remercie aussi l'ensemble des enseignants, qui ont contribué à notre formation.

Enfin, mes remerciements vont à ceux qui ont participés, plus ou moins indirectement à mon mémoire.

Merci à mes intimes amis : Kadour Bachir, Tabet Adel.

Merci à mes collègues de post graduation (Université de Blida): B.Maamar, H.Hamza, F.Messaouda, B.Djawida, sans oublier Amina et Mehdia.

Merci à mes amies : Kamel, Anis, Abd el salem, Yazid, Ramdan, Hocine, Farid, Hakim, Abd el kader.

Merci à tous ce qui nous ont aidé de près ou loin.

## TABLE DES MATIERES

| RESUME                                                                           |    |

|----------------------------------------------------------------------------------|----|

| ABSTRACT                                                                         |    |

| REMERCIEMENTS                                                                    |    |

| TABLE DES MATIERES                                                               |    |

| LISTE DES ILLUSTRATIONS                                                          |    |

| LISTE DES TABLEAUX                                                               |    |

| INTRODUCTION                                                                     | 15 |

| CHAPITRE 1 CODESIGN MATERIEL/LOGICIEL                                            | 19 |

| 1.1 Introduction                                                                 | 19 |

| 1.2 Technique classique de conception des systèmes embarqués                     | 20 |

| 1.2.1 Définition d'un système embarqué                                           |    |

| 1.2.2 Problèmes de conception d'un système embarqué                              |    |

| 1.3 Comparaison entre conception traditionnelle et le codesign matériel/logiciel |    |

| 1.4 .Quelques définitions pour le codesign                                       |    |

| 1.5 Pourquoi le codesign Matériel/logiciel ?                                     |    |

| 1.6 Intérêts du codesign                                                         |    |

| 1.7 Domaines d'application du Codesign                                           |    |

| 1.8 Architectures cible utilisées pour le codesign                               |    |

| 1.8.1 Organisation de l'architecture                                             |    |

| 1.8.2 Composants de l'architecture                                               |    |

| 1.9 Conclusion                                                                   | 29 |

| CHAPITRE 2 DIFFERENTES ETAPES DE PROCESSUS DU CODESIGN                           | 31 |

| 2.1 Introduction                                                                 |    |

| 2.2 Etapes de processus de codesign                                              |    |

| 2.2.1 La cospécification                                                         |    |

| 2.2.2 La modélisation                                                            |    |

| 2.2.3 Le partitionnement                                                         |    |

| 2.2.4 La cosynthèse d'interfaces de communication                                |    |

| 2.2.5 La covalidation/covérification                                             |    |

| 2.3 Conclusion                                                                   | 45 |

| CHAPITRE 3 PROBLEMATIQUE DE COSYNTHESE D'INTERFACES                              | DE |

| COMMUNICATIONS                                                                   |    |

| 3.1 Introduction                                                                 | 40 |

| 3.3 La synthèse du matériel                                                     | 47    |

|---------------------------------------------------------------------------------|-------|

| 3.4 La Cosynthèse de la communication et d'interfaces                           |       |

| 3.4.1 Classification des schémas de communications dans les systèmes mixtes     | 50    |

| 3.4.2 Niveaux d'abstraction des interfaces                                      | 52    |

| 3.4.3 Types de synthèse d'interfaces (Types de conception des interfaces)       | 53    |

| 3.4.4 Composants et protocoles de communication                                 |       |

| 3.5 Position du problème de cosynthèse d'interfaces                             | 55    |

| 3.6 Conclusion                                                                  | 58    |

| CHAPITRE 4 DIFFERENTES APPROCHES POUR LA COSYNTHESE D'INTERFA                   |       |

| DE COMMUNICATION                                                                | 59    |

| 4.1 Introduction                                                                | 59    |

| 4.2 Différents approches de synthèse d'interfaces de communications             | 60    |

| 4.2.1 L'approche de Kalavade [44]                                               |       |

| 4.2.2 L'approche Vulcan [64]                                                    | 61    |

| 4.2.3 Approche de sélection et d'allocation de communication à partir de protoc | coles |

| abstraits [21]                                                                  |       |

| 4.2.4 Méthodologie SpecSyn [26, 27, 28]                                         |       |

| 4.2.5 Méthodologie de l'université Brauschweig Cosyma [32, 25]                  |       |

| 4.2.6 Approche proposée par [8]                                                 |       |

| 4.2.7 L'approche IPCHINOOK [18]                                                 |       |

| 4.2.8 Approche de Conception des systèmes hétérogènes multilangage [34]         |       |

| 4.2.9 L'environnement MUSIC [19]                                                |       |

| 4.2.10 Approche de Génération des Interfaces de Communication pour les Syste    |       |

| multiprocesseurs Monopuces [30]                                                 | /0    |

| 4.2.11 Méthodologie Ptolemy (Université de Californie/Berkeley) [12, 13, 49, 78 |       |

| 4.2.12 Autres approphes de aggrathèse d'interfaces                              |       |

| 4.2.12 Autres approches de cosynthèse d'interfaces                              |       |

| 4.3 Comparaison 4.4 Conclusion                                                  |       |

| 4.4 Conclusion                                                                  | /0    |

| CHAPITRE 5 SPECIFICATION DU SYSTEME MIXTE                                       | 77    |

| 5.1 Introduction                                                                | 77    |

| 5.2 Présentation générale de l'approche proposée                                | 78    |

| 5.3 Formalisme de cospécification orienté objets                                |       |

| 5.4 Motivation du choix d'un formalisme orienté objets                          |       |

| 5.5 Langage Java pour la cospécification                                        |       |

| 5.6 Motivation du choix du langage Java                                         |       |

| 5.7 Modèle orienté objet pour les entités de l'application et les composants    |       |

| l'architecture cible                                                            |       |

| 5.8 Conclusion                                                                  | 85    |

| CHAPITRE 6 ANALYSE DU CODE DE LA COSPECIFICATION                                | 86    |

| 6.1 Introduction                                                                | 86    |

|                                                                                 |       |

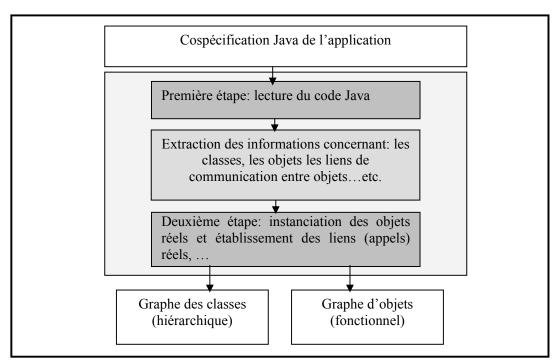

| 6.2 Principe de l'analyse de la cospécification                                     | 86    |

|-------------------------------------------------------------------------------------|-------|

| 6.3 Différentes étapes de l'analyse                                                 |       |

| 6.3.1 Première étape de l'analyse                                                   | 88    |

| 6.3.2 Deuxième étape de l'analyse                                                   | 88    |

| 6.4 Le résultat de l'analyse de la cospécification                                  | 88    |

| 6.4.1 Graphe des classes (hiérarchique)                                             |       |

| 6.4.2 Graphe d'instances d'objets (fonctionnel)                                     |       |

| 6.5 Conception de l'analyse                                                         |       |

| 6.5.1 Les informations à extraire de la spécification Java                          |       |

| 6.5.2 Structures de données proposées et hiérarchie des structures de données       |       |

| 6.5.3 Déroulement de l'analyse de la cospécification                                |       |

| 6.6 Problèmes rencontrés et cas particuliers                                        |       |

| 6.6.1 Cas des classes internes                                                      |       |

| 6.6.2 Problème de détection des instances d'objets                                  |       |

| 6.6.3 Traitement des objets internes ou objets cachés                               |       |

| 6.6.4 Problème des variables globales et de la cohérence de la mémoire              |       |

| 6.6.5 Cas des appels internes de méthodes et des méthodes privées                   |       |

| 6.6.6 Cas de deux instances d'objets portes un nom identique dans des i             |       |

| différentes                                                                         |       |

| 6.7 Présentation de l'outil développé pour l'analyse                                |       |

| 6.8 Conclusion                                                                      |       |

| PROTOCOLES DE COMMUNICATION                                                         |       |

| 7.1 Introduction                                                                    |       |

| 7.2 Principales fonctionnalités de l'environnement de description de l'architect    |       |

| 7.3 Composition et description de l'architecture cible                              | 107   |

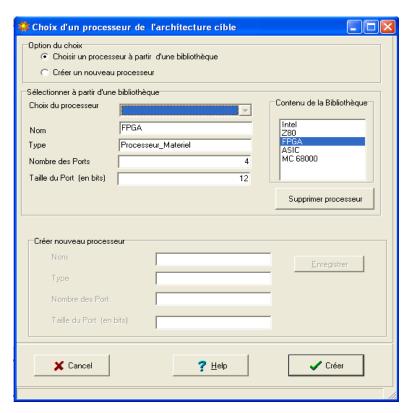

| 7.3.1 Description des composants processeurs                                        | 107   |

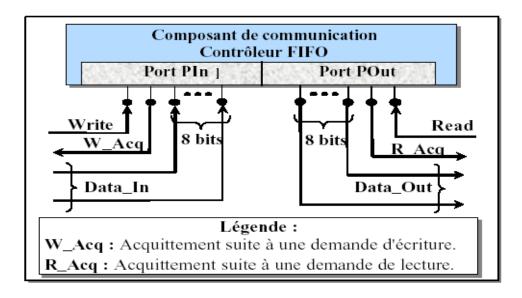

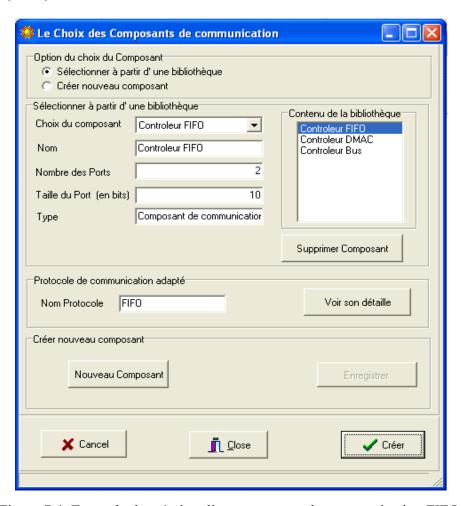

| 7.3.2 Description des composants de communication                                   |       |

| 7.3.3 Choix d'un protocole de communication et connexion des composants             | 111   |

| 7.3.4 Description des lignes des ports physiques des composants architecturaux      | t 115 |

| 7.3.5 Connexion et brochage des lignes des ports physiques des composants           | 116   |

| 7.4 Conclusion                                                                      | 117   |

| CHAPITRE 8 APPROCHE POUR LA COSYNTHESE D'INTERFACE<br>COMMUNICATION                 |       |

| 8.1 Introduction                                                                    | 110   |

| 8.2 Présentation générale de l'approche de cosynthèse d'interfaces de communica     |       |

| 8.3 Avantages de l'approche proposée pour la synthèse d'interfaces                  |       |

| 8.4 Etapes de la cosynthèse d'interfaces de communication                           | 121   |

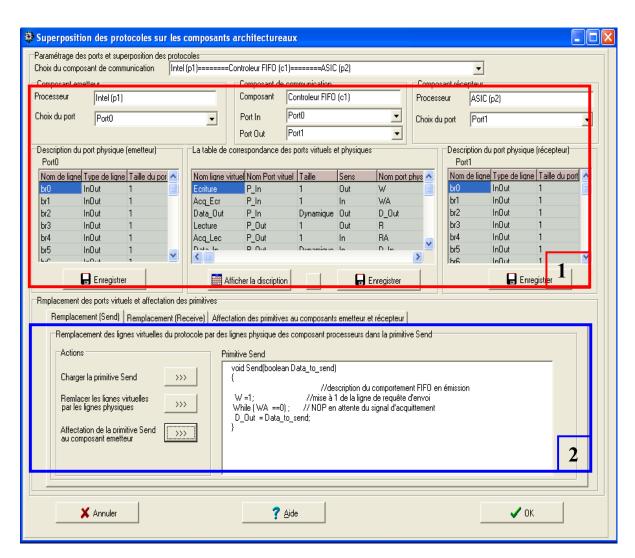

| 8.4.1 Paramétrage et superposition des ports et des protocoles virtuels             |       |

| composants de l'architecture cible                                                  |       |

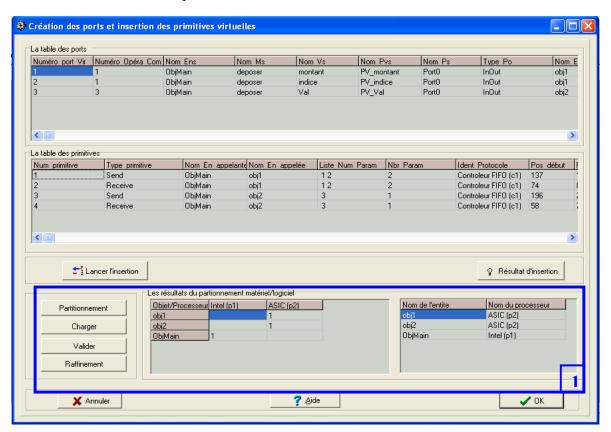

| 8.4.2 Création des ports virtuels et insertion des appels aux primitives virtuelles |       |

| 5.1.2 esection des ports virtuels et insertion des appeis dux primitives virtuelle. | J 120 |

|                                                                                     |       |

| 8.4.3 Processus d'affinement des appels aux primitives virtuelles dans le l'application | 135           |

|-----------------------------------------------------------------------------------------|---------------|

| 8.5 Conclusion                                                                          |               |

| 8.3 Coliciusion                                                                         | 140           |

| CHAPITRE 9 MISE EN OEUVRE ET TEST DE L'APPROCHE DE COS                                  | SYNTHESE      |

| D'INTERFACE PROPOSEE                                                                    | 141           |

|                                                                                         | 1.41          |

| 9.1 Introduction                                                                        |               |

| 9.2 Présentation du jeu de test                                                         |               |

| 9.2.1 Cospécification de l'application                                                  |               |

| 9.2.2 Analyse du code de la cospécification                                             |               |

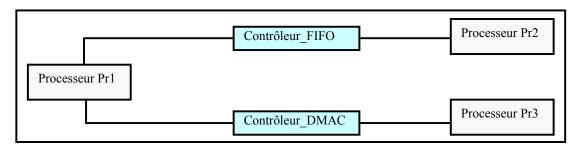

| 9.2.3 Description de l'architecture cible                                               |               |

| 9.2.4 Choix d'un protocole de communication                                             |               |

| 9.2.5 Superposition des protocoles sur les composants processeurs de l'                 |               |

| cible                                                                                   |               |

| 9.2.6 Création des ports virtuels et insertion des appels aux primitives virtue         |               |

| 9.2.7 Le partitionnement.                                                               | 149           |

| 9.2.8 Affinement des appels de primitives virtuelles dans les entités de l'app          |               |

| 9.3 Traitement de quelques problèmes et cas particuliers                                |               |

| 9.3.1 Cas d'une fonction renvoyant un résultat                                          |               |

| 9.3.2 Cas de transmission de variables complexes                                        | 151           |

| 9.3.3 Problème d'un composant processeur possédant plus d'un cor                        | nposant de    |

| communication                                                                           |               |

| 9.3.4 Problème de correspondance de type entre les ports physiques et les p             | orts virtuels |

| dans le processus d'affinement                                                          |               |

| 9.3.5 Problème de correspondance de taille entre les ports physiques et les p           | orts virtuels |

| dans le processus d'affinement                                                          |               |

| 9.4 Conclusion                                                                          | 154           |

|                                                                                         |               |

| CONCLUSION                                                                              | 155           |

| DEPENDINGER                                                                             |               |

| REFERENCES                                                                              |               |

## LISTE DES ILLUSTRATIONS

| Figure 1.1: Approche de conception traditionnelle [46]                                         | . 22 |

|------------------------------------------------------------------------------------------------|------|

| Figure 1.2: Approche de conception conjointe [46]                                              | . 23 |

| Figure 1.3: Croissance de la production des produits électroniques (systèmes embarqués) [1].   | . 25 |

| Figure 2.1: Les différentes étapes du processus de codesign [46]                               | . 32 |

| Figure 2. 2: Flot de conception pour une spécification homogène [34].                          | . 33 |

| Figure 2.3: Flot de conception pour une spécification hétérogène [69].                         | . 34 |

| Figure 2.4: Flot de conception pour une spécification multilangage [34]                        | . 34 |

| Figure 2.5: Différentes classes d'approches utilisée dans la cospécification [46].             | . 35 |

| Figure 2.6: Création d'un modèle interne (ex: réseaux de Petri)                                | . 37 |

| Figure 2.7: Schéma générique d'une architecture cible.                                         | . 40 |

| Figure 2. 8: Principe du flot de cosynthèse                                                    | . 42 |

| Figure 3.1: Interfaces permettant à deux composants de communiquer par un bus                  | . 49 |

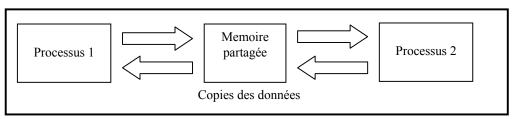

| Figure 3.2: Communication par mémoire partagée.                                                | . 50 |

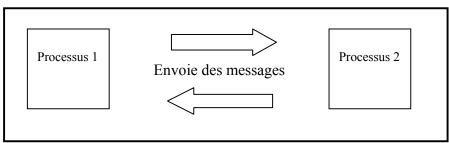

| Figure 3.3: Communication par passage de message.                                              | . 51 |

| Figure 3.4: Problème de cosynthèse de la communication.                                        | . 56 |

| Figure 3.5: Synthèse d'interfaces de communication                                             | . 57 |

| Figure 3.6: Affinement de la communication [34]                                                | . 58 |

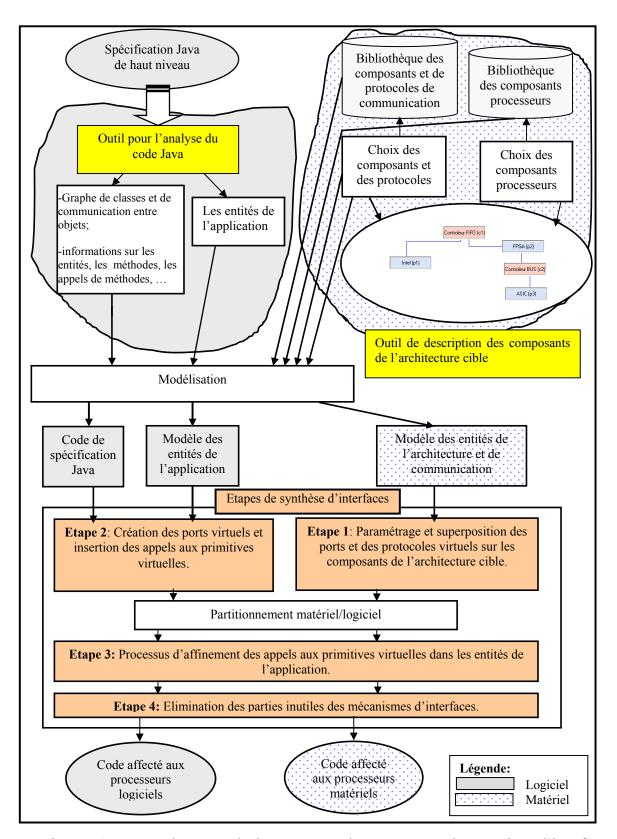

| Figure 5.1: Présentation générale de notre approche et ses étapes de cosynthèse d'interface    | . 80 |

| Figure 5.2: Modèle générique représente les différentes unités d'un composant [46]             | . 85 |

| Figure 6.1: Etapes de l'analyse de la cospécification Java.                                    | . 87 |

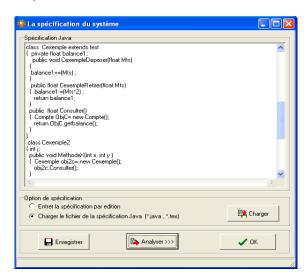

| Figure 6.2: Outil permettant la lecture du code de la cospécification Java                     | . 87 |

| Figure 6.3: Exemple d'un graphe de classes (hiérarchique)                                      | . 89 |

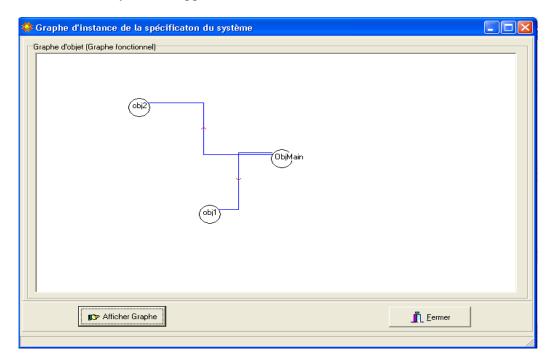

| Figure 6.4: Exemple d'un Graphe d'instances d'objets.                                          | . 90 |

| Figure 6.5: Exemple de structure générale d'un programme de spécification en Java              | . 92 |

| Figure 6.6: Hiérarchie des principales structures de données proposées pour le graphe des clas |      |

| Figure 6.7: Hiérarchie des principales structures de données proposées pour le graphe d'objet. | . 93 |

| Figure 6.8: Exemple de détection d'une classe et la structure de données correspondante        | 94   |

| Figure 6.9: Exemple de détection des méthodes membres et la structure de données propo-                                               | sée 94 |

|---------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 6.10: Exemple de détection des appels aux méthodes et la structure de données p                                                |        |

| Figure 6.11: Exemple de classes internes dans le code de cospécification                                                              |        |

| Figure 6.12: Exemple de problème des variables globales                                                                               | 98     |

| Figure 6.13: Exemple d' appels internes des méthodes                                                                                  | 99     |

| Figure 6.14: Exemple de concaténation des noms d'objets                                                                               | 100    |

| Figure 6.15: Exemple de spécification Java                                                                                            | 101    |

| Figure 6.16: Environnement d'analyse pour l'extraction des informations de l'application                                              | 102    |

| Figure 6.17: Graphe d'instance correspondant à la spécification Java de l'exemple (figu                                               |        |

| Figure 6.18: Graphe des classes correspondant à l'exemple (figure 6.15)                                                               | 103    |

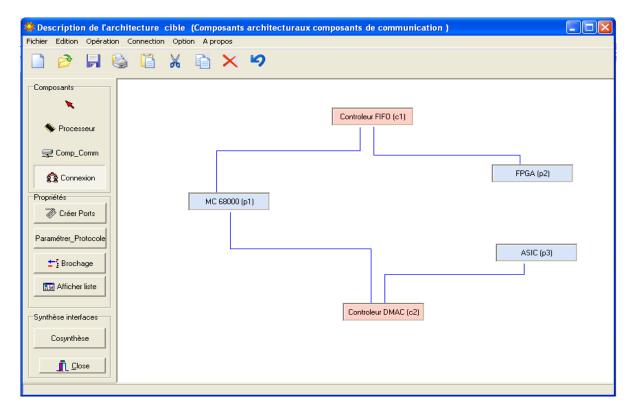

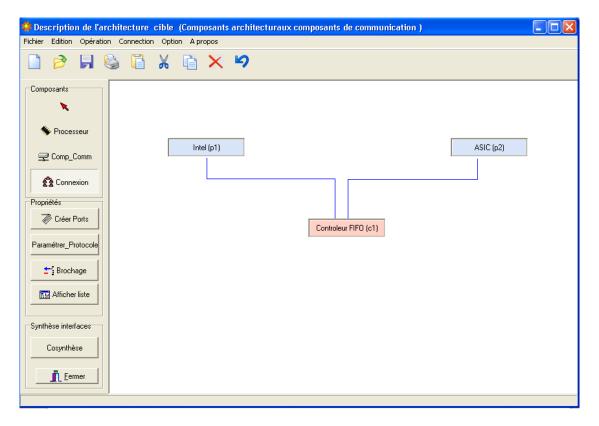

| Figure 7.1: Exemple de description d'une architecture cible à l'aide de l'environnement dé                                            |        |

| Figure 7.2: Exemple pour la création d'un processeur Matériel                                                                         | 108    |

| Figure 7.3: Exemple d'un composant de communication contrôleur FIFO [46]                                                              | 109    |

| Figure 7.4: Exemple de création d'un composant de communication FIFO                                                                  | 110    |

| Figure 7.5: Modèle de protocole de communication [46]                                                                                 | 111    |

| Figure 7.6: Exemple d'un port virtuel.                                                                                                | 112    |

| Figure 7.7: Exemple d'un Protocole de communication.                                                                                  | 113    |

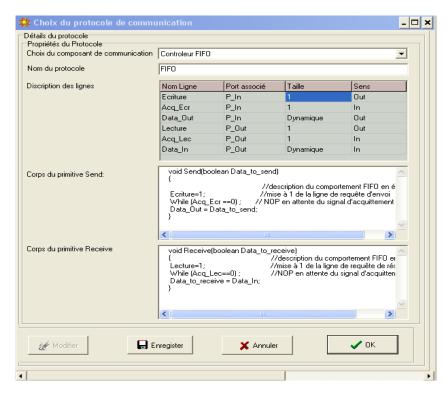

| Figure 7.8: Détail du protocole FIFO rangé dans la bibliothèque                                                                       | 113    |

| Figure 7.9: Description de nouveaux composants et protocoles de communication                                                         | 115    |

| Figure 7.10: Exemple de description des ports physiques des composants architecturaux.                                                | 116    |

| Figure 7.11: Brochage des ports des composants de l'architecture cible                                                                | 117    |

| Figure 8.1: Etapes de l'approche de cosynthèse d'interfaces de communication                                                          | 120    |

| Figure 8.2: Exemple de correspondance entre les lignes des ports virtuels du protocole les ports physiques des composants processeurs |        |

| Figure 8.3: Exemple de remplacement des ports virtuels par les ports physiques                                                        | 125    |

| Figure 8.4: Exemple de création de ports virtuels                                                                                     | 127    |

| Figure 8.5: Exemple d'insertion des appels aux primitives Send/Receive                                                                | 130    |

| Figure 8.6: Exemple des modifications effectuées sur une méthode d'un objet appelé                                                    | 132    |

| Figure 8.7: Exemple de déclenchement d'une méthode appelée                                                                            | 134    |

| Figure 8.8: Exemple d'insertion du corps de la primitive Send d'un protocole FIFO                                                     | 137    |

| Figure 8.9: Algorithme du processus de réduction des mécanismes d'interfaces                                                          | 139    |

| Figure 9.1: Editeur permet d'entrer la cospécification Java de l'application                                   | 141 |

|----------------------------------------------------------------------------------------------------------------|-----|

| Figure 9.2: Exemple de cospécification Java d'un système                                                       | 142 |

| Figure 9.3: Graphe d'instance de l'exemple de cospécification précédent (figure 9.2)                           | 143 |

| Figure 9.4: Exemple de composition d'une architecture cible                                                    | 144 |

| Figure 9.5: Choix d'un protocole de communication dans une bibliothèque                                        | 145 |

| Figure 9.6: Paramétrage et superposition des protocoles sur les composants architecturaux                      | 146 |

| Figure 9.7: Exemple de création des ports virtuels et insertion des primitives de l'exe précédent (figure 9.2) | -   |

| Figure 9.8: Résultat de l'insertion des primitives de l'exemple de la figure 9.2                               | 148 |

| Figure 9.9: Exemple d'affinement des appels aux primitives de l'application (résultat de l d'affinement)       |     |

| Figure 9.10: Exemple de communication avec deux composants de communication                                    | 151 |

| Figure 9.11: Transformation de la primitive "Send/Receive" pour le transfert par paquets                       | 153 |

## LISTE DES TABLEAUX

| Tableau 3.1: Niveaux d'abstraction des communications inter-modules [34].            | 53  |

|--------------------------------------------------------------------------------------|-----|

| Tableau 6.1: Table de mécanisme de cohérence de la mémoire                           | 98  |

| Tableau 7. 1: Structure de la bibliothèque de protocoles.                            | 114 |

| Tableau 8.1: Table de correspondance entre les ports physiques et les ports virtuels | 124 |

| Tableau 8.2: Table des entités et composant d'affectation après partitionnement      | 127 |

| Tableau 8.3: Table de correspondance et caractéristiques des ports                   | 128 |

| Tableau 8.4: Structure de la table des primitives                                    | 129 |

| Tableau 9.1: Partitionnement des objets de l'application                             | 149 |

#### INTRODUCTION

La conception des systèmes mixtes (matériels/logiciels) est un processus difficile: la complexité croissante des applications, l'évolution rapide des technologies de réalisation des circuits intégrés nécessitent l'utilisation de nouvelles méthodes de conception qui doivent être capables de tenir compte de nombreuses contraintes : temps, flexibilité, fiabilité, complexité, consommation.

Les techniques classiques de la conception des systèmes (mixtes) contenant du matériel et du logiciel consistaient à séparer la partie matérielle de la partie logicielle très tôt dans le cycle de conception (indépendance de deux parties jusqu'à la phase d'intégration). Les concepteurs du matériel n'avaient donc que peu de connaissances sur la partie logicielle. Il en était de même pour les concepteurs du logiciel. Souvent, de nombreux problèmes étaient rencontrés à la phase d'intégration. Ce type des méthodes pose souvent quelques problèmes, du fait de la complexité croissante des systèmes, l'hétérogénéité des systèmes, la flexibilité des systèmes, la simulation impossible, la difficulté de corriger les erreurs et de maintenir le système en fonctionnement normal, etc.

Tous ces problèmes et d'autres mettent l'accent sur la nécessité de disposer d'une méthodologie qui respecte les exigences de plus en plus grandes en performance, délais, coûts, testabilité, etc. Cette méthodologie est appelée Codesign "Concurrent design" ou la conception concurrente. Elle consiste à prendre en considération l'interaction entre les deux parties du système (matérielle et logicielle) très tôt et durant tout le cycle de conception, et retarder la séparation des deux parties le plus tard possible.

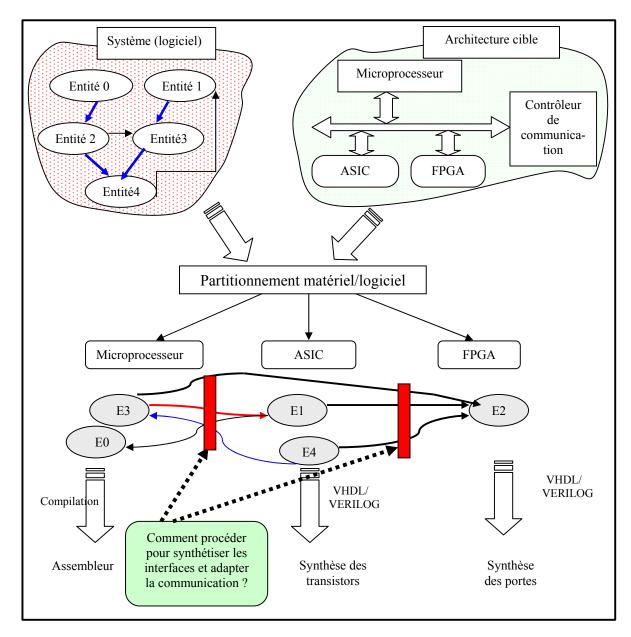

Le processus de conception des systèmes mixtes procède par étapes. Il commence par la spécification et la modélisation du comportement et des fonctionnalités du système, ainsi que son architecture. Ensuite une étape de partitionnement sert à déterminer les parties du système qui doivent être implantées en matériel et celles qui doivent l'être en logiciel. Suit une étape de synthèse de la partie matérielle sous forme de circuit ASIC (Application Specific Integrated Circuit), FPGA (Field Programmable Gate Array), de synthèse de la partie logicielle sous forme

un programme exécutable sur un processeur logiciel, et de synthèse de la communication et des interfaces de communication entre les deux parties (Matérielle et logicielle). La dernière étape est la validation pour garantir que le système conçu réalise de façon correcte les fonctionnalités attendues tout en respectant les contraintes fixées.

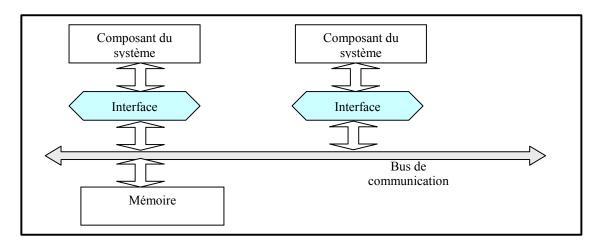

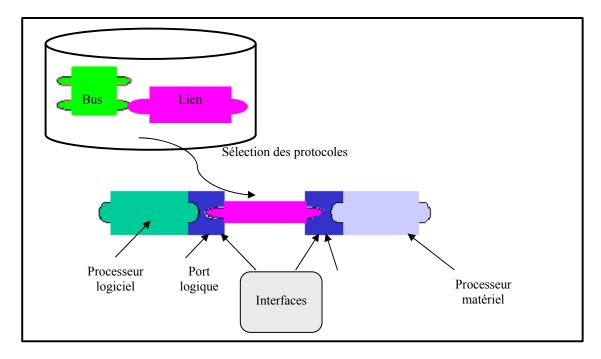

Les différentes parties du système partitionné sont, en général, indépendantes du point de vue traitement, mais il est fréquent qu'elles aient à échanger des informations à travers des mécanismes dédiés à la communication [46]. Ces mécanismes peuvent être en matériel (bus, contrôleurs...etc.) ou en logiciel (pilotes, protocoles...etc.). Pour assurer la communication entre les différentes parties du système, il faut qu'elles parlent le même langage, et utilisent un protocole de communication qui assure l'échange des informations entre elles. Il est donc nécessaire de générer des interfaces qui adaptent la communication entre ces parties.

L'opération de cosynthèse d'interfaces de communication pour le processus de codesign constitue une étape primordiale. Elle consiste à établir des liens de communication entre les composants (matériels et logiciels) du système mixte. Dans les systèmes mixtes, il est possible de distinguer trois types de communication: communication logiciel/logiciel, communication matériel/matériel, communication logiciel/matériel. Le premier et le deuxième type de communication posent moins de problèmes puisqu'ils nécessitent un mécanisme simple pour la communication. Par contre, le dernier type pose plus de problèmes en raison de l'hétérogénéité des composants utilisés pour les deux parties, la nature des traitements, les différences de vitesses, etc. Un autre problème posé par l'étape de cosynthèse d'interface est dû au fait que certains détails de l'interface ne sont connus qu'à l'issue de l'étape de partitionnement (les goulots d'étranglement ne peuvent être identifiés que lors d'une cosimulation), et donc un feedback est nécessaire, ce qu'il complique la cosynthèse. Les concepteurs sont confrontés à la difficulté que constitue la tâche de synthèse d'interfaces et mettent l'accent sur la nécessité de disposer d'outils automatiques permettant d'aider le concepteur dans sa tâche.

Le travail introduit dans ce mémoire, présente une nouvelle approche de cosynthèse d'interfaces de communication pour le codesign. Notre objectif est le développement d'une approche automatique de haut niveau pour la cosynthèse d'interface de communication. L'approche de cosynthèse développée est basée sur la notion de ports virtuels et de primitives virtuelles de communication (*Send*, *Receive*). Elle procède en remplaçant les appels aux

méthodes et leurs paramètres par des appels aux primitives virtuelles (pour les méthodes) et des ports virtuels (pour les paramètres). Elle procède ensuite par affinements successifs sur le code Java de la cospécification des entités de l'application (après une modification dans le code initial). Il est nécessaire de prendre en charge la quantité importante d'informations hétérogènes manipulées tout au long du processus de cosynthèse. Cette approche est basée sur un modèle et un formalisme de cospécification orienté objet. La partie système est décrite en langage Java, et la partie de l'architecture cible est décrite d'une manière graphique à l'aide de composants et de protocoles stockés dans des bibliothèques.

Notre approche permet de rendre l'opération de la synthèse indépendante vis-à-vis de l'architecture cible et des protocoles de communication et ceci grâce à l'utilisation de la notion de bibliothèques de composants architecturaux et de protocoles.

Notre contribution dans ce travail consiste à :

- Développer et réaliser une technique et un environnement permettant d'analyser le code de la cospécification orienté objet (Java), afin d'extraire toutes les informations qui caractérisent la communication entre objets. Ces informations sont représentées à la fin de l'opération de l'analyse par deux graphe : graphe hiérarchique (des classes) qui représente la hiérarchie des classes de la cospécification; et graphe d'instance (fonctionnel) : qui représente les liens de communication entre objets.

- Développer et réaliser une technique et un environnement qui permet la description des composants architecturaux et des protocoles de communication. Nous avons fait le choix d'offrir aux concepteurs la possibilité de composer ses architectures cibles en même temps que l'application qui s'exécute dessus. L'outil développé est basé sur des bibliothèques de composants architecturaux et de protocoles de communication réutilisables.

- Développer une nouvelle approche de cosynthèse des interfaces de communication pour le processus de codesign, qui est basée sur les informations fournies par les deux outils d'analyse et de description des composants architecturaux.

Notre mémoire est structuré en deux parties: la première constitue une étude bibliographique sur la cosynthèse d'interface de communication. Elle comporte quatre chapitres.

Le premier chapitre présente des généralités sur le processus de conception des systèmes mixte (codesign), motivation, avantages et domaine d'application, etc.

Le deuxième chapitre détaille les différentes étapes de processus de codesign afin de situer notre travail.

Le troisième chapitre est consacré aux différents problèmes liés à la cosynthèse d'interfaces de communication.

Le quatrième chapitre présente un état de l'art sur la cosynthèse d'interfaces de communication. Il présente certaines des principales approches citées dans la littérature.

La deuxième partie présente l'approche proposée pour la cosynthèse d'interfaces, elle comporte cinq chapitres.

Le cinquième chapitre présente le schéma général de notre approche, le modèle et le formalisme de cospécification utilisés.

Le sixième chapitre présente l'environnement développé pour l'analyse du code de la cospécification.

Le septième chapitre illustre l'outil développé pour la description de l'architecture cible et des protocoles de communication.

Le huitième chapitre détaille les différentes étapes de l'approche proposée concernant la synthèse d'interfaces.

Le neuvième chapitre présente un jeu de test et la mise en œuvre de l'approche.

#### CHAPITRE 1 CODESIGN MATERIEL/LOGICIEL

#### 1.1 Introduction

Un système mixte est souvent formé de deux parties: une partie matérielle est une autre logicielle en étroite interaction. Si la conception du système est totalement en matériel, elle peut alors présente l'inconvénient du manque de flexibilité, du temps développement important, du coût élevé et du faible taux de réutilisation des composants. Par contre, la réalisation du système en logiciel qui est basé sur l'utilisation des processeurs à usage général, permet d'augmenter la flexibilité, mais présente l'inconvénient d'être lente.

Afin de concevoir ces systèmes embarqués (intégrés dans l'environnement qu'ils contrôlent), l'utilisation conjointe de processeurs d'usage général, dont les performances atteignent aujourd'hui des niveaux très élevés [9], et de circuits spécialisés chargés de la réalisation des fonctions très spécifiques (opérateurs particuliers de traitement de signaux, des interfaces rapides ou analogiques, des protocoles complexes, ...etc.), il est nécessaire de développer des méthodologies de conception nouvelles permettant la mise en oeuvre du système mixte matériel/logiciel.

Avant l'apparition du codesign, les techniques utilisées pour la conception des systèmes (mixtes) contenant du matériel et du logiciel consistaient à séparer la partie matérielle de la partie logicielle très tôt dans le cycle de conception (indépendance de deux partie jusqu'à la phase d'intégration). Les concepteurs du matériel n'avaient donc que peu de connaissances sur la partie logicielle. Il en était de même pour les concepteurs du logiciel. Souvent, de nombreux problèmes étaient rencontrés à la phase d'intégration [46].

La tendance actuelle pour la conception des systèmes mixtes matériels/logiciels consiste à prendre en considération l'interaction entre les deux parties matérielle et logicielle très tôt et durant tout le cycle de développement, et retarder la séparation des deux parties le plus tard possible. Cette approche est appelée conception conjointe Matérielle/logicielle ou Codesign.

#### 1.2 Technique classique de conception des systèmes embarqués

#### 1.2.1 Définition d'un système embarqué

Un système embarqué est un "système digital qui représente un sous-système dans un système global et qui offre un service spécifique à ce système" [67, 22].

Actuellement, les systèmes embarqués sont de plus en plus présents comme constituants de produits industriels ou commerciaux (dans le four micro-onde, le contrôleur d'injection et d'allumage d'une voiture, le robot industriel, le téléphone cellulaire ou le système de pilotage automatique d'un avion ...etc).

#### 1.2.2 Problèmes de conception d'un système embarqué

Les méthodes de conception traditionnelles proposent aux différentes équipes de développer chaque partie du système séparément et de faire l'intégration de l'ensemble lors de la construction du prototype [34].

D'après [29], le flot classique de conception part d'une spécification souvent informelle du système. Il distingue immédiatement les parties logicielles des parties matérielles. Ces parties sont développées indépendamment l'une de l'autre par des équipes différentes. A la fin, une équipe d'intégration assemble les parties, ce qu'il pose souvent des problèmes d'incompatibilité. Cette intégration donne directement un prototype à tester. En cas d'erreur, il peut être nécessaire de recommencer complètement le flot.

Ce type d'approche peut avoir pour conséquence une augmentation du temps et du coût de conception du système, à cause des problèmes de validation du système entier, et des problèmes d'interfaces entre les différentes parties au moment de la construction du prototype [34]. La première difficulté rencontrée par les concepteurs est la complexité des systèmes actuels (Les systèmes embarqués sont de plus en plus complexes) ils doivent fournir des fonctionnalités de plus en plus élaborées, et peuvent donc être constitués de composants logiciels ou matériels variés.

Les approches classiques de conception reposent généralement sur une décomposition initiale de la spécification en sous-systèmes qui sont chacun optimisés localement et validés

ensuite globalement par co-simulation. Cette approche rend difficile la vérification fonctionnelle et temporelle du système [2].

D'autres problèmes peuvent être rencontrés par les concepteurs des systèmes embarqués:

- Difficulté de corriger les erreurs et de vérifier le système.

- Difficulté de maintenir le système en fonctionnement normal.

- Préserver des délais de mise sur le marché les plus courts possibles (compétitivité).

- La robustesse du système à concevoir.

La modélisation de systèmes réactifs est donc une activité difficile. Elle n'est pas dépourvue de risques d'erreurs par les méthodes usuelles.

Les composants réutilisables permettent d'éviter aux concepteurs d'avoir développer à chaque fois toutes les fonctionnalités requises. Cependant, pour qu'il ait un gain de temps l'intégration de ces composants au reste du système ne doit pas demander trop d'effort aux concepteurs.

Une autre voie pour surmonter la complexité consiste à élever le plus possible le niveau d'abstraction des descriptions des systèmes à concevoir. Cette méthode, peut donner aux concepteurs une vision plus générale et plus simple des systèmes.

Donc il est nécessaire de suivre des méthodologies et des outils plus efficaces permettant la conception conjointe, pour guider le passage des descriptions de haut niveau aux réalisations finales. Il est nécessaire aussi de tendre vers des approches globales de conception et d'optimisation multi-critères pour réduire le fractionnement actuel du processus de conception [2].

#### 1.3 Comparaison entre conception traditionnelle et le codesign matériel/logiciel

Les Méthodes de conception classiques ou traditionnelles des systèmes imposent du séparer le matériel du logiciel très tôt dans le cycle de conception. Les techniques de conception des deux parties du système (Matériel et logiciel) restent indépendantes [46], n'autorisant l'interaction que lors de la phase d'intégration.

Ce type de conception pose souvent quelques problèmes [47]:

- Mauvaise appréciation des besoins en ressources pour les concepteurs matériels.

- Mauvaise exploitation des ressources pour les concepteurs logiciels.

- Modifications majeures matérielles et/ou logicielles à la phase d'intégration.

La conception conjointe ou concurrente, encore nommée "codesign matériel/logiciel", est donc née de la nécessité de développer des applications respectant des exigences de plus en plus grandes en performances, coût, délais ou testabilité [46]. Il est nécessaire, dès les premières étapes de la conception, de tenir compte des interactions entre le matériel et le logiciel.

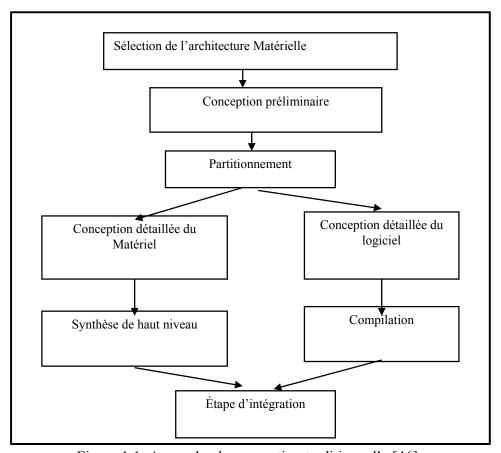

Les figures (1.1 et 1.2) illustrent les approches de conception traditionnelle et conjointe pour les systèmes mixtes.

Figure 1.1: Approche de conception traditionnelle [46]

Figure 1.2: Approche de conception conjointe [46]

L'inconvénient des méthodes traditionnelles de codesign est leur trop grande spécialisation: une méthode est faite pour un type de problème [38].

Le développement conjoint du logiciel et du matériel est un domaine relativement récent. Pour maîtriser la complexité croissante des systèmes et pour répondre aux critères de performances attendus, il est important d'aborder la conception des systèmes mixtes en terme de conception conjointe de matériel/logiciel [31, 7]. Ce type d'approche agit aussi au plus haut niveau d'abstraction, c'est à dire le niveau système. Le besoin d'un niveau d'abstraction plus élevé, notamment le niveau système, vient du fait que les systèmes deviennent de plus en plus complexes [34].

Les buts de codesign sont multiples puisqu'il permet de:

- Trouver le meilleur compromis entre la réalisation logicielle et réalisation matérielle.

- Augmenter la productivité en permettant la conception simultanée du logiciel et du matériel (concurrent design).

#### 1.4 Quelques définitions pour le codesign

D'après différents chercheurs qui travaillent dans le domaine de la conception des systèmes mixtes, on peut citer plusieurs définitions:

- D'après Stoy [67], le but du codesign est d'intégrer la conception du matériel et du logiciel pour former un processus unique de conception. Seul le comportement de tout le système intéresse l'utilisateur. Le codesign permet de trouver des moyens d'améliorer les techniques de conception des systèmes où le matériel et le logiciel travaillent en étroite collaboration pour résoudre des problèmes qui ont le plus souvent des contraintes imposées sur leurs solutions.

- Selon Kalavade [43], la tâche de codesign consiste à produire un système matériel/logiciel optimal, qui répond aux spécifications données, en respectant les contraintes de conception (contraintes temps-réel, de performance, de vitesse, de surface, de taille du code, d'espace mémoire, et de consommation). La doctrine clé dans le codesign est d'éviter la séparation entre le matériel et le logiciel conçus trop tôt.

- D'après Edwards [24], le but principal du codesign est de produire des systèmes contenant un équilibre optimal entre les composants matériels et logiciels qui travaillent conjointement pour réaliser un comportement spécifié et répondre à des contraintes identifiées y compris satisfaire des objectifs de performance critiques.

- De Micheli [22] affirme que le codesign matériel/logiciel signifie répondre aux objectifs au niveau système en exploitant la synergie du matériel et du logiciel à travers la conception conjointe.

- D'après [46] le codesign matériel/logiciel est une Méthodologie unique de conception intégrant différents composants d'un système mixte en respectant les fonctionnalités et les contraintes associées.

- Selon [69], la conception concurrente matérielle/logicielle est une approche qui intègre dans un même environnement la conception du matériel et celle du logiciel.

- Pour [29] le codesign a pour but de développer conjointement les diverses parties d'un système hétérogène (logiciel, électronique, mécanique, etc.). C'est pourquoi une description globale du système est nécessaire.

- D'après [42], Le codesign est l'une des techniques les plus intéressantes car elle s'efforce de mettre en place une vraie méthode de conception simultanée du matériel et du logiciel. Son

émergence est due à la grande et croissante ressemblance de la conception des systèmes numériques avec la conception du logiciel.

Nous pouvons donc conclure, que le codesign est une approche qui permet d'intégrer dans une méthode de conception unique les différentes composants d'un système mixte (composants matériels, composants logiciels, ou composants des communications) et qu'elle prend en compte principalement l'interaction entre ses composants, afin d'obtenir des produits respectant les fonctionnalités désirées et respectant les différentes types de contraintes.

#### 1.5 Pourquoi le codesign Matériel/logiciel?

La nécessité d'une nouvelle méthodologie de conception vient essentiellement de la progression que connaît de nos jours le domaine de la conception des circuits intégrés à très grande échelle (plusieurs Millions de transistors sur une même puce). Selon Buchenrieder [10], le codesign progresse dans l'industrie en partie parce que, respecter les conditions du développement de systèmes de complexité croissante sous des contraintes de temps de mise sur le marché rigides nécessite une nouvelle approche.

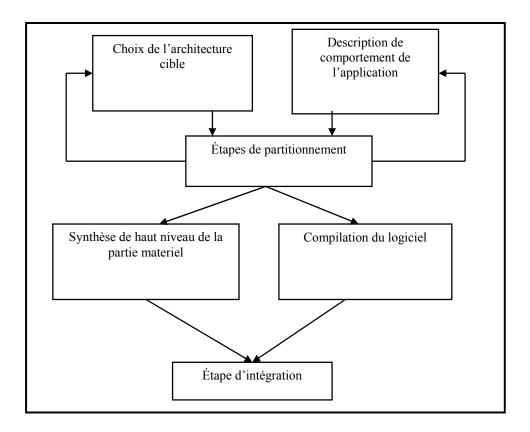

Figure 1.3: Croissance de la production des produits électroniques (systèmes embarqués) [1]

#### 1.6 Intérêts du codesign

Parmi les intérêts du codesign, citons:

- Exploration efficace de l'espace de conception: Le concepteur doit explorer toutes les options possibles, outils et architectures (manuellement ou par l'utilisation d'outils automatique). Le codesign facilite l'exploration des compromis à travers les frontières de manière dynamique au fur et à mesure que le processus de conception progresse, il permet d'explorer un plus grand nombre de solutions.

- <u>Flexibilité de la conception</u>: La flexibilité de la conception des systèmes mixtes consiste en des modifications qui peuvent survenir durant le processus de conception, à cause des changements d'objectifs, ou d'une amélioration apportée. Pour ce faire, il est important de pouvoir effectuer des réajustements sans avoir à refaire tout le travail effectué.

- Réduction des délais de mise sur le marché: À cause des problèmes de validation du système entier et des problèmes d'interfaces entre les différentes parties au moment de la conception des systèmes [34], le temps et le coût de conception augmentent. Le fait d'adopter une méthodologie de conception unique et automatisée de toutes les parties du système mixte, permet d'accélérer le processus de conception, et de concevoir d'autres composants plus rapidement.

- <u>Conceptions à moindre coût</u>: La conception concurrente des deux parties (matériel/logiciel) du système à concevoir permet d'explorer efficacement un plus grand nombre de solutions en réduisant les délais de conception. Elle permet donc de fournir rapidement un bon compromis performance/coût et d'aboutir à des solutions plus intéressantes en coût et en performances

En plus de ces intérêts, le codesign facilite la réutilisation des composants matériels et des composants logiciels et il fournit un environnement intégré pour la synthèse et la validation des composants matériels et logiciels.

#### 1.7 Domaines d'application du Codesign

Durant ces dernières années, de plus en plus d'exemples de codesign matériel/logiciel ont été publiés, et parmi les classes de systèmes concernés par le codesign, citons [14]:

- <u>Les systèmes de communication:</u> cette classe englobe les systèmes qui reçoivent, transforment, et émettent des flots de messages. C'est l'un des domaines les plus actifs du codesign, car il nécessite la production à faible coût de systèmes à contraintes strictes dans un environnement de grande concurrence.

- <u>Les systèmes de traitement de signaux</u>: cette classe concerne les systèmes de traitement et toutes formes de signaux digitaux. Le développement de systèmes utilisant des processeurs de traitement de signaux digitaux constitue une application directe des processeurs à jeu d'instruction et des processeurs dédiés.

- Les systèmes de contrôle/commande: regroupent les système qui sont en interaction avec leur environnement, composés essentiellement d'actionneurs qu'il contrôlent en fonction d'évènement perçus par des capteurs.

#### 1.8 Architectures cible utilisées pour le codesign

Une architecture mixte logicielle/matérielle combine à la fois des composants logiciels et des composants matériels. Le but de la conception d'architecture est de décrire pour un système donné le nombre de composants, le type de chaque composant, et le type de connexion entre ces divers composants. Les composants sont les éléments de base pour réaliser une application donnée. Trois types de composants peuvent être distingués: les composants logiciels, les composants matériels et les composants de communication.

Dans la conception conjointe logicielle/matérielle, il y a une grande variété d'architectures cibles. L'utilisation d'une architecture spécifique, bien adaptée à une application déterminée, est plus efficace. Cependant, ce type d'architecture n'est pas assez flexible pour bien s'adapter dans un environnement de codesign à d'autres types d'application [69].

#### 1.8.1 Organisation de l'architecture

L'organisation de l'architecture cible est définie par la composition ou l'assemblage d'éléments de base. Deux types d'organisation peuvent être distinguée [69]:

• <u>L'architecture monoprocesseur:</u> qui est composée d'un processeur et d'un ensemble de composants matériels spécifiques. Dans cette architecture, un seul processeur a la

responsabilité de l'état global du système.

• <u>L'architecture multiprocesseur:</u> dans ce type d'organisation, l'architecture est composée d'un réseau de processeurs autonomes communicants. Les processeurs agissent de manière indépendante. L'interaction entre les différents composants constitue la communication. Cette communication permet l'échange des informations et du contrôle.

#### 1.8.2 Composants de l'architecture

Les systèmes complexes existants comportent plusieurs types de composants. Les composants trouvés dans ce type de système sont les processeurs, les composants matériels (ASICs, FPGAs..), composants logiciels, et composants de communication.

#### 1.8.2.1 Les processeurs

Les travaux de [69] présentent une classification des processeurs: processeurs d'usage universel, processeurs parallèles et processeurs spécifiques.

#### 1.8.2.1.1 Les processeurs d'usage universel

Ce sont des processeurs classiques à jeu d'instructions comme les processeurs RISC (Reduced-Instruction Set Computer) ou CISC (Complex Instruction Set Computer). Ils sont optimisés pour réaliser des cycles d'horloge courts, un nombre restreint de cycles par instruction, et une parallélisation efficace du flot d'instruction (pipelining).

#### 1.8.2.1.2 L'architecture à processeurs parallèles

Regroupe les machines VLIW (Very Large Instruction Word), SIMD (Single Instruction stream Multilple Data stream) ou MIMD (Multilple Instruction stream Multilple Data stream) exploitant le parallélisme en utilisant de multiples unités fonctionnelles dans leur chemin de données.

#### 1.8.2.1.3 Le processeur programmable spécifique

Appelé aussi ASIP (Application-Specific Instruction-set Processor), les applications qui y sont adaptées varient du simple algorithme à un vaste domaine comme celui du traitement du signal. Il est réutilisable avec son logiciel pour la conception de systèmes complexes. Cette réutilisation permet la diminution de temps de conception et le coût des systèmes.

#### 1.8.2.1.4 Les ASICs (Application-Specific Integrated Circuit)

Les ASICs offrent les garanties d'offrir une basse consommation et les meilleures performances. Par contre, la flexibilité, le temps de développement et les possibilités de réutilisation sont ses points faibles. Les concepteurs utilisent plus les ASICs pour les parties d'une application bien maîtrisées qui évoluent peu, laissant le reste pour une implantation en logiciel, et ceci dans un but de flexibilité et de coût. Les circuits ASICs ont fait l'objet de beaucoup d'intérêt pendant la dernière décennie à cause du développement d'outils de synthèse de haut niveau. Ces outils ont été développés pour augmenter la productivité de conception des circuits en réduisant le temps de conception.

#### 1.8.2.1.5 Les FPGAs (Field Programmable Gate Arrays)

Les FPGAs sont souvent utilisés en conjonction avec les composants cités plus haut. Ils fournissent des circuits logiques et numériques avec une complexité moyenne de l'ordre de quelques milliers de portes environ et peuvent être utilisés pour des applications spécifiques dans un seul circuit intégré. La popularité des FPGAs peut s'expliquer par leur facilité d'utilisation et le fait qu'ils soient programmables, tout en offrant des performances intéressantes.

#### 1.9 Conclusion

En raison de la grande variété de réalisation des traitements, leur hétérogénéité, et les différentes contraintes de conception (temps, surface, consommation, temps de mise sur le marché, flexibilité, coût...etc.), le processus de conception des systèmes mixtes est devenu de plus en plus complexe.

Le codesign matériel/logiciel des systèmes mixtes est une méthodologie unique capable d'intégrer différents composants, en respectant un certain nombre de contraintes. Cette technique de conception prend une importance de plus en plus grande, étant donné la complexité des applications à traiter et surtout des possibilités très grandes offertes par les technologies pour la réalisation de circuits mixtes [9]. Un certain nombre de techniques et d'outils basés sur la conception de systèmes sur puce commencent à apparaître dans l'industrie, mais les années à venir devraient voir une explosion du domaine [9].

Les objectifs de ce chapitre étaient de définir le vocabulaire que nous utiliserons dans le processus de codesign, et de présenter la méthodologie de ce processus de conception, ses intérêts, ses domaines d'application et l'organisation des architectures cibles. Le chapitre suivant est consacré aux étapes de ce processus.

# CHAPITRE 2 DIFFERENTES ETAPES DE PROCESSUS DU CODESIGN

#### 2.1 Introduction

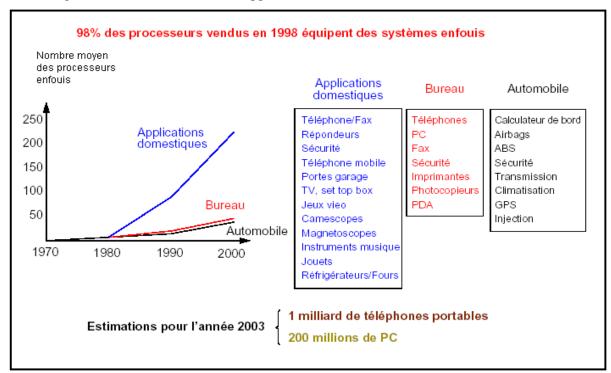

Le processus de conception des systèmes mixtes codesign suit généralement les étapes illustrées en figure 2.1. Il commence par une étape de spécification conjointe décrivant le système à concevoir [46]. Il est possible de distinguer deux types de spécifications:

- La spécification fonctionnelle qui permet de décrire le comportement attendu de l'application [37].

- La spécification des contraintes externes que le système devra supporter (consommation, contraintes temporelles,...etc).

Une étape de modélisation suite a l'étape de spécification, a pour but de modéliser les entités et les composants architecturaux du système. Elle est suivie d'une étape de partitionnement qui a pour but de répartir les entités de l'application en trois parties: une partie logicielle, une partie matérielle, et des interfaces de communication permettant la communication entre les deux parties précédentes.

Avant de passer à l'étape suivante (cosynthèse), le système partitionné doit être vérifié (fonctionnement, contraintes de temps, espace mémoire occupé, coût...).

L'étape suivante consiste à déterminer les composants à utiliser pour mettre en œuvre la partie matérielle et pour synthétiser le logiciel, en tenant compte de la communication et de la synchronisation entre les différentes composantes du système.

Figure 2.1: Les différentes étapes du processus de codesign [46]

#### 2.2 Etapes de processus de codesign

Dans ce qui suit, nous revenons plus en détail sur ces différentes étapes.

#### 2.2.1La cospécification

Cette étape consiste généralement à décrire les fonctionnalités du système à concevoir et les contraintes qu'il doit respecter [46]. Vu que les systèmes mixtes deviennent de plus en plus complexes, de plus en plus hétérogènes, cela implique la nécessité d'élever le niveau d'abstraction (niveau système). Les spécifications au niveau système sont typiquement conçues comme des ensembles de modules communicants [34]. Chaque module réalise une fonctionnalité spécifique. Les modules peuvent communiquer de manière synchrone ou asynchrone et peuvent être orientés contrôle ou donnée. De plus, ils peuvent avoir des contraintes temps réel très rigoureuses. Cette grande variété de caractéristiques pose le problème de choix du langage à

utiliser pour la spécification de tels systèmes, car aucun langage de spécification ne s'est imposé pour décrire toutes les parties du système de manière efficace.

#### 2.2.1.1 Méthodes pour la spécification des systèmes complexes

Il n'existe pas de technique ou règle précise pour déterminer le type de langage ni le nombre de langages nécessaires à la spécification d'un tel système [34]. Selon le choix du concepteur, la spécification de la fonctionnalité d'un système complexe peut être faite à l'aide de l'une des trois méthodes:

- La spécification homogène.

- La spécification hétérogène.

- La spécification multilangage.

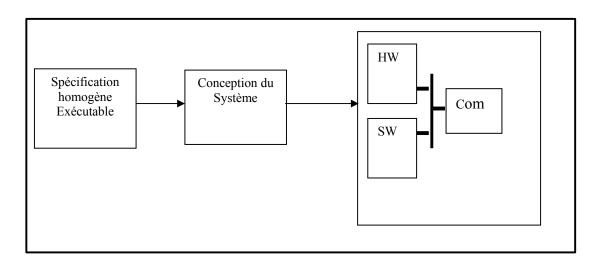

#### 2.2.1.1.1 Spécification homogène

Dans ce type de spécification un seul langage de spécification est utilisé [34]. Le système est spécifié comme un ensemble de fonctions et de contraintes, indépendamment de l'implémentation et du partitionnement matériel/logiciel.

Un environnement générique de codesign basé sur un modèle homogène est schématisé dans la figure 2.2.

Figure 2. 2: Flot de conception pour une spécification homogène [34].

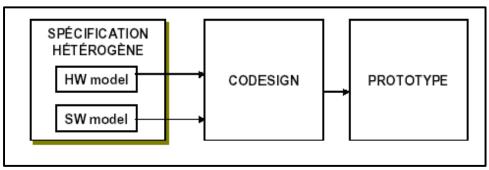

#### 2.2.1.1.2 Spécification hétérogène

Dans les spécifications hétérogènes, des langages spécifiques sont utilisés pour les parties matérielles et logicielles. Un environnement générique de conception conjointe basé sur un modèle hétérogène est présenté en figure 2.3.

Figure 2.3: Flot de conception pour une spécification hétérogène [69].

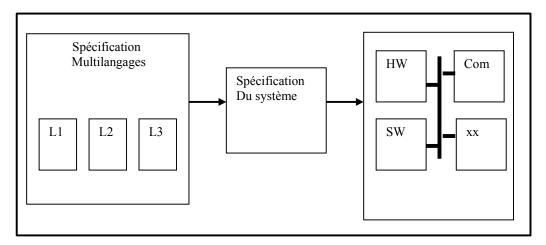

#### 2.2.1.1.3 Spécification multilangage

La spécification multilangage peut être vue comme une généralisation de la description hétérogène d'architectures mixtes logicielles/matérielles [34]. Il s'agit de traiter des systèmes composés des modules hétérogènes. La caractéristique de la méthode de spécification multilangage est l'utilisation de plusieurs langages pour la spécification de la fonctionnalité du système. La figure 2.4 illustre un environnement générique de codesign basé sur un modèle multilangage.

Figure 2.4: Flot de conception pour une spécification multilangage [34].

#### 2.2.1.2 Différentes classes d'approches pour la cospécification

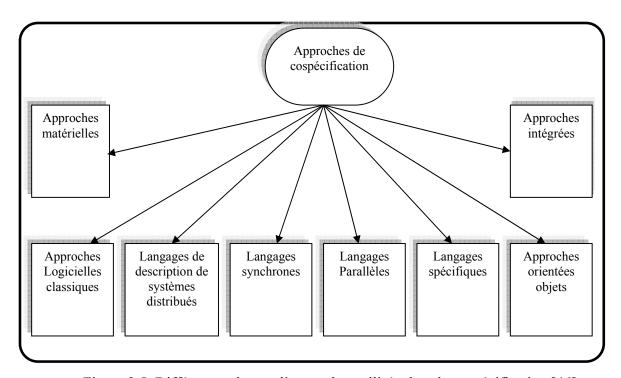

Il existe différentes classes d'approches utilisées pour la cospécification des systèmes mixtes. Certaines approches consistent à maintenir une nette séparation entre la spécification de la partie matérielle et la partie logicielle [46]. Chaque partie du système est spécifiée à l'aide d'un langage correspondant à sa nature (exemple C/C++/java.. pour la partie logiciel, VHDL/VERILOG pour la partie matérielle) [45, 54].

La figure 2.5 présente les différentes classes d'approches prônant l'unification de la spécification.

Figure 2.5: Différentes classes d'approches utilisée dans la cospécification [46].

#### 2.2.1.2.1 Les langages de description du matériel

Plusieurs approches utilisent un langage de description de matériel pour décrire les parties matérielles d'un système en conjonction avec un langage logiciel [20]. VHDL et VERILOG figurent parmi les logiciels de description de matériel les plus utilisés soit directement comme langages de spécification des applications mixtes (matériel/logiciel), soit à l'issue de la dernière étape du codesign afin de permettre l'utilisation d'outils de synthèse commerciaux.

#### 2.2.1.2.2 Les approches de description de logiciels classiques

Dans l'approche de description de logiciels classiques, le système est spécifié en logiciel, en utilisant un langage classique servant habituellement à décrire le logiciel. Les premiers langages utilisés pour la spécification des systèmes mixtes sont les langages d'assemblage. Etant donné le manque de souplesse et la relative pauvreté d'expression de ces langages [46], ils sont actuellement désertés au profit de langages de plus haut niveau (C, C++, Java...).

## 2.2.1.2.3 Autres formalismes de spécification

Il existe d'autres classes d'approches et d'autres langages de spécification des systèmes mixtes. Parmi ces approches, citons:

- Les automates à états finis étendus (EFSM: Extended Finite State Machines).

- Les machines à états finis dédiées au codesign (CFSM: Codesign Finite State Machines).

- Les modèles à diagrammes d'états (StateChart).

- Les CSPs (Communicating Sequential Process) sont largement utilisés pour spécifier les circuits asynchrones [35].

- Tangram et Balsa sont deux langages de spécification utilisant une représentation intermédiaire à base de composants qui implémentent le protocole hand-shake[11].

- Les langages de description des systèmes distribués tels que SDL (Specification and Description Language).

- Le langage synchrone SIGNAL est utilisé pour le développement d'applications embarquées et temps réel.

#### 2.2.1.3 Les aspects que doit posséder un formalisme de cospécification

Un formalisme de cospécification doit garantir les aspects suivants.

- Le formalisme de cospécification permet l'expression des contraintes de temps.

- Il doit assurer la concurrence [21], Cette dernière est caractérisée par le grain du parallélisme. Celle-ci peut être au niveau de l'instruction (opérations parallèles) ou au niveau du processus.

- La hiérarchie qui permet de décomposer un système en sous-systèmes afin de mieux gérer sa complexité.

- La synchronisation qui permet la coordination des différents comportements et de la communication [21].

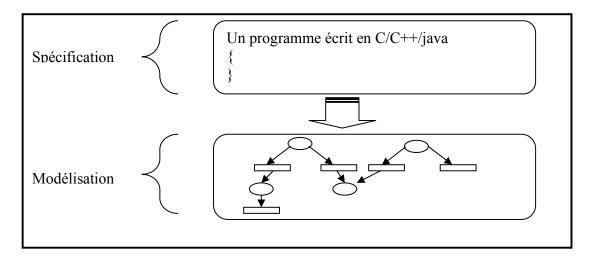

# 2.2.2La modélisation

Cette étape consiste à remplacer le système physique mixte qu'on veut concevoir par une représentation symbolique ou modèle [46]. Un modèle peut être défini comme étant une abstraction de ce qui existe dans le monde réel. Il peut être mathématique ou constructif.

En codesign, le choix d'un modèle interne pour un outil de conception assistée par ordinateur dépend fortement du type de système à concevoir.

#### 2.2.2.1 Exemple de modèle

Figure 2.6: Création d'un modèle interne (ex: réseaux de Petri).

# 2.2.2.2 Objectifs d'un modèle

Parmi les objectifs d'un modèle dans le codesign, citons:

• Permettre au concepteur de capturer les fonctionnalités et les contraintes du système à concevoir.

- Il doit être synthétisable (c'est-à-dire permettre le passage automatique à la phase de synthèse).

- Permettre la vérification et/ou simulation.

# 2.2.2.3 Quelques modèles utilisés en codesign

Nous présentons ici quelques modèles utilisés pour le processus de codesign. L'objectif n'est pas de détailler chaque modèle, mais juste de citer et de donner des exemples de modèles les plus utilisés dans le codesign.

- Les automates à états finis (FSM): ils constituent un des modèles les plus utilisés pour le flot de contrôle dans les systèmes synchrones.

- Les graphes de flot de données (DFD): ils sont utilisés pour modéliser les applications de traitement de signaux digitaux.

- Les réseaux de petri: ils sont utilisés pour modéliser les systèmes mixtes [65, 66].

- Les approches orientés objets [46].

- L'approche orientée acteurs [50].

- UML (Unified modeling language).

Le choix du modèle dépend fortement du système à concevoir. Il est guidé par l'ensemble des contraintes et des caractéristiques de l'application. Un modèle choisi doit tenir compte de toutes les étapes du processus de codesign: le partitionnement, la synthèse de la communication et des interfaces, la covérification/covalidation. Les travaux de [40, 20, 69, 34] modélisent une unité de communication comme étant un objet fournissant un ensemble de primitives de communication (méthodes) réalisant un protocole spécifique.

La tendance actuelle dans de nombreuses équipes de recherche est à l'unification, pour aboutir à un modèle de calcul concurrent unique [46]. Ceci pourrait être accompli en réalisant un mélange d'un certain nombre de modèles, mais un tel modèle serait extrêmement complexe et difficile à utiliser, et les outils de synthèse et de simulation seraient difficiles à concevoir [48].

#### 2.2.3 Le partitionnement

L'étape de partitionnement constitue le processus qui détermine les parties du système qui doivent être implantées en matériel et celles qui doivent l'être en logiciel. En général, les

partitions qui se trouvent sur le chemin critique de l'application et qui demandent un temps de réponse court sont réalisées en matériel. Les autres partitions sont réalisées en logiciel [20] afin d'offrir plus de souplesse si des changements doivent être apportés. Le partitionnement et l'ordonnancement sont deux étapes en étroite interaction. Ce sont des problèmes NP-difficiles.

#### 2.2.3.1 La granularité du partitionnement

La granularité consiste à déterminer comment découper les entités du système à concevoir dans le but d'affecter ces fragments de code aux différents processeurs matériels et logiciels de l'architecture cible. Le niveau de granularité (degré de granularité) est le niveau de finesse adopté pour les différentes parties de l'application [46]. Dans la littérature, nous pouvons distinguer trois principaux niveaux de granularité:

- Le gros grain (niveau système).

- Le grain moyen (c'est le niveau tâche, processus, fonction...).

- Le grain fin (instruction simple, opération arithmétique).

#### 2.2.3.2 Le choix de l'architecture cible

Le choix de l'architecture cible consiste à déterminer le nombre et le type de processeurs que le système doit contenir [37], le nombre et le type de coprocesseurs implémentant les parties matérielles ainsi que l'organisation et le choix des média de communications. Plusieurs types d'architectures cibles sont utilisés dans les différents travaux sur le codesign, par exemple: un composant unique, une carte dédiée, une carte autonome embarquée, etc.

Nous pouvons distinguer deux approches pour la classification des architectures cibles:

- La première approche consiste à fixer l'architecture avant de procéder au partitionnement de l'application;

- La seconde classe consiste à déduire l'architecture cible qui résulte de l'étape de partitionnement [46].

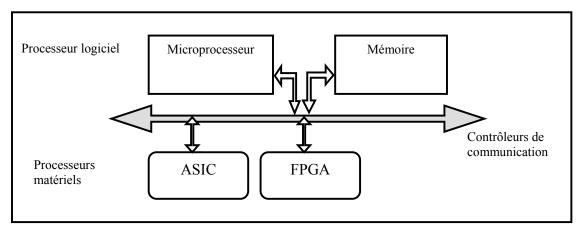

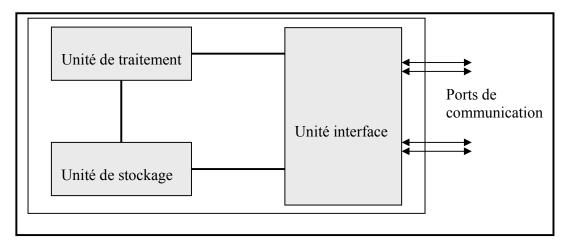

La figure 2.7 illustre la structure générale (schéma générique) d'une architecture cible.

Figure 2.7: Schéma générique d'une architecture cible.

#### 2.2.3.3 Les méthodes de partitionnement

L'étape du partitionnement est effectuée, soit d'une manière automatique, soit d'une manière interactive. Il est possible de distinguer deux méthodes de partitionnement:

#### 2.2.3.3.1 Le Partitionnement interactif

Une technique de partitionnement interactif permet aux concepteurs de balayer manuellement ou d'une manière semi-automatique plusieurs alternatives de partitionnement du système. Cette technique prend en considération l'expérience et le bon sens des concepteurs.

#### 2.2.3.3.2 Le Partitionnement automatique

L'approche de partitionnement interactif est intéressante quand la taille du système mixte est de petite taille. Lorsque la taille et la complexité du système augmentent, le partitionnement devient de plus en plus difficile à gérer manuellement. Dans ce dernier cas, spécialement lorsque le grain de partitionnement est fin, la majorité des chercheurs s'accorde à penser que le partitionnement automatique est la seule solution viable.

#### 2.2.3.4 Contraintes guidant le partitionnement

Plusieurs paramètres influent sur le processus de partitionnement, citons par exemple, parmi les plus utilisés: les contraintes de temps, l'espace mémoire, la communication et la dissipation en puissance.

#### 2.2.3.5 La fonction de coût

L'utilisation d'une fonction de coût permet de comparer les solutions possibles du partitionnement, et d'affecter un coût à chacune. L'algorithme de partitionnement consiste alors à déterminer la solution présentant le coût le minimum (maximum).

Dans les travaux d'Edwards [24], la fonction de coût inclut une combinaison du temps, de l'espace, du coût des composants, de la communication et de la consommation en puissance, où l'importance relative dépend fortement du type d'application. Henkel et Ernst [33], utilisent une fonction de coût qui prend en compte la surface et le temps d'exécution et qui permet de respecter une contrainte temps-réel et de minimiser la quantité de matériel en même temps.

# 2.2.3.6 Les approches de partitionnement

Dans la littérature, un certain nombre d'approches sont utilisées pour résoudre le problème de partitionnement. Il est possible de les regrouper en fonction de plusieurs facteurs: le degré de granularité, partitionnement manuel ou automatique, partitionnement binaire ou étendu.

Parmi les approches existantes, citons l'approche exacte. Son principe consiste à explorer de manière exhaustive toutes les solutions possibles. Elle a comme avantage d'offrir la certitude de trouver la meilleure solution. Cependant, elle présente un coût élevé en temps, spécialement lorsque le système est complexe.

Une autre approche est basée sur des techniques heuristiques inspirées de la recherche opérationnelle (recuit simulé, algorithmes génétiques...etc).

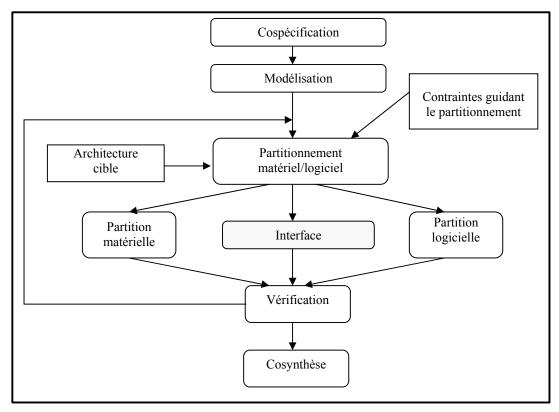

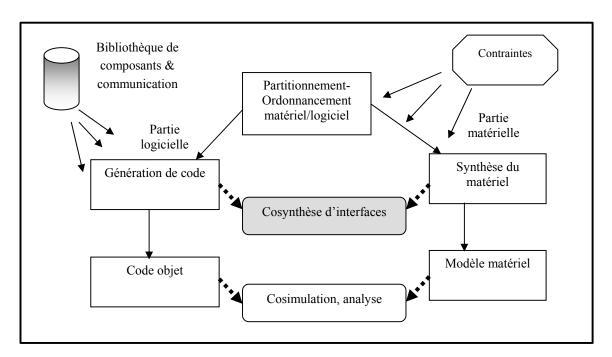

#### 2.2.4 La cosynthèse d'interfaces de communication

Le partitionnement a pour but de , décomposer le système en trois parties:

- Une partie matérielle implantée sous forme de circuits (FPGA, ASIC,...).

- Une partie logicielle mise en œuvre sous forme d'un programme exécutable sur un processeur à usage général.

- Une interface de communication sert à réaliser l'échange de données entre les deux parties.

Les partitions obtenues doivent échanger des informations à travers des mécanismes de communication. Ces mécanismes peuvent être matériels (bus, arbitre,...etc.), ou logiciels (protocoles, pilotes, ...etc.). La synthèse des communications dans les systèmes mixtes consiste à réaliser physiquement les canaux permettant les échanges de données entre les tâches affectées aux différents processeurs [37]. La cosynthèse d'interface de communication peut être définie comme le processus de réalisation des liens de communication entre les processus qui échangent des messages dans une architecture mixte [46].

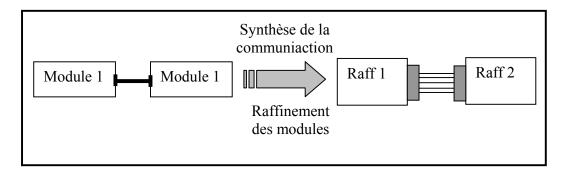

Autrement dit, La synthèse des interfaces peut être vue comme le processus d'affinement des mécanismes de communication en partant d'un modèle abstrait jusqu'à un modèle plus détaillé de plus bas niveau d'abstraction. L'affinement prend en considération toutes les contraintes, que ce soit celles formulées par l'utilisateur ou celles émanant des règles de conception [4]. La figure 2.8 illustre le principe de cosynthèse.

Figure 2. 8: Principe du flot de cosynthèse

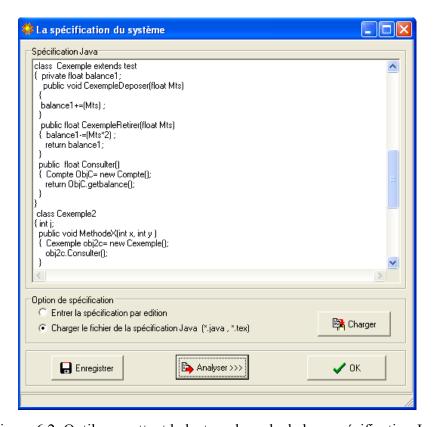

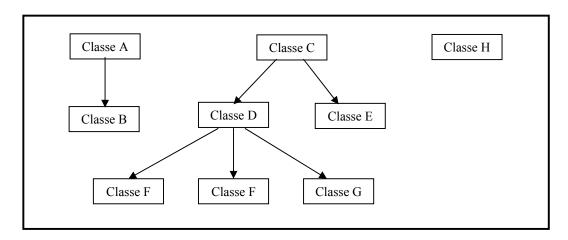

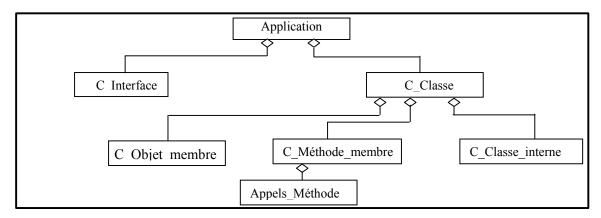

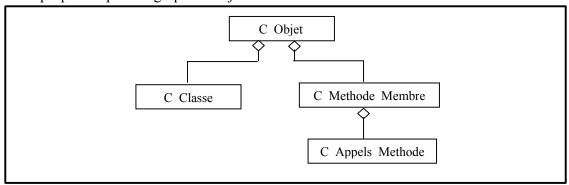

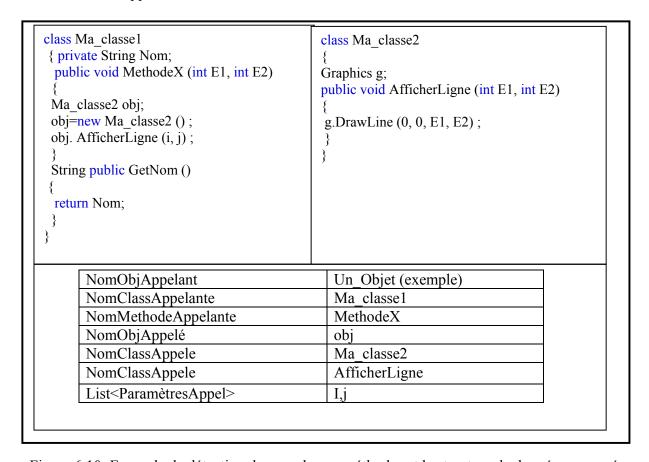

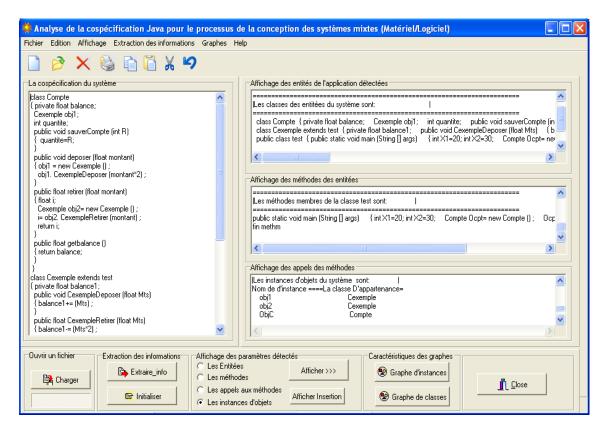

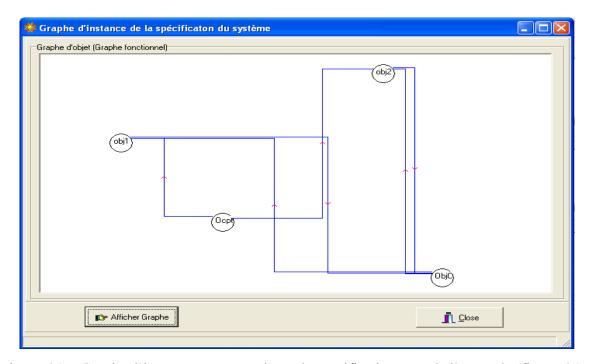

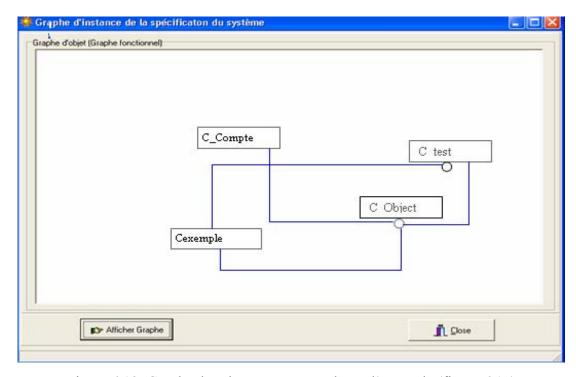

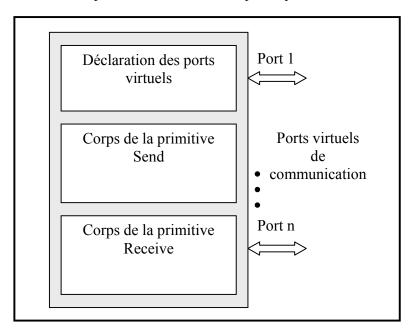

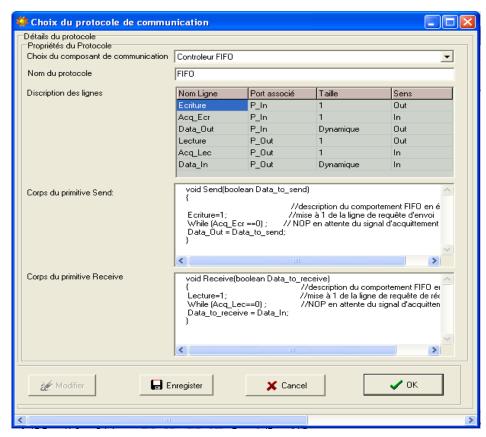

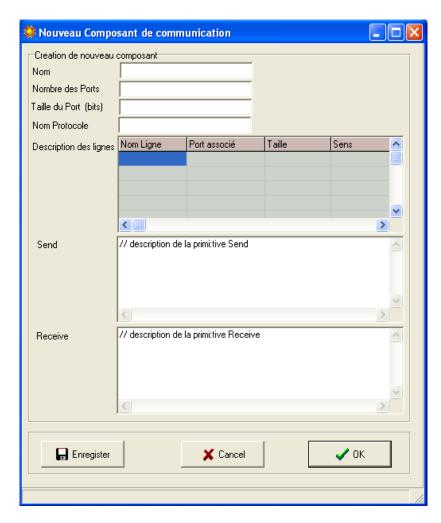

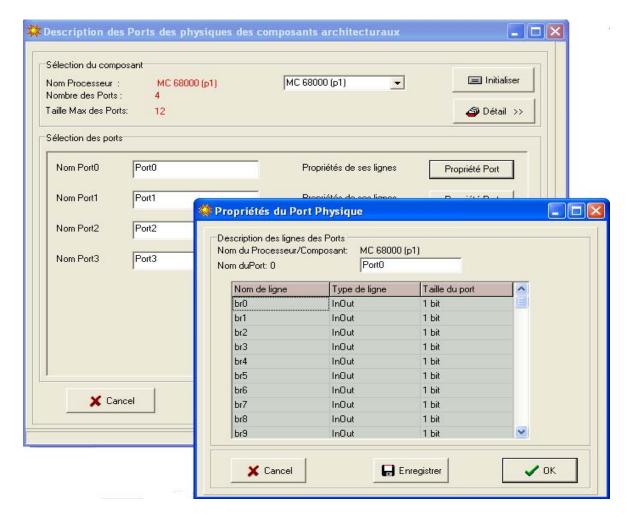

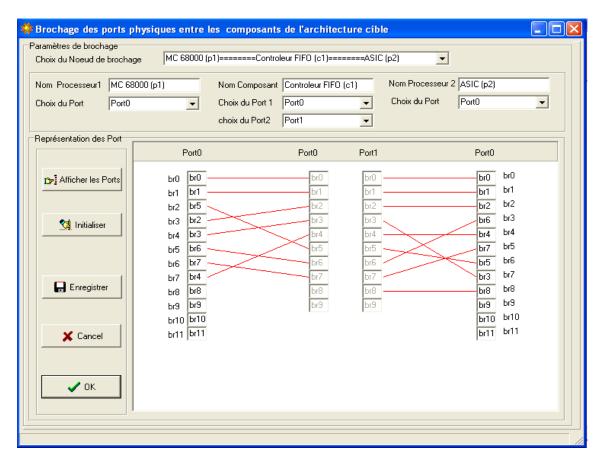

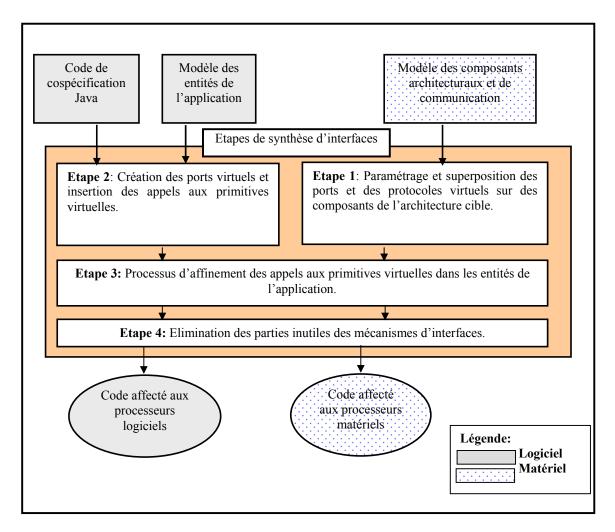

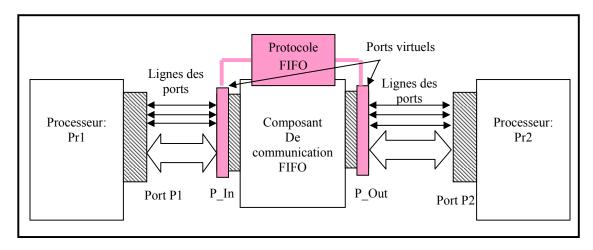

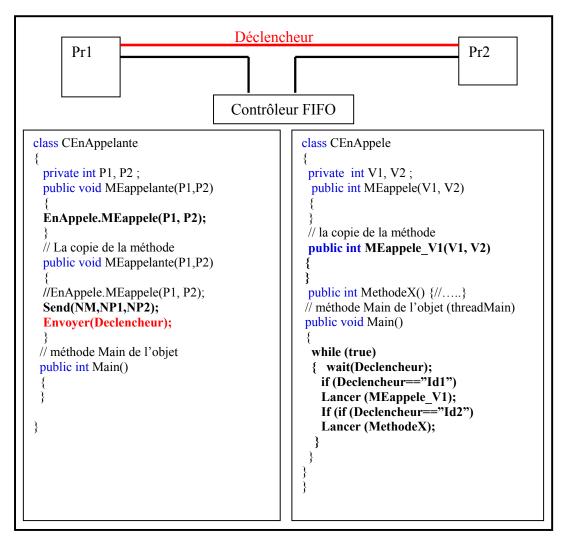

# 2.2.5 La covalidation/covérification