République Algérienne Démocratique et Populaire Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Université Saad Dahlab, Blida USDB

Faculté des Sciences Département Informatique

Mémoire pour l'Obtention

Du Diplôme de Master en Informatique

Option: Ingénierie du Logiciel

Sujet:

Réalisation d'une Plateforme HW/SW sur FPGA Dédiée au Contrôle Embarqué

Présenté par: Med Lamine Berrandjia **Promoteurs:**

- Mr Abdelkrim Kamel Oudjida

- Mme Nadjia Benblidia

Soutem devet the just . 413 FD HA FIDA: President Argay makating: Esconsimited Burghana Maamen: Examinates

Organisme d'accueil : Centre de Développement des Technologies Avancées

- 2010/2011-

JA-004-75-1

Gloire à Dieu

A mes chers Parents

A ma famille

### Remerciements

Je tiens à remercier la direction du Centre de Développement des Technologies Avancées (CDTA) ainsi que le département informatique de l'Université Saad Dahlab de Blida pour tous les efforts qui ont été déployés afin de nous inscrire en Master 2 Recherche.

Je tiens aussi à remercier Mr Oudjida, Chargé de Recherche au CDTA, et Mme Benblidia, Maître de Conférences à l'Université de Blida, d'avoir bien accepté de m'encadrer dans ce projet de Master.

Mes remerciements vont aussi à tous ceux qui m'ont aidé de près ou de loin à concrétiser ce travail.

#### Résumé

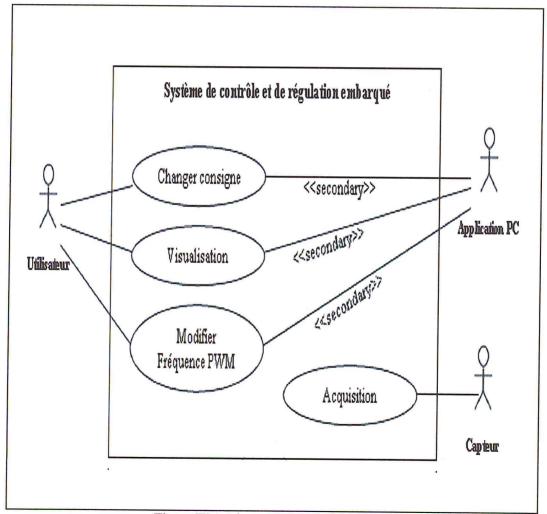

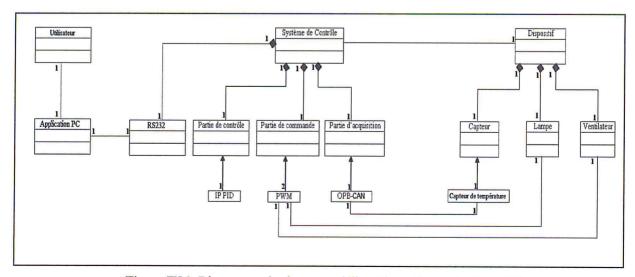

Dans ce Mémoire, nous présentons la mise au point d'une plateforme embarquée sur FPGA dédiée au contrôle et à la régulation des systèmes dynamiques. A cet effet, nous allons montrer à travers les chapitres de ce mémoire les différentes étapes que nous avons suivies pour développer les trois parties essentielles d'un système de contrôle ou de régulation, en l'occurrence : la partie de commande, la partie d'acquisition et la partie de contrôle. Cette dernière est réalisée par un PID (Proportionnel Intégral Dérivé) implémenté sous forme d'un IP. Comme cas pratique permettant la validation de notre système, nous avons implémenté ce dernier sur la plateforme Memec V2MB1000 qui contrôle un dispositif de régulation de température. Une Application software sur PC qui permet de modifier la consigne et de visualiser l'état du système à contrôler a été aussi développée.

Mots-clés— Capteur; Contrôle; Contrôle Embarqué(CE); Régulation; Field Programmable Gate Array (FPGA); Proportionnel Dérivé Intégral (PID); Microblaze; Modulation de Largeur d'impulsion (PWM); On-Chip Peripheral Bus; Propriété Intellectuelle (IP); Système Embarqué.

#### **Abstract**

In this thesis, an FPGA platform dedicated for embedded control and regulation of dynamic systems is presented. We will show the necessary steps to integrate the three essentials parts of any control system: Input interface, output interface and the controller. This latter is implemented as a PID (Proportional, Derivative, and Integral). As a practical case, we have implemented our system in Memec V2MB1000 platform and developed an experimental device in order to it in a real environment. We have also developed a user software application to facilitate the utilization of our platform and to display the state of the controlled process.

**Keywords**—Control; Embedded Control; Field Programmable Gate Array (FPGA); PID (Proportional, Derivative, and Integral); Embedded System; Intellectual Property (IP); Microblaze; On-Chip Peripheral Bus; Pulse Width Modulation (PWM); Regulation; Sensor.

#### ملخص

هذه المذكرة تناقش إنشاء نظام مكون من مسطحة من نوع مصفوفة البوابات المنطقية القابلة للبرمجة في الميدان لتعديل والتحكم في الأنظمة المتغيرة. لقد قمنا بإدخال أجزاء التحكم والإكتساب والمراقبة على نظامنا. إن جزء المراقبة مبني على طريقة العنصر تحكم تناسبي تكاملي تفاضلي. من أجل التحقق من فعالية النظام، قمنا بوضع هذا الأخير في مسطحة من أجل مراقبة سيره في وسطحقيقي للتحكم في درجة حرارة جهاز تجريبي. لقد قمنا أيضا بتطوير برنامج يسمح بتغيير عوامل التجربة ورسم نتائج هذه الأخيرة.

الكلمات الدالة: مراقبة، تعديل، نظام مضمن، مصفوفات البوابات المنطقية القابلة للبرمجة في الميدان، عنصر تحكم تناسبي تكاملي تفاضلي، مكشاف.

| IV.1.2. Description et Test Fonctionnel42                                |  |  |  |  |  |

|--------------------------------------------------------------------------|--|--|--|--|--|

| IV.2. Intégration et Développement des Pilotes47                         |  |  |  |  |  |

| IV. Conclusion58                                                         |  |  |  |  |  |

| Chapitre IV                                                              |  |  |  |  |  |

| Conception et Réalisation d'un Dispositif Expérimental59                 |  |  |  |  |  |

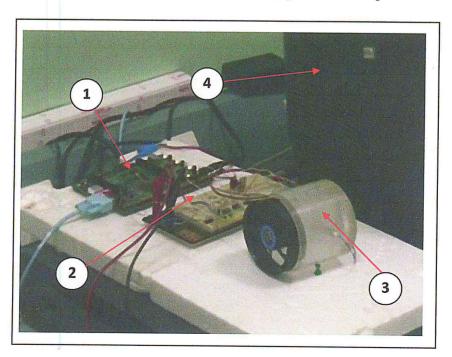

| I. Description et Conception Globale60                                   |  |  |  |  |  |

| I.1. Description Globale du Dispositif60                                 |  |  |  |  |  |

| I.2. Conception Préliminaire61                                           |  |  |  |  |  |

| II. Description Détaillée du Dispositif64                                |  |  |  |  |  |

| II.1. Capteur et Partie d'Acquisition64                                  |  |  |  |  |  |

| II.2. Commande d'une Lampe et d'un Ventilateur65                         |  |  |  |  |  |

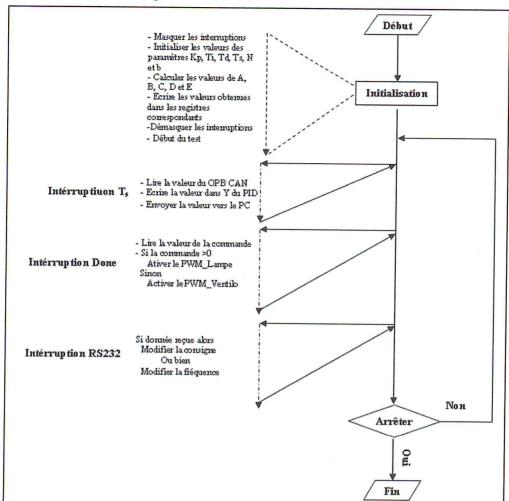

| II.3. Fonctionnement Interne du Système66                                |  |  |  |  |  |

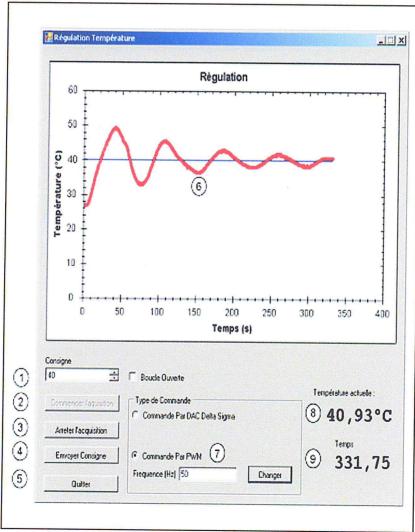

| II.4. Interaction et Visualisation des Données67                         |  |  |  |  |  |

| III. Conclusion69                                                        |  |  |  |  |  |

| Chapitre V70                                                             |  |  |  |  |  |

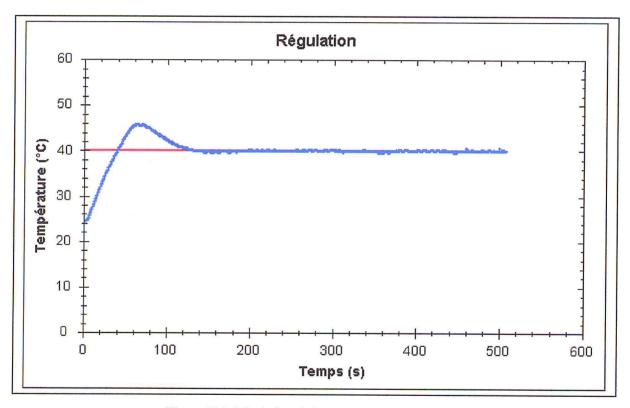

| Tests et Résultats Expérimentaux70                                       |  |  |  |  |  |

| I. Test de Fonctionnalité71                                              |  |  |  |  |  |

| II. Impact de la Précision73                                             |  |  |  |  |  |

| III. Test de Stabilité74                                                 |  |  |  |  |  |

| IV. Test de Poursuite                                                    |  |  |  |  |  |

| IV. Conclusion75                                                         |  |  |  |  |  |

| Conclusion et Perspectives76                                             |  |  |  |  |  |

| Annexes79                                                                |  |  |  |  |  |

| Annexe A: Régulateur PID80                                               |  |  |  |  |  |

| Annexe B : Montage d'un Amplificateur de Tension83                       |  |  |  |  |  |

| Annexe C : Conversion réel flottant $\rightarrow$ Réel en virgule fixe84 |  |  |  |  |  |

| Références Bibliographiques86                                            |  |  |  |  |  |

|                                                                          |  |  |  |  |  |

# Liste des Figures

| Figure I.1     | E   |

|----------------|-----|

| Figure I.2     | . 7 |

| Figure I.3     | .7  |

| Figure I.4     | 8   |

| Figure I.5     |     |

| Figure I.6     |     |

| Figure I.7     |     |

| Figure I.8     |     |

| Figure I.9     |     |

| Figure II.1    |     |

| Figure II.2    |     |

| Figure II.3    |     |

| Figure II.4    |     |

| Figure II.5    |     |

| Figure II.6    |     |

| Figure III.1   |     |

| Figure III.2   |     |

| Figure III.3   |     |

| Figure III.4   |     |

| Figure III.5   |     |

| Figure III.6   |     |

| Figure III.7   |     |

| Figure III.8   |     |

| Figure III.9   |     |

| Figure III.10  |     |

| Figure III.113 |     |

| Figure III.123 |     |

| Figure III.134 |     |

| Figure III.14  |     |

| Figure III.154 |     |

| Figure III.16  |     |

|                | -   |

| Figure III.1744  |

|------------------|

| Figure III.1845  |

| Figure III.1945  |

| Figure III.2046  |

| Figure III.2147  |

| Figure III.2249  |

| Figure III.23 50 |

| Figure III.24 54 |

| Figure III.25 55 |

| Figure III.2656  |

| Figure III.27 57 |

| Figure IV.1 61   |

| Figure IV.2 62   |

| Figure IV.3 63   |

| Figure IV.4 64   |

| Figure IV.5 65   |

| Figure IV.6 67   |

| Figure IV.7 68   |

| Figure V.171     |

| Figure V.272     |

| Figure V.373     |

| Figure V.474     |

| Goure V 5        |

## Liste des Tableaux

| Tableau I.1   | 6  |

|---------------|----|

| Tableau I.2   | 14 |

| Tableau III.1 |    |

| Tableau III.2 |    |

| Гаbleau Ш.3   |    |

| Tableau III.4 |    |

| Гаbleau Ш.5   |    |

|               |    |

| Tableau III.6 |    |

| Гаbleau III.7 | 54 |

### Liste des Abréviations

ASIC: Application-Specific Integrated Circuit

BMA: Booth Multiplication Algorithm

CAN : Convertisseur Analogique Numérique

CNA: Convertisseur Analogique Numérique

COTS: Commercial Off-The-Shelf

DSP: Digital-Signal-Processors

EDK: Embedded Design Kit

FPGA: Field Programmable Gate Array

GNU: GNU's Not UNIX

HDL: Hardware Description Language

HW/SW: Hardware / Software

IP: Intellectual Property

JTAG: Joint Test Action Group

LMB: Local Memory Bus

LQG: Linear Quadratic Gaussian

MAC: Multiply And Accumulate

MBMA: Modified Booth Multiplication Algorithm

ODMAC: Optimized Double Multiply And Accumulate

OPB: On-Chip Peripheral Bus

PWM: Pulse Width Modulation

PID: Proportionnel Intégral Dérivé

RMRMA: Recursive Multibit Recording Multiplication Algorithm

RISC: Reduced Instruction Set Computer

UML: Unified Modeling Language

# Introduction Générale

De nos jours, l'utilisation des systèmes de contrôle numérique est de plus en plus croissante (Appareils électroménagers, Voitures, Médecine, Industrie, Robotique,...) contraignant ainsi les concepteurs à proposer des solutions efficaces et à moindre coût. Dans le domaine des systèmes embarqués tels que la robotique ou bien l'industrie spatiale et l'aéronautique des contraintes plus difficiles sont imposées aux concepteurs. Effectivement, ces derniers doivent développer des solutions visant à optimiser les ressources disponibles (limitées) ainsi que la consommation de puissance qui représente un facteur clef de qualification des systèmes embarqués.

Il existe principalement quatre solutions pour l'intégration de contrôleurs numériques :

- Composants électroniques de type COTS (Commercial Off-The-Shelf). Cela comprend les microprocesseurs à usage général ainsi que les microcontrôleurs;

- Processeurs de type DSP (Digital-Signal-Processors) comme le TMS320C55x et le TMS320C64x, considérés respectivement comme étant le processeur réclamant le moins d'énergie et le processeur le plus performant du commerce ;

- Circuits reprogrammables de type FPGA (Field-Programmable Gate-Array), tels que ceux de Xilinx ou ceux d'Altera FPGA;

- Circuits de type ASIC (Application-Specific Integrated Circuit) qui sont des puces conçues et fabriquées selon une technologie donnée pour des solutions spécifiques ou à usage général.

Il est démontré que la solution ASIC représente l'approche qui donne les meilleurs résultats par rapport aux autres solutions (en termes de surface, consommation de puissance et vitesse). Cependant, la méthodologie de conception des circuits de type ASIC passe par plusieurs étapes aussi longues les unes que les autres et qui impliquent une augmentation du temps de développement et par conséquent du coût. D'un autre coté, les FPGAs exigent moins de temps de développement et peuvent être exploités à des fins de prototypage rapide et dans certains cas ils peuvent être utilisés comme solution finale.

Ce projet de Master s'insère dans le cadre du protocole de recherche 2011-2013, inscrit sous le contrat de recherche 21/CRSOC/DMN/CDTA/2011 au Centre de Développement des Technologies Avancées, et dont l'intitulé est : Contrôle Embarqué pour des Applications de Micromanipulation. L'objectif est de développer des contrôleurs numériques avancés (LQG, SSV, PID pour comparaison) sur FPGA pour la commande d'une micropince.

Le développement de telles solutions sur FPGA passe par plusieurs phases qui garantissent des propriétés telles la maintenabilité et la réutilisation. La première phase consiste à coder le contrôleur en langage HDL (VERILOG ou VHDL) en utilisant les spécifications établies à partir du cahier de charges. La deuxième phase permet d'effectuer un test fonctionnel du contrôleur dans l'environnement Simulink de Matlab. La dernière phase consiste à intégrer le contrôleur dans un système embarqué sur FPGA et de le valider définitivement dans un environnement réel.

Dans ce mémoire, nous nous intéresserons à la dernière phase du développement du contrôleur. Notre tache consiste à intégrer ce dernier dans une plateforme HW/SW de contrôle embarqué sur FPGA. Tout système de contrôle est composé essentiellement de trois parties : la partie de contrôle, la partie de commande et la partie d'acquisition. Nous exposons à travers les chapitres de ce mémoire les différentes étapes entreprises pour l'intégration et le test des différentes parties de notre système de contrôle. Enfin, un dispositif expérimental permettant la validation définitive de notre système dans un environnement réel doit être développé.

Ce Mémoire est organisé comme suit : dans le premier chapitre, nous commençons par une introduction aux systèmes embarqués et aux circuits FPGA. Le deuxième chapitre introduira les systèmes de contrôle et exposera le contexte et la problématique du projet. Dans le chapitre suivant, nous présentons les différentes étapes d'intégration des parties constituant notre système de contrôle embarqué. Le quatrième chapitre sera consacré à la conception et la réalisation d'un dispositif expérimental permettant le test de notre plateforme dans un environnement réel. Le dernier chapitre traitera les tests qui ont été réalisés et les résultats expérimentaux obtenus. Enfin nous terminons par une conclusion et des perspectives.

# Introduction aux FPGA et aux Systèmes Embarqués

Ce chapitre constitue une introduction aux systèmes embarqués sur FPGA et au contrôle et la régulation de processus physiques. Nous commençons tout d'abord par une brève présentation des FPGAs (Définition, domaines d'application, avantages et inconvénients,...) et au flot de conception matériel / Logiciel de Xilinx. Nous présentons aussi les outils de conception permettant le développement de solutions embarquées sur FPGA. Ensuite nous passons aux systèmes embarqués (Définition et domaines d'utilisation) et plus particulièrement à ceux implémentés sur FPGA.

#### I. Introduction aux FPGAs

#### I.1. Définition et Domaines d'Applications

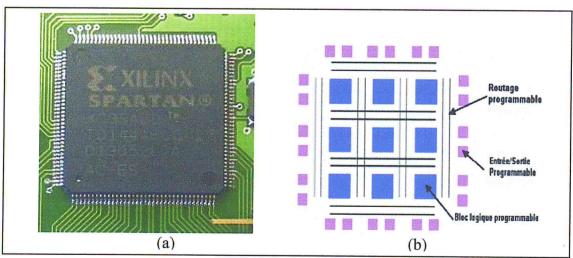

Un FPGA (Field-Programmable Gate Array) est un dispositif semi-conducteur contenant des composants à logique programmable (Blocs logiques) et des interconnexions programmables (routage programmable). Les blocs logiques peuvent exécuter n'importe quelle fonctionnalité depuis les fonctions logiques de base (comme : AND, OR, XOR, NOT) jusqu'aux fonctions complexes combinatoires. Les FPGAs comprennent aussi des éléments de mémoire (bascules, blocs complets de mémoire). Quelque soit la fonction logique, elle peut être réalisée par l'interconnexion des blocs logiques. La figure I.1.b représente une vue d'ensemble d'un FPGA [1].

Figure I.1. a) FPGA de Xilinx avec 400 000 portes b) Schéma d'ensemble d'un FPGA

La principale caractéristique des FPGAs est la reconfiguration. Cette dernière peut être même effectuée en cours de fonctionnement. On parlera alors de reconfiguration dynamique. Cette propriété est très intéressante car elle permet de développer des systèmes autonomes. Les FPGAs permettent aussi un prototypage rapide en comparaison avec la solution ASIC (Application-Specific Integrated Circuit), mais en contre partie ils sont moins rapides

et consomment plus d'énergie. Le tableau I.1 présente une comparaison entre les caractéristiques d'un FPGA par rapport à un ASIC.

Tableau I.1. Comparaison entre FPGA est ASIC [2].

| FPGA                                            | ASIC                                                   |  |

|-------------------------------------------------|--------------------------------------------------------|--|

| Flexibilité de programmation ;                  | Conception fixe ;                                      |  |

| • Délais de développement court ;               | développement court ; • Délais de développement long ; |  |

| <ul> <li>Seulement pour applications</li> </ul> | <ul> <li>Applications numériques,</li> </ul>           |  |

| numériques ;                                    | analogiques, mixtes;                                   |  |

| Consommation de puissance plus                  | • Faible consommation de puissance.                    |  |

| élevée.                                         |                                                        |  |

Donc pour des fins de recherche ou bien de test (Prototypage rapide), les FPGAs constituent un excellent choix. Parmi les fabricants de tels circuits reprogrammables, on trouve Abound Logic, Achronix, Actel, Altera, Atmel, Cypress, Lattice Semiconductor, Nallatech, QuickLogic, SiliconBlue, Tabula Inc., Tier Logic et Xilinx. Dans ce qui suit nous nous intéressons à l'architecture des FPGAs de Xilinx et plus précisément à la famille VIRTEX.

#### I.2. FPGAs Virtex

En 1998, Xilinx a introduit une nouvelle famille de FPGAs nommée Virtex et depuis plusieurs produits basés sur cette classe ont été mis sur le marché tels que : Virtex II, Virtex-E, Virtex 4 ou bien Virtex 5. La famille Virtex 5 est actuellement la plus utilisée car elle représente une solution à faible coût tout en délivrant de hautes performances.

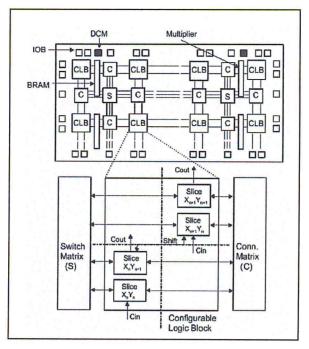

Un FPGA Virtex est composé essentiellement de quatre éléments qui sont [2]:

- Configurable Logic Bloc : il représente l'élément reconfigurable principal d'un Virtex. Il fournit des composants permettant l'exécution de fonctionnalités de logique combinatoire et séquentielle ;

- Block SelectRAM (RAM) : représente des modules mémoire de stockage ;

- Des Multiplieurs 18-bit x 18-bit;

- Blocks DCM (Digital Clock Manager): ces blocks permettent la distribution, la multiplication et la division du signal d'horloge,...

La figure I.2 [3] présente l'architecture interne d'un CLB qui contient quatre Slices :

Figure I.2. Architecture d'un FPGA Virtex.

Un Slice (voir figure I.3) est une petite unité de reconfiguration qui contient :

- Deux générateurs de fonction (F & G) qui peuvent être configurés comme Look-Up Table (LUT), ou bien comme registres à décalage,...;

- Deux Bascules-D;

- Des portes logiques arithmétiques ;

- Multiplexeurs larges;

- . .

Figure I.3. Architecture interne d'un Slice.

[3] contient plus de détails concernant l'architecture des FPGAs Viretx. Dans la section suivante nous allons présenter les plateformes d'évaluation FPGA et en particulier la plateforme MEMEC V2MB1000 qui a été utilisée dans notre projet.

#### I.3. Plateformes d'Evaluation FPGA

Une plateforme d'évaluation FPGA est un circuit imprimé contenant un circuit FPGA, un processeur (éventuellement), des périphériques d'E/S permettant l'interaction avec l'environnement externe. Ces plateformes permettent non seulement de tester de façon rapide et efficace des prototypes de test mais peuvent aussi être utilisées comme solution finale après validation. Pour cela, elles sont équipées de mémoire ROM leurs permettant de garder de façon définitive la solution finale.

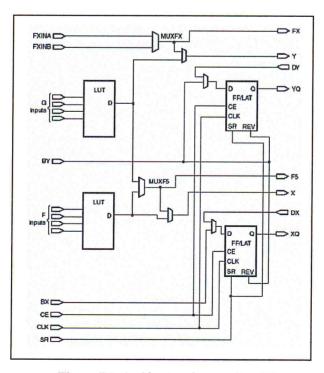

Pour notre cas, nous avons utilisé la plateforme d'évaluation MEMEC V2MB1000 [4] basée sur le FPGA XC2V1000-4FG456C de Xilinx (famille Virtex II). Cette plateforme est dotée de plusieurs types de périphériques (RS232, Leds, Boutons Switch,...) qui peuvent être utilisés selon les besoins du concepteur et la nature de l'application à développer. La figure I.4 représente une vue globale de la plateforme V2MB1000.

Figure I.4. Plateforme d'évaluation MEMEC V2MB1000.

#### Tels que:

- •1 : circuit PROM qui permet de conserver définitivement une conception donnée ;

- •2 : est un port JTAG qui permet la programmation du FPGA ;

- •3: mémoire DDR 16M x 16;

- •4: sources d'alimentation;

- •5 : est un port de réception LVDS ;

- •6: est un FPGA Virtex II, XC2V1000-4FG456C;

- •7: est un port d'émission LVDS;

- •8: deux horloges (25MHZ et 100MHZ);

- •9 : est un port de communication RS232 ;

- •10: DIP Switches;

- •11 : deux afficheurs sept-segments ;

- •12: boutons Switches.

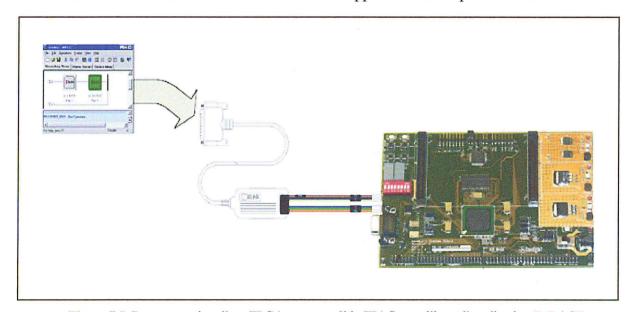

Le FPGA est programmé à partir d'un ordinateur en utilisant un câble JTAG et une application appropriée (voir figure I.5). Cette dernière fait partie d'un ensemble d'outils (voir la section suivante) permettant le développement de solutions sur FPGA, depuis les spécifications du cahier de charges jusqu'au test final sur la plateforme d'évaluation. Dans ce Mémoire nous nous intéressons aux outils de développement Xilinx pour FPGA.

Figure I.5. Programmation d'un FPGA avec un câble JTAG en utilisant l'application IMPACT.

#### I.4. Outils Xilinx pour FPGA

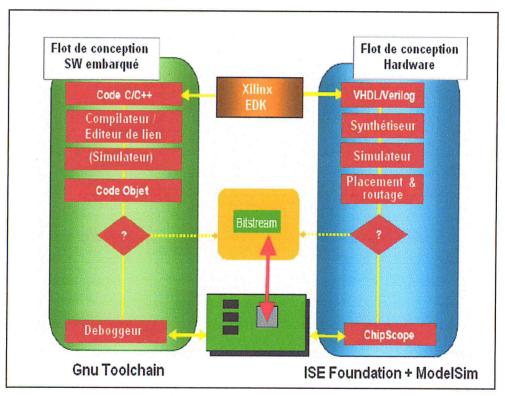

Le flot de conception Xilinx pour FPGA contient une multitude d'outils adaptés aux besoins du concepteur. Ces outils permettent d'accomplir ce qu'on appelle le CoDesign, c'est-à-dire associer d'un coté le développement Hardware en utilisant des langages HDL (Hardware Description Language) tels que Verilog ou bien VHDL et de l'autre coté le développement de software embarqué en utilisant des langages de programmation classiques tels que C ou bien C++. La figure I.6 est un schéma synoptique représentant les différentes étapes de développement d'une solution HW/SW en utilisant le flot de conception de Xilinx.

Figure I.6. Flot de conception HW/SW de Xilinx.

L'outil EDK (Embedded Design Kit) [5] de Xilinx permet de développer des solutions sur FPGA en faisant du Co-Design. Le flot de conception Hardware permet d'avoir en finalité des modules qui seront implémentés sur FPGA et qui feront office de circuits électroniques (Contrôleur de périphérique, Acquisition, Convertisseurs, ...). Le flot de conception software sert d'un autre coté à développer les applications permettant l'exploitation de la partie Hardware. Après avoir effectué plusieurs tests de vérification du bon fonctionnement de la partie Hardware ainsi que de la partie Software, on obtient en finalité un fichier appelé **Bitstream**. Ce dernier est obtenu après plusieurs étapes (Synthèse, placement, routage, ...) et est utilisé pour programmer en dernier lieu le FPGA. Il faut savoir que la conception et le développement de la partie Hardware suit une méthodologie bien définie sur plusieurs phases

jusqu'à son implémentation effective sur FPGA ou bien sous forme d'ASIC (circuit intégré) en passant par des étapes de vérification très rigoureuses assurant ainsi son bon fonctionnement [6][7]. L'outil de simulation Modelsim [8] est aussi très utilisé durant l'étape de vérification. Il permet non seulement la simulation du fonctionnement d'un module mais aussi la simulation du fonctionnement de toute une plateforme FPGA. Les étapes de synthèse et de placement/routage sont accomplies par EDK de façon transparente en utilisant les outils fournis avec ISE Foundation (tel que XST pour la synthèse). Ce dernier est un Kit de développement pour FPGA fournissant tous les outils nécessaires depuis l'écriture du code HDL jusqu'au test Hardware. Quant à la partie software, EDK utilise une suite d'outils de programmation de GNU (GNU Toolchain) qui contient essentiellement plusieurs compilateurs, Bintuils (Editeur de liens, assembleur,...) ainsi que des outils nécessaires au débogage et à la vérification du code. Dans ce mémoire nous nous intéressons particulièrement à l'outil EDK et à l'intégration de modules et d'applications embarquées sur FPGA.

#### II. Introduction aux Systèmes Embarqués

#### II.1. Définition et Domaines d'Applications

Un système embarqué peut être défini comme un système autonome intégrant des logiciels et de l'électronique et éventuellement des parties mécaniques ou autres. Il est dédié à une tâche bien précise. Les ressources dont il dispose sont limitées. Cette limitation est généralement d'ordre spatial (taille limitée) et énergétique (source d'énergie limitée).

Malgré que les caractéristiques des systèmes embarqués diffèrent selon l'application visée, nous pouvons néanmoins en citer les propriétés les plus communes :

- Ils sont généralement conçus pour exécuter une tache bien précise ;

- Ils doivent satisfaire des contraintes très difficiles (consommation d'énergie, surface, rapidité,...);

- •Ils doivent interagir avec leur environnement et calculer les résultats d'un traitement en temps réel.

Aujourd'hui ces systèmes sont très présents dans notre vie quotidienne et leur production dépassent de loin celle des ordinateurs personnels. Les domaines dans lesquels on trouve des systèmes embarqués sont de plus en plus nombreux :

- Transport : Automobile, Aéronautique (avionique), etc ;

- Astronautique : Fusée, Satellite artificiel, Sonde spatiale, etc ;

- •Militaire: Missiles, Avions de chasse, etc;

- Télécommunication : Set-top box, Téléphonie, Routeur, Pare-feu, Serveur de temps, Téléphone portable, etc ;

- Electroménager : Télévision, Four à micro-ondes ;

- Impression: Imprimante multifonctions, Photocopieur, etc;

- •Informatique : Disque dur, Lecteur de disquette, etc ;

- Multimédia : Console de jeux vidéo, Assistant personnel ;

- Guichet automatique bancaire (GAB);

- Equipement médical;

- Automate programmable industriel, Contrôle-commande;

- Métrologie.

Figure I.7. Exemples d'utilisation des systèmes embarqués.

Un système embarqué est constitué d'un processeur exécutant des applications softwares (applications dédiées, système d'exploitation, ...). Dans la section suivante nous nous intéressons aux différents types de processeurs et plus particulièrement à ceux utilisés dans les systèmes embarqués sur FPGA.

#### II.2. Processeur

Il existe deux types de processeurs utilisés dans les systèmes embarqués :

- •Hardcore : ce type désigne des circuits intégrés (ASIC) qui sont fabriqués et dédiés à une application bien précise. Ce genre de processeurs ne peut être reconfiguré après sa fabrication. Il existe plusieurs genres de processeurs Hardcores qui sont adaptés à des applications spécifiques tels que : les DSPs (Digital Signal Processor) pour les applications de traitement du signal, les GPUs (Graphic Processing Units) pour les applications de visions et de traitement d'images, etc ;

- •Softcore : ce type désigne les processeurs qui sont décrits entièrement en langage HDL (Hardware Description Language) tels que VHDL ou bien Verilog et qui sont généralement implémentés dans une logique reconfigurable (FPGA). Ce genre de processeurs présente l'énorme avantage d'être reconfigurable c'est-à-dire qu'il peut être adapté selon les besoins de l'application visée (Performance, consommation de puissance,...). L'autre avantage réside dans le fait que n'importe quel nombre de processeurs Softcores peut être intégré sur FPGA (Dans la limite des capacités de ce dernier bien sûr) et que son coût est nettement inférieur à celui d'un processeur Hardcore. Cependant, ce dernier est bien plus performant.

Notons que plusieurs familles de FPGA intègrent un ou plusieurs processeurs Hardcores, comme c'est le cas pour le Virtex II-Pro qui contient deux processeurs PowerPC.

Dans ce mémoire nous nous sommes limités à l'utilisation du processeur softcore *Microblaze* [9] de Xilinx pour les raisons suivantes :

- •La plateforme matérielle utilisée (MEMEC V2MB1000) contient un FPGA (Virtex II, XC2V1000-4FG456C) qui ne comprend pas de processeur Hardcore;

- Facilité d'utilisation et de configuration du processeur Microblaze à l'aide de l'outil EDK de Xilinx;

- •Microblaze peut être intégré dans un système complexe qui contient plusieurs périphériques d'E/S et est supporté par plusieurs systèmes d'exploitation embarqués tels que : uClinux, Xilinx Xilkernel, FreeRTOS, etc.

Dans ce qui suit, nous présentons une vue d'ensemble des processeurs Softcores existants ainsi que sur l'architecture du processeur Microblaze et des systèmes embarqués basés sur ce dernier.

#### II.2.1. Vue d'Ensemble sur les Processeurs Softcores Existants

Il existe plusieurs processeurs Softcores qui peuvent être utilisés dans les systèmes embarqués sur FPGA. Pour les FPGAs de Xilinx, on distingue essentiellement trois processeurs largement utilisés :

- Microblaze : est un processeur RISC 32 bits développé par Xilinx. Il a été conçu et optimisé spécialement pour les FPGAs de Xilinx. Microblaze est distribué avec EDK, cependant son code source n'est pas accessible ;

- •LEON: est un processeur RISC 32 bits compatible avec l'architecture de SPARC V8. Il est hautement configurable et son code source est accessible sous la licence GNU GPL;

- OpenRisc: est un processeur RISC 32 bits. OpenRisc est gratuit (Open Source) et peut être obtenu sur le site de OpenCores (Code Verilog) sous la licence GNU GPL.

Le tableau I.2 [10] présente une comparaison succincte entre ces trois processeurs.

Tableau I.2. Comparaison entre Microblaze, LEON et OpenRisc.

| Processeur | Avantages                              | Inconvénients                        |

|------------|----------------------------------------|--------------------------------------|

| Microblaze | • Optimisé pour les                    | • Ne contient pas de MMU (Memory     |

|            | FPGAs de Xilinx;                       | Managment Unit);                     |

|            | • Utilisation se ressources minimisée; | Code source non disponible.          |

|            | • Bien documenté                       |                                      |

|            | • Facilité d'ajout de                  |                                      |

|            | périphériques utilisateur.             |                                      |

| LEON       | • Hautes performances;                 | • Utilise beaucoup de ressources sur |

|            | • Code source disponible.              | FPGA.                                |

| OpenRisc   | • Bonne Performances ;                 | • Utilise beaucoup de ressources sur |

|            | • Code source disponible.              | FPGA;                                |

|            |                                        | • Pas bien documenté ;               |

|            |                                        | Outils de développement pauvres.     |

#### II.2.2. Architecture de Microblaze

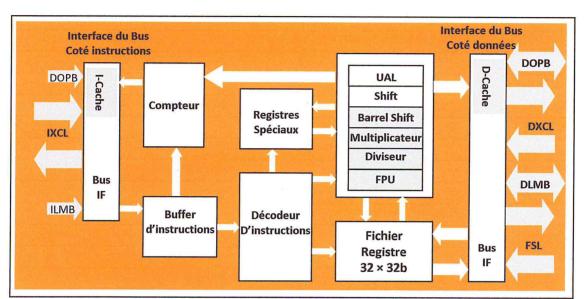

Microblaze est un processeur RISC 32 bits doté d'un pipeline à trois étages. Il contient 32 registres à usage général, une UAL et un riche ensemble d'instructions pour les applications embarquées. Il est à noter que Microblaze est une propriété de Xilinx et que son code source n'est pas disponible. La figure I.8 représente un schéma synoptique de l'architecture interne d'un processeur Microblaze.

Figure I.8. Architecture interne de Microblaze.

Les principales caractéristiques de Microblaze sont :

- •32 registres à usage général;

- •Pipeline à trois étages ;

- Supporte le bus OPB (On-Chip Peripheral Bus). Ce dernier est une interface à usage général qui est conforme à la technologie CoreConnect de IBM. Cette technologie permet aussi de développer des périphériques pour des systèmes se basant sur le processeur PowerPC;

- •Connexion directe à On-Chip Memory (BRAM) à travers le bus LMB (Local Memory Bus);

- •Possibilité d'ajout d'un Co-Processeur utilisant une connexion FSL (Fast Simplex Link);

- •Peut travailler avec une fréquence pouvant atteindre 200 Mhz sur Virtex 4 et 170 Mhz sur Virtex 2 ;

- Multiplicateur et diviseur Hardware réduisant le temps d'exécution des opérations.

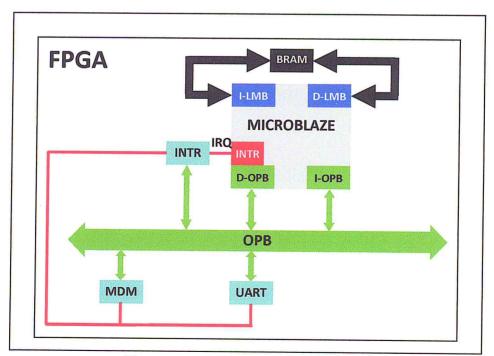

#### II.2.3. Système Embarqué sur FPGA

Nous avons vu qu'un système embarqué est un système autonome intégrant des logiciels et du matériel ce qui signifie la présence d'un processeur et des périphériques connectés à ce dernier à travers un Bus. Nous avons vu aussi que les FPGAs permettent l'intégration des processeurs Softcores qui sont moins chers, configurables mais aussi moins performants que les processeurs dédiés. Dans notre cas, nous utilisons la plateforme MEMEC V2MB1000 qui ne contient pas de processeur Hardcore à l'instar de la Virtex 2 Pro. Nous sommes donc contraints à utiliser le processeur Microblaze.

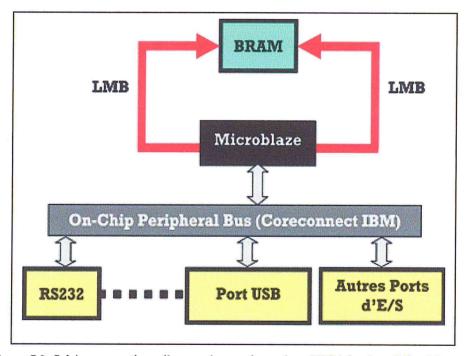

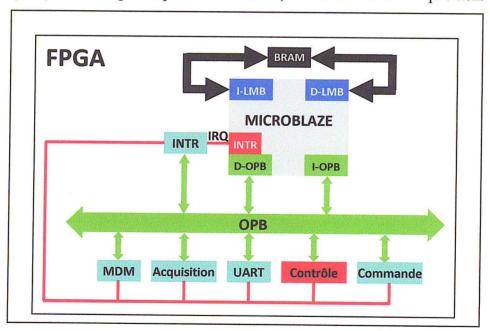

Notre système embarqué est constitué du processeur Microblaze connecté à travers le bus OPB aux différents périphériques d'E/S. Nous utilisons comme mémoire centrale, la BRAM présente sur le FPGA. Cette dernière est reliée à Microblaze à travers le Bus LMB (Local Memory Bus). La figure I.9 représente un schéma synoptique d'un système embarqué sur FPGA ayant Microblaze comme processeur.

Figure I.9. Schéma synoptique d'un système embarqué sur FPGA basé sur Microblaze.

Ce genre de système peut être développé facilement en utilisant EDK. Ce dernier dispose d'une base de données contenant les sources HDL (en Verilog ou en VHDL) de plusieurs modules qui peuvent être soit des contrôleurs de périphériques d'E/S (RS232, USB,...) soit un contrôleur d'interruption ou tout simplement un module dédié à une tâche bien précise (traitement d'image, traitement de la voie, ...). Ces modules doivent être impérativement compatibles-OPB afin qu'ils puissent être gérés à travers des applications embarquées.

#### **III. Conclusion**

Dans ce chapitre nous avons présenté une introduction aux circuits FPGA. Ces derniers permettent un prototypage rapide et une conception à la fois de la partie matérielle et logicielle du système à concevoir. Nous avons exposé en particulier les FPGAs de la famille Virtex de Xilinx ainsi que le flot de conception qui contient un ensemble d'outils adaptés au développement matériel et logiciel. Nous avons aussi présenté les systèmes embarqués et leurs domaines d'application. Nous nous sommes intéressés plus particulièrement aux systèmes embarqués sur FPGA. Dans le chapitre suivant, nous allons présenter une introduction aux systèmes de contrôle et exposer la problématique et le contexte de notre projet tout en situant notre tache exacte.

# Introduction aux Systèmes de Contrôle

Dans ce chapitre nous présentons une introduction aux systèmes de contrôle. Nous exposons de façon brève le principe de fonctionnement d'un système de contrôle et de régulation et ses principales parties ainsi que le fonctionnement du régulateur PID (Proportionnel, Intégral, Dérivé). Nous finirons par présenter la problématique de notre projet et dans quel contexte s'insère ce dernier.

#### I. Introduction aux Systèmes de Contrôle

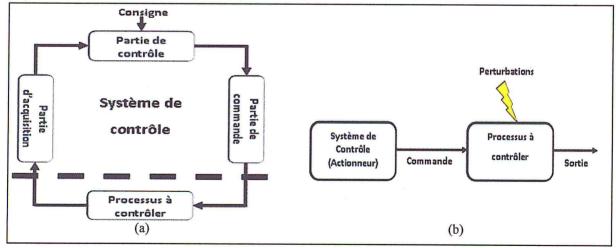

Dans de nombreux systèmes et produits actuels, il est indispensable de maintenir des grandeurs physiques (Température, vitesse, débit,...) à des valeurs déterminées dans les installations industrielles ou bien simplement dans des appareils de tous les jours (Four, climatiseurs,...) et cela en dépit des variations internes ou externes influant sur ces dernières. Dans le cas où ces perturbations sont minimes, un simple réglage dit en boucle ouverte est suffisant pour maintenir le processus à contrôler à la valeur désirée. Cependant, dans la plupart des cas, le réglage en boucle ouverte ne permet pas l'obtention des résultats attendus car ce dernier est trop brut ou bien instable. Une comparaison en permanence entre la valeur mesurée du paramètre à régler et la valeur souhaitée s'impose pour avoir un meilleur contrôle du processus. La figure II.1 représente le fonctionnement d'un système de contrôle et de régulation en boucle fermée et en boucle ouverte.

Figure II.1. Types des systèmes de contrôle (a) Contrôle en boucle fermée (b) contrôle en boucle ouverte.

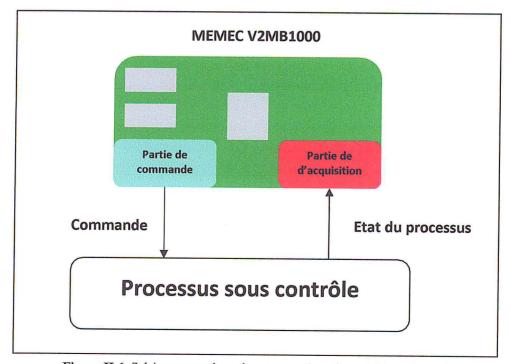

En général un système de Contrôle ou de régulation en boucle fermée est composé essentiellement de trois parties :

• Partie d'acquisition: cette partie permet de récupérer la valeur de l'état du processus à contrôler, comme la température, la vitesse, la pression, etc;

• Partie de contrôle: cette partie permet de calculer la valeur de la commande à appliquer sur le processus afin de satisfaire la consigne imposée par l'utilisateur; Partie de commande: cette partie permet d'appliquer la commande calculée par la partie de contrôle sur le processus à contrôler.

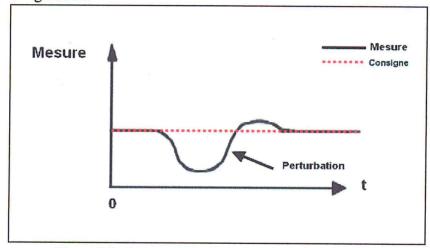

Le contrôle d'un processus donné peut être effectué soit en régulation soit en asservissement. Dans le cas de contrôle d'un processus en régulation, la valeur de la consigne est maintenue constante et le système de régulation doit maintenir l'état du processus malgré les perturbations externes. Dans le milieu industriel, l'aspect de régulation est primordial car les valeurs des consignes sont en général constantes. La figure II.2 montre le comportement d'un processus en régulation.

Figure II.2. Comportement d'un processus en régulation.

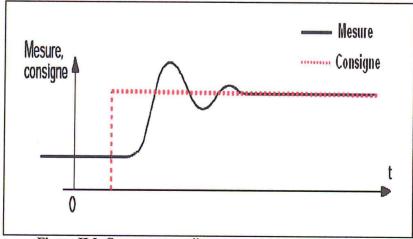

Dans le cas de contrôle d'un processus en asservissement, la valeur de la consigne est modifiée par l'opérateur ce qui induit un changement du point de fonctionnement du processus à contrôler. La figure II.3 représente le comportement d'un processus en asservissement.

Figure II.3. Comportement d'un processus en asservissement.

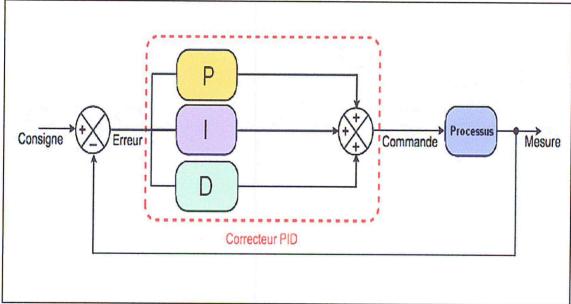

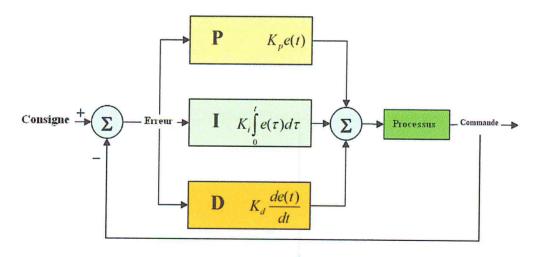

#### I.2. Régulateur PID (Proportionnel Intégral Dérivé)

En industrie, le régulateur PID (Proportionnel Intégral Dérivé) représente le standard le plus utilisé (voir Annexe A). Il permet de contrôler ou de réguler en boucle fermée à l'aide de ses trois actions (P, I et D) les performances d'un grand nombre de processus industriels (température, débit, vitesse, déplacement, ...). Un régulateur PID remplit essentiellement les trois fonctions suivantes :

- •Il fournit un signal de commande en tenant compte de l'état du processus par rapport à la consigne de l'utilisateur ;

- •Il élimine l'erreur statique en utilisant l'action Intégral ;

- •Il anticipe les variations de l'état du processus en utilisant l'action Dérivé.

La figure II.4 présente le principe de fonctionnement d'un régulateur PID.

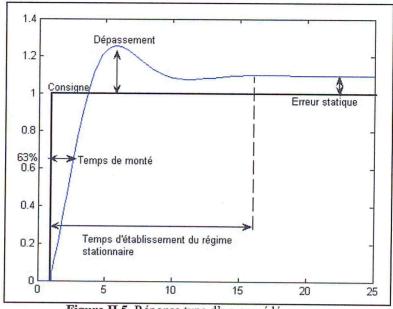

Figure II.4. Principe de fonctionnement d'un PID.

Toutes les équations régissant le fonctionnement des trois actions P, I et D sont expliquées et détaillées dans [11] (voir annexe A). Le réglage d'un PID consiste à déterminer les coefficients des actions P, I et D afin d'obtenir une réponse adéquate du processus et de la régulation. L'objectif est d'être robuste, rapide et précis. Pour cela, il faut limiter le ou les éventuels dépassements (overshoot). Le critère de robustesse représente le critère le plus important et le plus critique. En effet, ce dernier doit garantir un fonctionnement correct même si l'état du processus subit des variations externes. Le critère de rapidité dépend du temps de monté et de celui d'établissement du régime stationnaire (voir figure II.5). Quant au critère de précision, il dépend de l'erreur statique.

Figure II.5. Réponse type d'un procédé.

#### II. Contexte et Problématique

Ce travail de Master s'intègre dans le cadre du protocole de recherche 2011/2013 au Centre de développement des Technologies Avancées inscrit dans le projet dont l'intitulé est Contrôle embarqué pour des applications de micromanipulation. Notre but consiste à intégrer les contrôleurs développés dans un système embarqué en les dotant d'une interface leur permettant de communiquer avec le processeur du système ainsi que d'un ensemble de pilotes qui permettent l'accès à ces contrôleurs à travers une application embarquée.

Figure II.6. Schéma synoptique de notre système de contrôle embarqué.

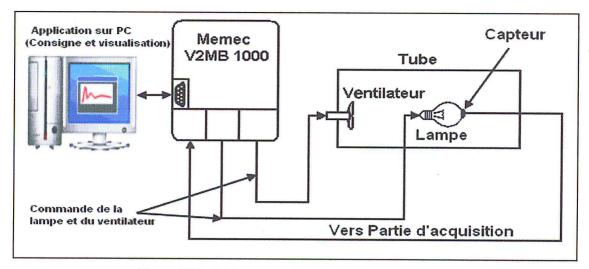

Nous visons ainsi le développement d'une solution HW/SW embarquée sur FPGA pour les systèmes de contrôle. Il s'agit ici en premier lieu, d'intégrer les parties d'acquisition et de commande sur la plateforme V2MB1000 en réutilisant et en adaptant des modules à notre cas. Cette tache est essentielle car elle permet au système de contrôle d'avoir les données nécessaires sur le processus à contrôler et de modifier l'état de ce dernier en appliquant une commande donnée. L'étape suivante consiste à intégrer la partie de contrôle au sein de notre système de contrôle embarqué. Cette partie est implémentée sous forme d'un module Hardware (Propriété Intellectuelle: IP) réalisant le travail d'un PID. La dernière étape consiste à valider définitivement notre système dans un environnement réel. Il s'agit de contrôler et de réguler la température d'un dispositif expérimental composé d'un tube contenant un ventilateur, une lampe halogène et un capteur. Le développement d'une application sur PC permettant à l'utilisateur d'interagir avec le système et de visualiser l'état du dispositif expérimental est aussi nécessaire.

# Intégration du Système de Contrôle Embarqué

Dans ce chapitre, nous présentons les différentes étapes permettant l'intégration de notre système de contrôle embarqué sur FPGA. Dans le chapitre précédent, nous avons vu que tout système de contrôle est constitué de trois parties: la partie d'acquisition, la partie de commande et la partie de contrôle. En premier lieu nous allons créer à l'aide de l'outil EDK un système de base avec un fonctionnement minimal, contenant un processeur Microblaze et quelques périphériques. Ensuite nous allons procéder à l'intégration, au développement des pilotes appropriés et au test des modules jouant le rôle de la partie de commande, d'acquisition et de contrôle.

### I. Configuration du Système Matériel de Base

Cette étape consiste à créer à l'aide de l'outil EDK un système embarqué de base [12] composé du processeur Microblaze relié à plusieurs modules ou périphériques à travers le bus OPB (On Chip Peripheral Bus) [13]. Notre système est constitué des éléments suivants:

- Microblaze;

- •Une BRAM interne reliée à Microblaze à travers le bus LMB (Local Memory Bus);

- •Un contrôleur d'interruptions;

- •Un contrôleur du port série RS232;

- MDM (Microblaze Debug Module): c'est un module de débogage pour Microblaze;

Figure III.1. Architecture du système de base.

Par analogie avec l'ordinateur personnel qui a comme entrée standard le clavier et comme sortie standard l'écran, le port RS232 constitue pour notre système embarqué l'entrée et la sortie standard. L'utilisation de ce port se fait au moyen du logiciel HyperTerminal ou tout autre logiciel équivalent (dans notre cas **Tera Term Pro**). Effectivement, ce dernier permet non seulement d'afficher les données provenant du port RS232 mais aussi d'en envoyer.

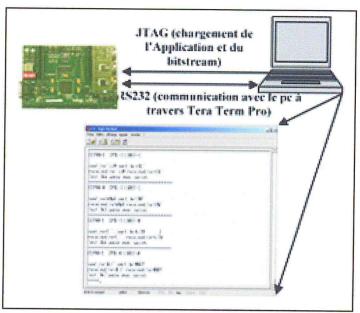

Figure III.2. Procédure de communication entre la plateforme et un PC.

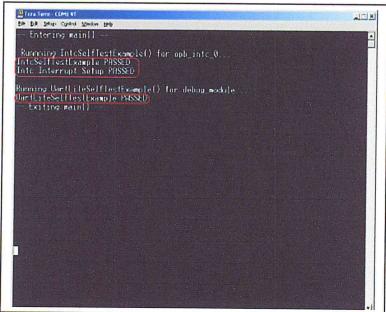

L'étape suivante consiste à générer le Bitstream correspondant à notre configuration et à exécuter l'application de test. Cette dernière permet de vérifier le bon fonctionnement des différents périphériques faisant partie de notre système de base. Le résultat d'exécution de l'application sera affiché à travers le logiciel Tera Term Pro comme le montre la figure III.3.

Figure III.3. Résultat d'exécution de l'application de test.

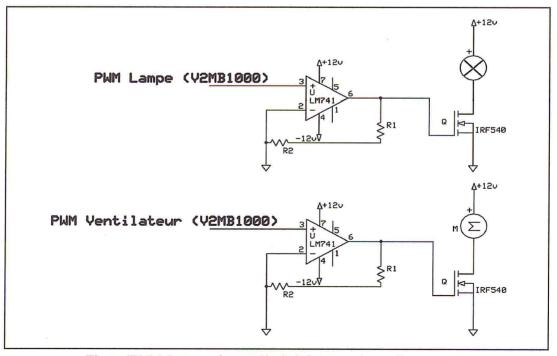

## II. Intégration de la Partie Commande

Dans cette étape, nous allons procéder à l'intégration de la partie de commande sur la plateforme MEMEC V2MB1000. Cette partie permet au système d'appliquer une commande sur le processus à contrôler afin d'amener l'état de ce dernier à une situation proche de la consigne imposée par l'utilisateur. Cette fonctionnalité peut être accomplie soit par un Convertisseur Numérique/Analogique (CNA) soit par un PWM (Modulation de largeur d'impulsion) [14]. Dans notre cas, la plateforme MEMEC V2MB1000 ne contient pas initialement un CNA, néanmoins ce dernier peut être remplacé par un module HDL au niveau du FPGA. A cet effet, nous utiliserons le module OPB Delta Sigma Digital To Analog existant au niveau de EDK. Ce dernier permet un contrôle en continu d'un processus donné. La deuxième solution consiste à utiliser un PWM qui permet de contrôler un processus donné en mode discret. Cette fonctionnalité peut être réalisée par la réutilisation du module OPB Timer-Counter qui peut être utilisé en mode PWM.

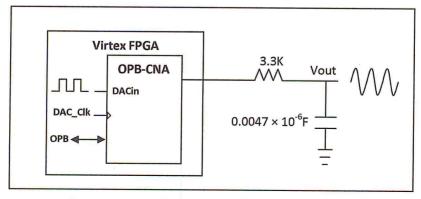

## II.1. OPB Delta Sigma Numérique/Analogique

Un convertisseur Numérique/Analogique permet de convertir une valeur numérique en un niveau de tension qui lui correspond. Cette fonctionnalité peut être effectuée par le module OPB-CNA delta sigma Softcore nécessite l'utilisation d'un filtre passe bas externe [15]. Ce dernier est un circuit simple composé d'une résistance reliée en série à une capacité (voir figure III.4). Les principales caractéristiques de ce module de conversion sont :

- Taille configurable de la donnée à convertir (2 jusqu'à 16 bits) ;

- Utilisation en mode interruption ;

- •16 entrées pour le FIFO;

- •Interface OPB (OnChip peripheral Bus) 32 bits.

Figure III.4. Module de conversion Numérique/Analogique.

Dans ce qui suit, nous donnons brièvement une description des signaux entrées/sorties, des interruptions, des paramètres ainsi que des registres faisant partie du module OPB-CNA qui permettent sa configuration.

Les signaux d'E/S du module OPB-CNA sont divisés en deux catégories :

- •Les signaux du OPB-CNA: ces signaux sont en relation directe avec le fonctionnement interne du OPB-CNA. Il y a trois signaux d'E/S qui sont :

- Dac\_clk\_en : ce signal d'entrée permet de synchroniser la conversion du CNA avec le signal d'horloge du système ;

- Read\_en : ce signal d'entrée permet de lire une nouvelle valeur à partir du FIFO afin de la convertir en un niveau de tension;

- Dac\_out : ce signal de sortie représente la valeur du nombre binaire convertie lue à partir du FIFO.

- •Les signaux OPB : ces signaux permettent à une application embarquée d'accéder soit en lecture soit en écriture à un registre du module OPB-CNA. On peut citer essentiellement les signaux suivants:

- OPB\_Clk: ce signal d'entrée est connecté directement à l'horloge du système;

- OPB\_Rst: ce signal d'entrée est connecté au signal système qui permet la remise à zéro du système ;

- IP2INTC\_Irpt: ce signal de sortie représente l'interruption système du module OPB-CNA;

- **OPB\_RNW**: ce signal d'entrée est mis à '1' par le processeur dans le cas d'une opération de lecture d'un registre ou bien à '0' dans le cas d'une écriture.

Le module OPB-CNA peut être ajusté par l'utilisateur en modifiant plusieurs paramètres notamment :

- •C\_NUM\_DAC\_BITS: ce paramètre représente la taille en bit du OPB-CNA qui varie entre 2 et 16;

- C\_BASE\_ADRESS: ce paramètre représente l'adresse du premier registre du OPB-CNA.

Le module OPB-CNA contient plusieurs registres adressables, accessibles en Lecture/Ecriture. L'adresse de base du premier registre est spécifiée dans le paramètre C\_BASE\_ADRESS. Ces registres permettent d'activer et d'initialiser le module, d'avoir des informations sur l'état du FIFO ou bien de définir le comportement du module en utilisant les interruptions. Le tableau III.1 regroupe les registres les plus importants du module OPB-CNA.

Tableau III.1. Quelques registres du CNA.

| Dogistva                  |                   | Fonction |                                 |  |

|---------------------------|-------------------|----------|---------------------------------|--|

| Registre                  | Accès             | Bits     | Description                     |  |

|                           | Lecture/Ecriture  | 0-29     | Réservé                         |  |

|                           |                   |          | Remise à zéro du FIFO           |  |

|                           |                   | 30       | '1' : remet à zéro le FIFO.     |  |

| Registre de Contrôle (CR) |                   |          | '0' : Opération normale.        |  |

| registre de controle (CR) |                   | 31       | Activation du CNA               |  |

|                           |                   |          | '1' : active le CNA.            |  |

|                           |                   |          | '0': désactive et remet le      |  |

|                           |                   |          | CNA à zéro.                     |  |

| Registre d'occupation du  | Lecture           | 0-26     | Réservé                         |  |

| FIFO (OCCY)               |                   | 27-31    | Nombre d'éléments dans le       |  |

|                           |                   |          | FIFO.                           |  |

|                           | Lecture /Ecriture | 0-26     | Réservé                         |  |

| Registre d'interruption   |                   | 27-31    | Une interruption est générée    |  |

| programmable (PIRQ)       |                   |          | si la valeur de ce registre est |  |

|                           |                   |          | supérieure à celle du registre  |  |

|                           |                   |          | OCCY                            |  |

Le fonctionnement du OPB-CNA peut être régit en mode interruption ou en mode scrutation (Polling mode). Le module OPB-CNA possède deux interruptions qui permettent la gestion du nombre de données présentes au niveau du FIFO :

- •FIFO EMPTY: cette interruption est mise à '1' lorsque le FIFO est vide;

- •FIFO PIRQ: cette interruption est mise à '1' lorsque le nombre de données au niveau du FIFO est supérieur à la valeur présente dans le registre PIRQ.

Les pilotes (interface entre l'application et le matériel) qui permettent l'utilisation du module OPB-CNA sont fournis avec EDK [15]. Ces derniers permettent:

- •L'initialisation et la remise à zéro ;

- •Lancer ou bien arrêter la conversion;

- Activer ou bien désactiver les interruptions ;

- Consulter l'état du FIFO (Nombre de données);

- Ajouter des données au FIFO.

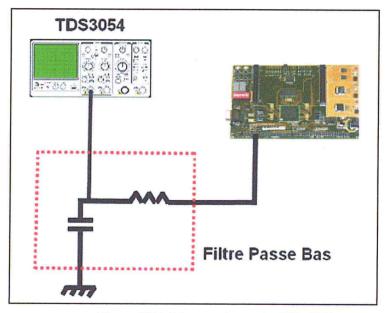

Pour tester le fonctionnement du module OPB-CNA, nous utiliserons l'oscilloscope numérique Tektronix TDS3054 [16]. Ce dernier sera relié à la sortie du filtre passe bas à l'aide d'une sonde (voir figure III.5).

Figure III.5. Montage de test du OPB-CNA

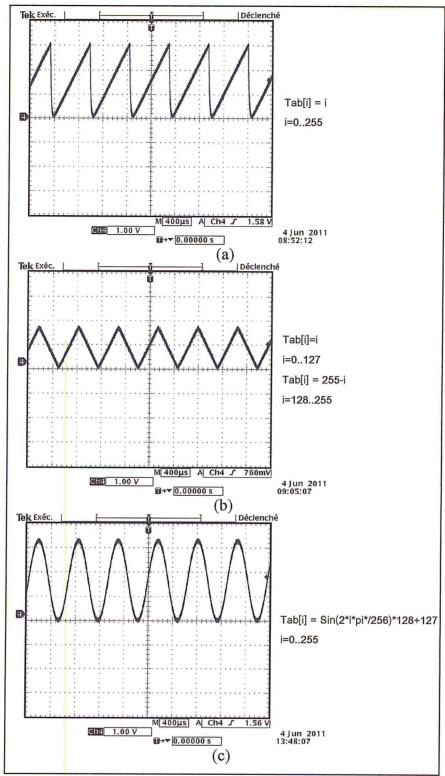

Le test consiste à générer à l'aide d'un programme embarqué sur la plateforme MEMEC V2MB1000 plusieurs types de signaux analogiques. En respectant le fonctionnement du OPB-CNA décrit dans [15], la conversion d'une valeur située dans le FIFO en un niveau de tension se fait à chaque fois que le signal **READ\_EN** est mis à '1'. Cette opération (mise à '1' du signal READ\_EN) doit se faire chaque 256 tops d'horloge laissant ainsi le temps au module OPB-CNA de convertir la valeur courante avant d'entamer la valeur suivante. Le programme embarqué extrait d'un tableau la valeur à convertir chaque 256 tops d'horloge et l'écrit dans le FIFO. La figure III.6 présente les signaux qui ont été générés avec le programme embarqué et les valeurs du tableau correspondantes.

Figure III.6. Test de génération de signaux analogiques (a) Dents de scie (b) Triangulaires (c) Sinusoïdaux.

Il est clair que l'utilisation d'un OPB-CNA peut s'avérer très utile, cependant ce dernier n'est pas adapté au contrôle de certains dispositifs tels que les transistors MOSFET qui se surchauffent rapidement avec un contrôle en continu. Dans la section suivante nous présentons une autre méthode qui permet de commander des dispositifs en mode discret tout

en permettant un ajustement précis du fonctionnement voulu.

# II.2. Modulation de Largeur d'Impulsion (PWM)

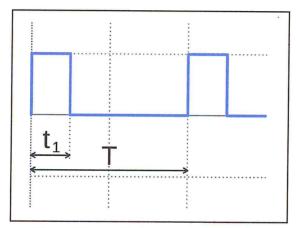

La technique PWM est couramment utilisée pour synthétiser des signaux continus à l'aide de circuits au fonctionnement tout ou rien, ou plus généralement à états discrets. La fonction PWM possède deux propriétés importantes à gérer qui définissent son fonctionnement : la période et le rapport cyclique. Ce dernier est défini par la relation suivante :

$$R = (t1 / T) \times 100$$

Tel que T représente la période et t1 est la durée pendant laquelle le signal est mis à '1'.

Figure III.7. Période et rapport cyclique d'un PWM.

Dans notre cas, cette fonction est réalisée par le module OPB Timer-Counter [17]. Ce dernier contient deux compteurs configurables (jusqu'à 32 bits). Il peut être utilisé en 3 modes, entre autres le mode PWM. Le tableau suivant présente les différents registres présents sur le module OPB Timer-Counter :

| Tableau 111.2. Registres du OFD Timer-Counter. |             |         |                  |                                 |

|------------------------------------------------|-------------|---------|------------------|---------------------------------|

| Registre                                       | Offset      | Taille  | Accès            | Description                     |

| TCSR0                                          | 0x00        | 32 bits | Lecture/Ecriture | Registre de contrôle du premier |

|                                                | 15.555 8 81 |         |                  | compteur.                       |

| TLR0                                           | 0x04        | 32 bits | Lecture/Ecriture | Registre de chargement          |

| TCR0                                           | 0x08        | 32 bits | Lecture          | Registre compteur               |

| TCSR1                                          | 0x10        | 32 bits | Lecture/Ecriture | Registre de contrôle du         |

|                                                | 0.22.0      | 02 010  | Decidic/Lenture  | deuxième compteur.              |

| TLR1                                           | 0x14        | 32 bits | Lecture/Ecriture | Registre de chargement          |

| TCR1                                           | 0x18        | 32 bits | Lecture          | Registre du compteur            |

Tableau III.2. Registres du OPB Timer-Counter

Les registres TCSR0 et TCSR1 sont des registres de contrôle. Ils permettent la configuration du mode de fonctionnement du module ainsi que l'activation ou bien la désactivation des interruptions. Le registre TCR0 (respectivement TCR1) contient la valeur courante du premier (respectivement du deuxième) compteur du module. Les registres TLR1 et TLR0 permettent la définition de la période et du rapport cyclique du PWM tel que :

•Le registre TLR0 permet de spécifier la valeur de la période du PWM comme suit:

$$PERIOD_PWM = (TLR0 + 2) * OPB_CLK_PERIOD (1)$$

•Le rapport cyclique est calculé à partir de la valeur du registre TLR1 d'après le Datasheet [17] comme suit:

En sachant que le rapport cyclique est défini comme suit :

$$R = (PWM HIGH TIME / PERIOD PWM) * 100$$

En utilisant les équations (1) et (2) on obtient :

$$R = [(TLR1 + 2)/(TLR0 + 2)] * 100 (3)$$

Tel que (1 / OPB\_CLK\_PERIOD) représente la fréquence à laquelle fonctionne le système.

Si on veut obtenir un signal PWM avec une fréquence et un rapport cyclique donné, il suffit simplement de calculer les valeurs correspondantes de TLR0 et TLR1 en utilisant les équations (1) et (3). De l'équation (1) on obtient:

$$TLR0 = (PERIOD_PWM / OPB_CLK_PERIOD) - 2(4)$$

On sait que PERIOD\_PWM = 1/FREQ\_PWM et que OPB\_CLK\_PERIOD = 1/FREQ\_OPB et en les remplaçant dans l'équation (4) on obtient :

$$TLR0 = ((1/FREQ_PWM) * FREQ_OPB) - 2 (5)$$

De même, on utilise l'équation (3) pour calculer la valeur à mettre dans le registre TLR1 pour obtenir un rapport cyclique donné :

$$TLR1 = [(R/100)*(TLR0 + 2)] - 2 (6)$$

Par exemple si on veut obtenir un signal PWM avec une fréquence de 20 Hz et un rapport cyclique de 60% en sachant que la fréquence de fonctionnement du système est de 50 MHz, il suffit d'utiliser les équations (5) et (6) pour calculer les valeurs de TLR0 et TLR0 correspondantes :

TLR0 =

$$((1/20) * 50 * 10^6) - 2 = 2500 * 10^3 - 2 = 2499998$$

TLR1 =  $((60/100) * (2499998 + 2)) - 2 = 1499998$

Il faut noter que le mode PWM n'est pas pris en charge par les pilotes fournis avec l'outil EDK. Dans ce qui suit nous présentons les pilotes qui ont été développés afin de prendre en charge ce mode de fonctionnement.

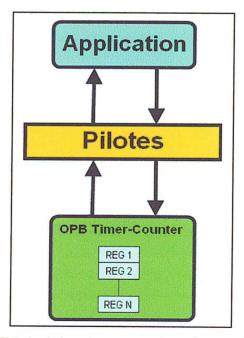

#### II.2.1. Développement des Pilotes pour le Mode PWM

Les pilotes représentent une interface entre l'application (software) et le matériel (Hardware), offrant la possibilité d'interaction entre ces deux derniers. Ils permettent un accès bas niveau aux registres internes du module soit en lecture soit en écriture (Figure III.8). L'accès à ces registres permet la gestion du mode interruption, l'activation ou la désactivation du module, ou bien le lancement d'une fonctionnalité donnée, etc.

Figure III.8. Accès bas niveau aux registres à travers les pilotes.

Les pilotes sont écrit en respectant le datasheet du module OPB Timer-Counter qui contient toutes les informations nécessaires à propos des registres existants ainsi que la signification de chaque bit de ces derniers. Par exemple, pour basculer vers le mode PWM il faut effectuer un certains nombre d'opérations sur les bits des registres TCSR0 et TCSR1 :

- •Mettre le bit 29 des registres TCSR0 et TCSR1 à '1';

- •Mettre le bit 31 des registres TCSR0 et TCSR1 à '0';

- •Enfin activer le PWM en mettant le bit 22 des registres TCSR0 et TCSR1 à '1'.

Le tableau III.3 présente les principaux pilotes qui ont été développés en C embarqué. Ces derniers permettent le passage au mode PWM ainsi que la spécification de la période et du rapport cyclique.

Tableau III.3. Pilotes permettant l'initialisation et l'utilisation du mode PWM.

| November 171.5. I notes permettant i intransation et i utilisation du mode i wivi. |                                                                                                                               |  |  |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Nom du Pilote                                                                      | Description                                                                                                                   |  |  |

| PWM_Set_TLR0 (TLR1)                                                                | Permet d'écrire une valeur dans le registre TLR0 (TLR1).                                                                      |  |  |

| PWM_Disable_MDT_TCSR0<br>(TCSR1)                                                   | Mettre le bit 31 du registre TCSR0 (TCSR1) à '0'. Cette fonction doit être exécutée avant l'activation du mode PWM.           |  |  |

| PWM_Enable_MDT_TCSR0<br>(TCSR1)                                                    | Mettre le bit 31 du registre TCSR0 (TCSR1) à '1'.                                                                             |  |  |

| PWM_Disable_PWM0_TCSR0<br>(TCSR1)                                                  | Mettre le bit 22 du registre TCSR0 (TCSR1) à '0'. Cette fonction désactive le mode PWM du module OPB Timer-Counter.           |  |  |

| PWM_Enable_PWM0_TCSR0<br>(TCSR1)                                                   | Mettre le bit 22 du registre TCSR0 (TCSR1) à '1'. Cette fonction active le mode PWM du module OPB Timer-Counter.              |  |  |

| PWM_Disable_GENT_TCSR0<br>(TCSR1)                                                  | Mettre le bit 29 du registre TCSR0 (TCSR1) à '0'.                                                                             |  |  |

| PWM_Enable_GENT_TCSR0<br>(TCSR1)                                                   | Mettre le bit 29 du registre TCSR0 (TCSR1) à '1'. Cette fonction doit être exécutée avant l'activation du mode PWM.           |  |  |

| PWM_Disable_ENALL_TCSR0 (TCSR1)                                                    | Mettre le bit 21 du registre TCSR0 (TCSR1) à '0'. Cette fonction permet d'activer les Timers du module OPB Timer-Counter.     |  |  |

| PWM_Enable_ENALL_TCSR0 (TCSR1)                                                     | Mettre le bit 21 du registre TCSR0 (TCSR1) à '1'. Cette fonction permet de désactiver les Timers du module OPB Timer-Counter. |  |  |

| PWM_Disable_INTR_TCSR0 (TCSR1)                                                     | Mettre le bit 25 du registre TCSR0 (TCSR1) à '0'. Cette fonction permet de désactiver les interruptions.                      |  |  |

| PWM_Enable_INTR_TCSR0<br>(TCSR1)                                                   | Mettre le bit 25 du registre TCSR0 (TCSR1) à '1'. Cette fonction d'activer l'effet des interruptions.                         |  |  |

| PWM_Clear_INTR_TCSR0 (TCSR1)                                                       | Mettre le bit 23 du registre TCSR0 (TCSR1) à '1'. Cette fonction permet de remettre à zéro le signal d'interruption.          |  |  |

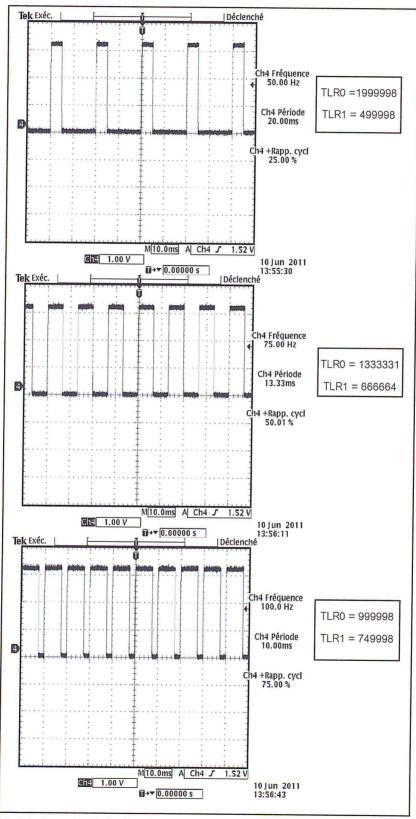

Pour le test du module OPB Timer-Counter en mode PWM, nous avons procédé de la même manière adoptée pour le test du OPB-CNA. La figure III.9 présente le résultat de génération de différents signaux PWM sur l'oscilloscope.

Figure III.9. Résultats de génération de signaux PWM avec différentes périodes et rapports cycliques.

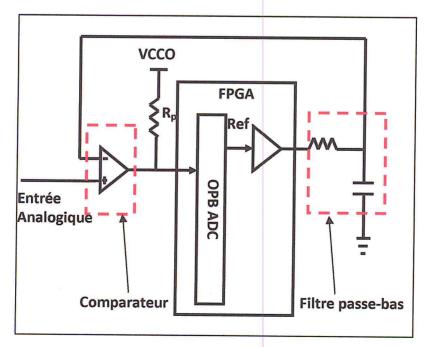

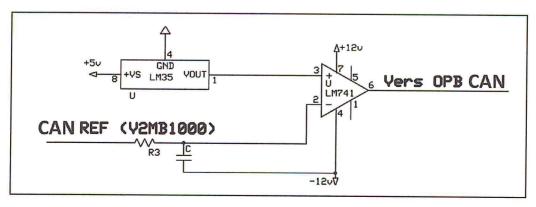

# III. Intégration de la Partie Acquisition

La partie d'acquisition (ou de mesure) fournit à la partie de contrôle les données issues d'un capteur permettant de mesurer l'état ou la situation du processus à contrôler. Cette fonction est réalisée par un Convertisseur Analogique/Numérique (CAN). Dans notre cas, la plateforme Memec V2MB1000 ne possède pas un circuit jouant le rôle d'un CAN. Néanmoins, une solution alternative consiste à réutiliser le module OPB Delta Sigma Analog-to-Digital [18]. Ce dernier est un module qui permet de réaliser la conversion Analogique/Numérique. Les principales spécifications de ce module sont :

- Compatible avec le Bus OPB 32 bits ;

- Fréquence de fonctionnement pouvant atteindre 100 Mhz ;

- •16 entrées pour le FIFO;

- Résolution paramétrable (8 où 10 bits).

Toutefois, ce module nécessite l'utilisation d'une certaine électronique externe à la plateforme V2MB1000 (Figure III.10). Ce dispositif électronique est constitué des composants suivants :

- •Un filtre passe-bas à la sortie du signal de référence;

- •Un comparateur qui a comme entrée le signal de référence et le signal analogique provenant du système à contrôler.

Figure III.10. Réalisation d'un CAN à l'aide d'un OPB-CAN.

Le module OPB-CAN convertit un niveau de tension en une valeur numérique non signée dont le minimum est 0 qui correspond à une tension de 0 volts et le maximum est  $2^n$ -1 qui correspond à une tension de 3.3 volts (tension maximum lue par la plateforme V2MB1000), tel que n représente la résolution du OPB-CAN. Le tableau III.4 présente les différents registres présents sur le module OPB-CAN :

| Registre                                 | Offset | Accès            | Description                                                            |

|------------------------------------------|--------|------------------|------------------------------------------------------------------------|

| Registre de Contrôle<br>(CR)             | 0x01C  | Lecture/Ecriture | Registre de contrôle du CAN.                                           |

| FIFO                                     | 0x104  | Lecture          | File d'attente FIFO pour les données converties.                       |

| Registre d'occupation du FIFO (OCCY)     | 0x108  | Lecture          | Nombre d'éléments dans le FIFO.                                        |

| Registre d'état du FIFO<br>(IPIPR 1 bit) | 0x020  | Lecture          | '1': Le FIFO contient des données; '0': Le FIFO est vide.              |

| Registre d'interruption<br>(IPIER 1 bit) | 0x028  | Lecture/Ecriture | '1': Interruption du FIFO activée; 0: Interruption du FIFO désactivée. |

Tableau III.4. Registres du OPB-CAN.

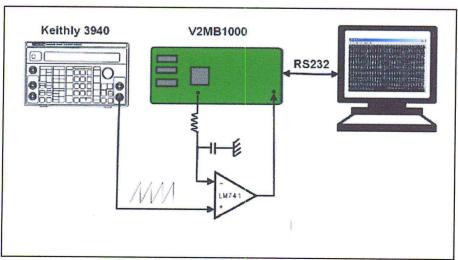

Pour le test de la partie d'acquisition nous avons utilisé un synthétiseur de signaux Keithly 3940 [19] dont la sortie est connectée à l'amplificateur opérationnel LM741 [20] jouant le rôle de comparateur. L'autre entrée du comparateur est connectée au signal de référence provenant de la plateforme V2MB1000. Le synthétiseur de signaux est utilisé pour générer un signal analogique en dents de scie. Les valeurs lues par le module d'acquisition sont envoyées à travers le RS232 et affichées sur le PC par logiciel Tera Term Pro. La figure III.11 représente le schéma synoptique du montage réalisé pour le test.

Figure III.11. Schéma synoptique du montage de test du OPB-CAN.

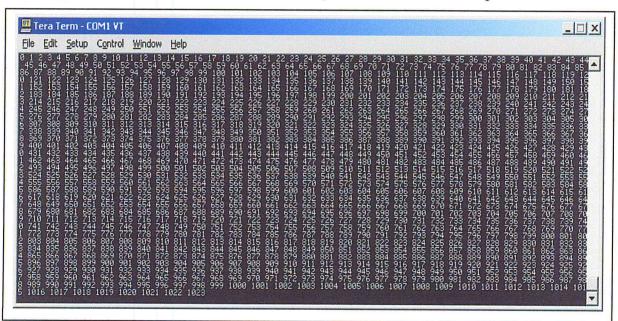

L'amplitude du signal analogique généré par le synthétiseur de signaux a été réglée pour quelle soit comprise dans l'intervalle [0 volts, 3.3 volts]. Ce dernier représente la plage des valeurs de tensions pouvant être lues par la plateforme V2MB1000. Nous avons configuré notre OPB-CAN pour une résolution de 10 bits, donc les valeurs lues seront comprises entre 0 et 1023 (2<sup>10</sup>-1). Tel que 0 correspond à une tension d'entrée de 0 volts et 1023 correspond à la tension maximale de 3.3 volts. Le signal en dents de scie varie linéairement dans le temps entre les valeurs 0 volt et 3.3 volt, donc le résultat sur le PC doit correspondre à un affichage des valeurs en ordre croissant entre 0 et 1023. La figure III.12 représente le résultat du test affiché par le logiciel Tera Term Pro, qui valide le bon fonctionnement de la partie d'acquisition.

Le synthétiseur de signaux qui a permis de générer le signal analogique sera remplacé par la suite par un capteur dont la sortie sera connectée à l'entrée du dispositif d'acquisition. Ce capteur permettra au système de contrôle embarqué de connaître l'état du processus.

Figure III.12. Résultat du test du OPB-CAN sur PC.

# IV. Intégration de la Partie de Contrôle

Cette partie représente le cœur du système de contrôle (ou de régulation) embarqué. En effet, elle permet de calculer la commande (qui sera appliquée par la partie de commande) permettant de modifier l'état du processus à contrôler. Ce calcul tient compte des données issues de la partie d'acquisition et de la consigne imposée par l'utilisateur du système. La partie de contrôle a été développée sous forme d'un module hardware (IP: Intellectual Property) écrit en langage HDL, et ensuite a été intégrée dans notre système. Dans ce qui suit

nous allons résumer les étapes de développement et de test qui ont permis d'abord la vérification fonctionnelle et par la suite l'intégration de cette partie.

## IV.1. Développement et Test Fonctionnel

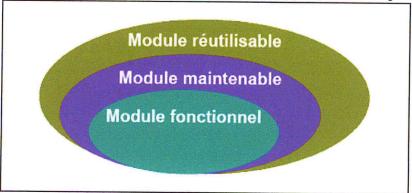

#### IV.1.1. Notion d'IP et Méthodologie de Conception

La partie de contrôle a été réalisée en utilisant la méthodologie de développement d'IP (Propriété Intellectuelle) [21] qui garantit un certain niveau de qualité avant le déploiement final du produit. Un IP est un module équipé de capacités de réutilisation (IP = module + capacité de réutilisation) qui peut être acheté, re-exploité et ajusté pour une application particulière. En plus d'être réutilisable, un module doit être :

- Configurable : le module est conçu pour résoudre un problème général ;

- Portable : le module est conçu indépendamment de la technologie ;

- •Lisible : le module doit être bien documenté sur la gamme d'applications, interfaces, contraintes,... ;

- Debuguable : le module doit être vérifié avec un degré élevé de confiance.

Ces propriétés nous permettent donc de classifier les IPs par leur niveau de qualité comme suit (voir aussi Figure III.13):

- •Fonctionnel : représente le niveau minimum qu'un module doit atteindre pour pouvoir être déployé ;

- Maintenable : par rapport au niveau fonctionnel, un bloc maintenable serait aussi fonctionnel, mais également bien documenté (schémas, codage propre et clair, codes commentés, spécifications, sommaires, ...);

- Réutilisable : ce niveau est un enrichissement par rapport au niveau précédent.

Figure III.13. Niveaux de qualité d'un IP.

Le passage d'un niveau à un autre peut se faire mais en faisant un effort supplémentaire de conception.

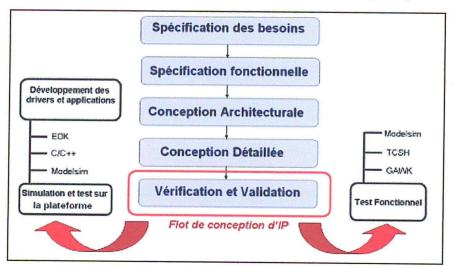

Pour garantir toutes ces propriétés, la méthodologie de développement d'IPs doit suivre un chemin bien tracé depuis la spécification des besoins jusqu'au test de validation final dans un environnement réel. La figure III.14 représente le flot de conception d'un IP qui passe par les étapes suivantes :

- Spécification des besoins : cette étape permet d'élaborer un cahier des charges après avoir effectué une étude du marché sur les produits commerciaux déjà existants ;

- Spécification fonctionnelle : cette étape permet de spécifier ce que l'IP doit faire et pas comment le faire. Elle ne contient pas les détails d'implémentations mais une description exacte sur les futurs caractéristiques de l'IP;

- •Conception architecturale : dans cette étape l'IP est décrit sous forme de blocs et d'interconnexions entre ces derniers. Les détails d'implémentation de chaque bloc sont omis dans cette étape ;

- Conception détaillée : dans cette étape on s'intéresse aux détails d'implémentation de chaque bloc établi dans l'étape précédente ;

- Vérification et validation : dans cette étape deux genres de test sont effectués :

- Test fonctionnel : ce test permet de vérifier d'abord le fonctionnement de chaque bloc, ensuite de l'IP complet par la suite [22];

- Test au niveau système : ce test permet de valider le fonctionnement de l'IP dans un système embarqué (Processeur + Bus + Périphériques).

Figure III.14. Flot de conception d'IPs.

Dans notre cas nous nous intéressons à la dernière étape qui consiste à intégrer l'IP dans un système embarqué, d'écrire les différents pilotes permettant l'utilisation du module et enfin de procéder aux différents tests de vérification de validation dans un environnement réel sur la plateforme MEMEC V2MB1000.

Il faut noter que l'IP jouant le rôle de la partie de contrôle a été déjà développé et a subi une vérification fonctionnelle conjointement sur Modelsim et dans l'environnement Simulink sur Matlab [23]. Avant d'aborder l'intégration de l'IP de contrôle, nous allons d'abord présenter une brève description de l'architecture interne de ce dernier ainsi que le test fonctionnel sur Simulink et Modelsim.

#### IV.1.2. Description et Test Fonctionnel

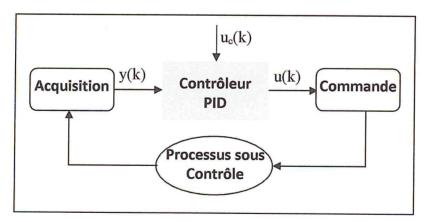

La fonctionnalité de contrôle ou bien de régulation est réalisée par un PID. Ce dernier représente le moyen de contrôle en boucle fermée le plus utilisé dans l'industrie grâce à sa simplicité et à sa robustesse. La figure III.15 représente un système en boucle fermée typique utilisant un contrôleur PID où y(k), uc(k) et u(k) représentent respectivement la donnée issue du capteur, la consigne de l'utilisateur et la commande calculée par le PID au kème instant d'échantillonnage.

Figure III.15. Système de contrôle en boucle fermée utilisant un PID.

La commande calculée par le PID qui doit être appliquée sur le processus à contrôler est définie comme suit [11]:

$$u(k) = P(k) + I(k) + D(k)$$

Tels que:

$$P(k) = A \cdot u_c(k) + B \cdot y(k), I(k) = I(k-1) + C \cdot e(k-1) \text{ et } D(k) = D \cdot D(k-1) + E \cdot f(k)$$

P représente l'action proportionnelle, I l'action intégrale et D l'action dérivé à un instant K.

Avec:

$$e(k-1) = u_c(k-1) - y(k-1)$$

et  $f(k) = y(k) - y(k-1)$ .

Tel que *e* représente l'erreur entre la consigne spécifiée par l'utilisateur (u<sub>c</sub>) et l'état actuel du processus à contrôler (y) à un instant k. Le tableau III.5 présente les équations permettant le calcul des coefficients A, B, C et D.

| Co | effreients                       |

|----|----------------------------------|

| A  | $K_p b$                          |

| В  | $-K_{p}$                         |

| С  | $K_p \frac{T_s}{T_i}$            |

| D  | $\frac{T_d}{T_d + NT_s}$         |

| Е  | $-\frac{K_p T_d N}{T_d + N T_s}$ |

Tableau III.5. Equations de calcul des coefficients.

Tels que  $K_p$  représente le gain proportionnel ;  $T_i$  et  $T_d$  sont respectivement les temps du dérivé et celui de l'intégral ; N est la valeur maximale du gain dérivé ; b permet de limiter l'effet de l'action proportionnel et  $T_s$  est le temps d'échantillonnage dans lequel l'état du processus à contrôler est transféré à la partie de contrôle.

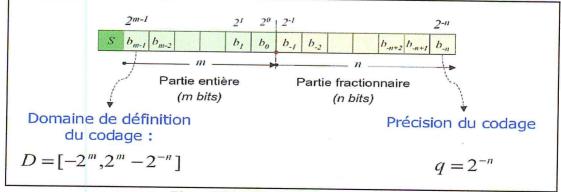

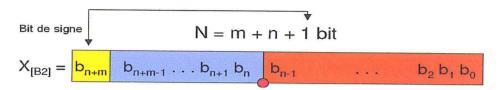

La représentation de la commande, de la mesure et de la consigne au niveau de l'IP PID est en virgule fixe. Cette représentation permet d'une part d'économiser les ressources utilisées au niveau du FPGA mais aussi de réduire la consommation de puissance de ce dernier. Le codage d'un nombre réel en virgule fixe est présenté par la figure III.16. Un nombre codé en virgule fixe est composé d'une partie entière, d'une partie fractionnaire et d'un bit de signe. En augmentant la taille de la partie fractionnaire on augmente par la même occasion la précision du calcul.

Figure III.16. Représentation en virgule fixe.

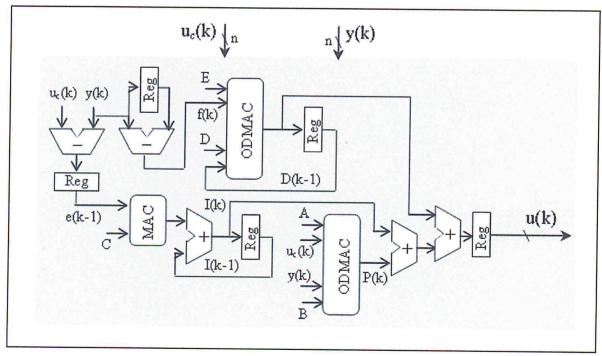

Dans ce qui suit nous donnons à titre d'informations les détails d'implémentation de l'IP PID. Une implémentation intuitive et parallèle du PID requiert en total 7 additionneurs/soustracteurs et 5 modules de multiplication. Dans la conception digitale le nombre total de portes logiques utilisées est linéairement lié à la taille du mot pour un additionneur et quadratiquement pour un multiplieur. Cette façon de faire accroit considérablement le nombre de ressources utilisées sur le FPGA, augmentant ainsi la consommation de puissance. Il est donc clair que l'effort d'optimisation de la consommation de puissance doit être concentré sur l'implémentation sérielle de la fonction MAC (Multiply And Accumulate X×Y) [24]. Une variante optimisée de cette dernière qui permet de calculer X×Y+T×Z (ODMAC : Optimized Double Multiply And Accumulate) a été implémentée de telle façon à optimiser le nombre de ressources utilisées et la consommation de puissance. Ces deux fonctions sont basées sur l'algorithme de multiplication RMRMA (Recursive Multibit Recording Multiplication Algorithm) [25] qui est une amélioration de l'algorithme de multiplication de Booth (BMA) [26] et de l'algorithme de multiplication de Booth modifié (MBMA) [27]. La figure III.17 représente l'architecture de l'IP PID.

Figure III.17. Architecture de l'IP PID.

Les entrées de l'IP sont la consigne imposée par l'utilisateur du système  $(u_c(k))$  et la mesure représentant l'état de ce dernier à un instant k (y(k)). La sortie du module n'est que la commande (u(k)) à appliquer sur le processus à contrôler. Les coefficients A, B, C, D et E qui servent à paramétrer l'IP PID sont implémentés sous forme de registres dont les valeurs sont calculées en utilisant les équations du tableau II.5 et les paramètres  $K_p$ ,  $T_i$ ,  $T_d$ ,  $T_s$ , N et b.

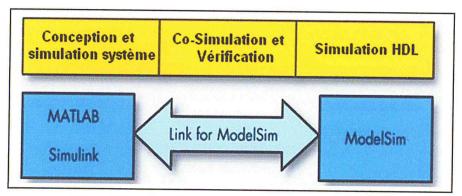

L'étape suivante (test et vérification fonctionnelle) consiste à vérifier le bon fonctionnement de notre IP PID. Cela permet dans un premier temps de valider l'IP avant de procéder à son intégration au sein d'un système embarqué et finalement de le tester dans un environnement réel. Pour ce faire, l'IP PID a été intégré dans Simulink sous forme d'un Bloc HDL dont les entrées sont stimulées par des vecteurs de test. Ces derniers sont générés par Simulink et transmis à l'outil Modelsim qui effectue la simulation HDL, qui a comme résultat la commande calculée par l'IP PID qui représente la sortie de ce dernier. Le transfert de données entre les deux outils Simulink et Modelsim se fait d'une manière transparente avec l'outil LINK FOR MODELSIM. Cette façon de faire est appelée Co-Simulation HDL (voir figure III.18).

Figure III.18. Interface de Co-Simulation Simulink/ModelSim.

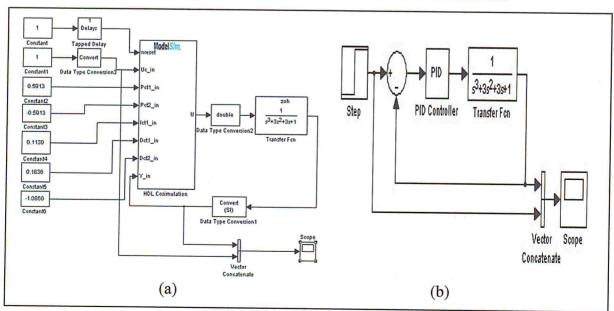

Afin de tester le bon fonctionnement de notre IP PID, deux environnements virtuels ont été mis en place. Le premier possède comme module de contrôle notre IP PID et le second un Bloc PID idéal (se trouve au sein de la bibliothèque de Simulink) qui servira comme référence pour notre PID. La figure III.19 représente les environnements crées sous Simulink.

Figure III.19. Environnements de Test Simulink (a) IP PID (b) PID idéal.

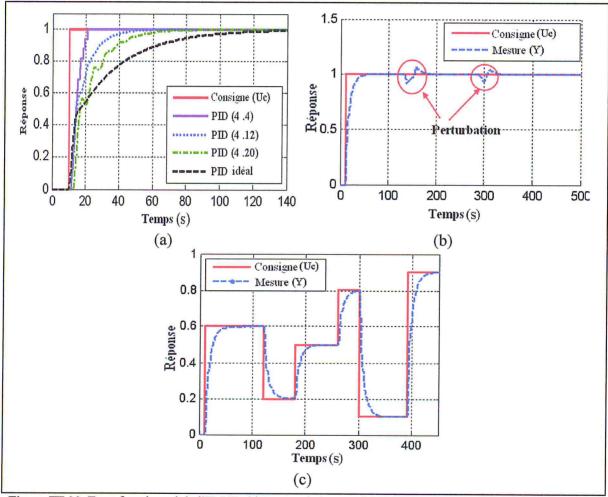

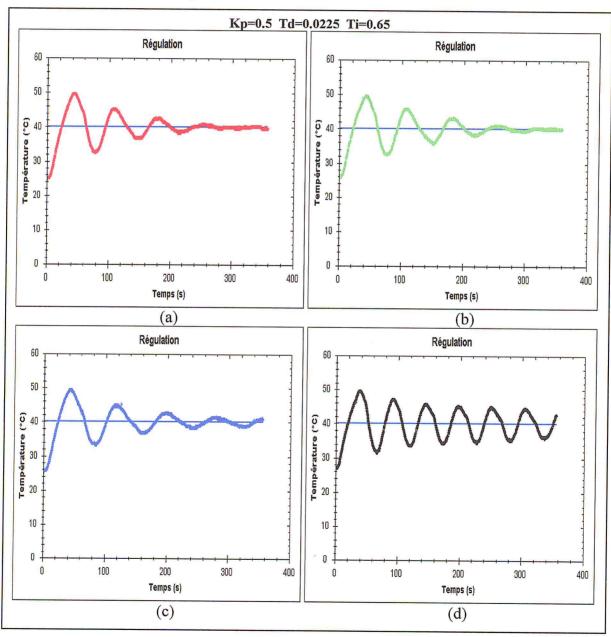

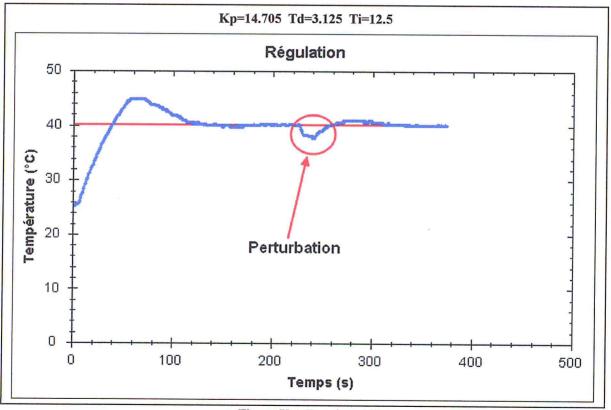

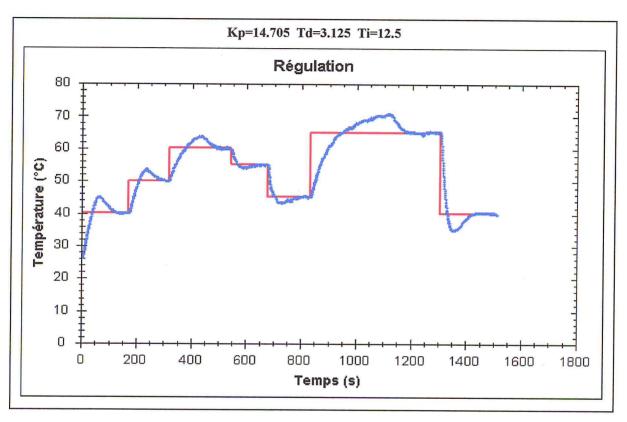

Le processus à contrôler est représenté sous forme d'une fonction de transfert [28] qui permet de modéliser son comportement et dont la sortie représente son état qui sera affiché avec la consigne (sur la courbe des résultats) et injecté au module de contrôle (PID idéal et IP PID) pour le calcul de la prochaine commande. Nous avons ensuite procédé à plusieurs types de tests pour valider le fonctionnement de l'IP PID. Le premier test consiste à vérifier l'impact de la taille de la partie fractionnaire sur la qualité de la régulation par rapport à celle effectuée par le PID idéal. Le deuxième test consiste à vérifier la stabilité de l'IP PID face à des perturbations externes (test de stabilité). Le dernier test permet de vérifier la capacité de l'IP PID à suivre une consigne variable dans le temps (test de poursuite). La figure III.20 présente les résultats obtenus des différents tests cités ci-dessus.

Figure III.20. Tests fonctionnel de l'IP PID (a) Impact de la précision (b) Test de stabilité (c) Test de poursuite.

On remarque d'après la figure III.20.a que plus on augmente la taille de la partie factionnaire plus la précision du calcul augmente et plus le résultat se rapproche de celui du PID idéal. Pour le test de stabilité qui consiste à exercer des séries de perturbations, on remarque que l'IP PID permet à l'état du processus de se stabiliser sur la valeur de la consigne après un certain temps.

Enfin pour le test de poursuite, on remarque d'après la figure III.20.c, que l'IP PID est capable de poursuivre une consigne avec amplitude et durée variables dans le temps. Dans la section suivante, nous allons présenter les étapes d'intégration de notre IP PID dans le système de contrôle ainsi que les pilotes qui ont été développés pour utiliser et accéder ce dernier.

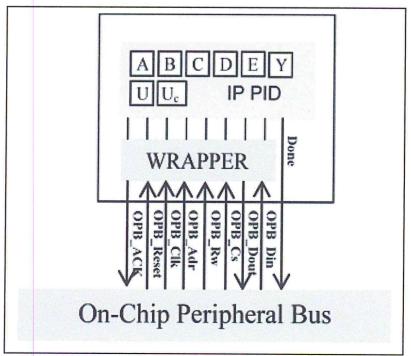

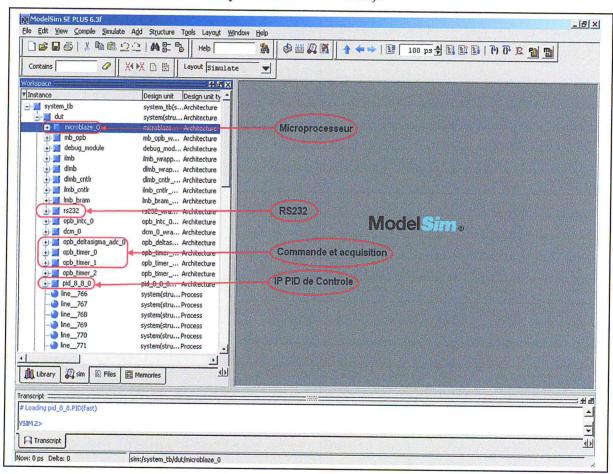

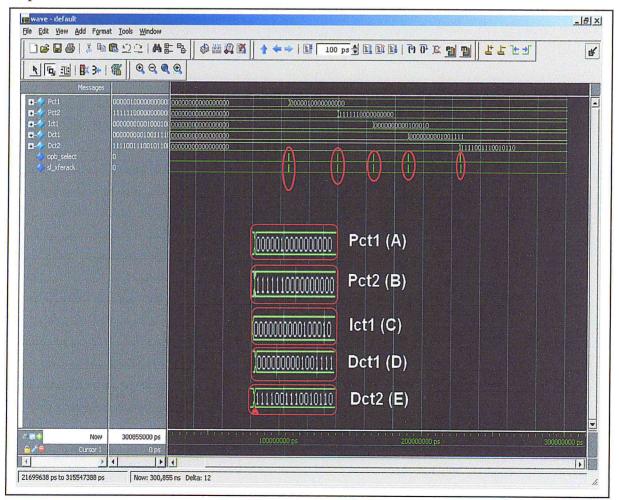

## IV.2. Intégration et Développement des Pilotes