32-530-376-1 الجمهورية الجزائرية الديمقراطية الشعبية REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE TS4/2019 وزارة التعليم العالى و البحث العلمي MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET LA RECHERCHE SCIENTIFIQUE UNIVERSITE FERHAT ABBAS - SETIF-Institut d'Electronique THESE En Vue d'Obtention du Diplôme de Magister En Electronique Option: Micro-Electronique THEME

Modélisation et Simulation en Régimes Statique et Dynamique du Transistor IGBT

(Insulated - Gate - Bipolar - Transistor)

Soutenue le : 30/06/ 1996

Par: Ing. BENBAHOUCHE LYNDA

Membres du jury :

Président : Dr A. MERZOUQUI (M.C)

Promoteur : Dr K. DJELLABI (C.C)

Examinateurs : Dr F. KRIM (C.C)

Dr E. BOUSBIAT (M.C)

Dr L. SELMANI (C.C)

Promotion 1996

الجمهورية الجزائرية الديمقراطية الشعبية

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعليم العالي و البحث العلمي MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET LA RECHERCHE SCIENTIFIQUE

> UNIVERSITE FERHAT ABBAS - SETIF-Institut d'Electronique

## THESE

En Vue d'Obtention du Diplôme de Magister En Electronique Option : Micro-Electronique

#### THEME

Modélisation et Simulation en Régimes Statique et Dynamique du Transistor IGBT

(Insulated - Gate - Bipolar - Transistor)

Soutenue le: / / 1996

Par: Ing. BENBAHOUCHE LYNDA

Membres du jury:

Président : Dr A. MERZOUGUI (M.C)

Promoteur : Dr K. DJELLABI (C.C)

Examinateurs : Dr F. KRIM (C.C)

Dr E. BOUSBIAT (M.C)

Dr L. SELMANI (C.C)

Promotion 1996

#### REMERCIEMENTS

Je remercie Dieu de nous avoir ouvert les yeux à cette lumière et répond sa clarté tout autour de nous.

Je remercie Mr A. MERZOUGUI, maître de conférence à l'institut d'électronique de SETIF, pour l'intérêt qu'il a porté à mon travail et pour l'honneur qu'il m'a fait en présidant le jury de cette thèse.

Je tiens à remercier, tout particulièrement, Mr K.DJELLABI chargé de cours à l'institut de mécanique de précision de SETIF, ainsi que Mr K.BENBAOUCHE, chargé de cours à l'institut d'électronique de SETIF, pour la confiance qu'ils ont manifestée à mon égard en me proposant ce sujet de thèse, pour m'avoir initiée à la recherche et pour m'avoir fait découvrir le monde de la simulation.

Je suis également très sensible à l'intérêt que Mr E.BOUSBIAT, maître de conférence à l'institut d'électronique d'Alger (KOBA), Mr F.KRIM chargé de cours à l'université de SETIF, Mr L.SELMANI, chargé de cours à l'université de SETIF, ont accordé à mon travail en acceptant de se porter juges de celui-ci.

## LISTES DES SYMBOLES

| A                          | Device active area (cm <sup>2</sup> ).                    |

|----------------------------|-----------------------------------------------------------|

| $I_n, I_p$                 | Electron, hole current (A).                               |

| n, p                       | Electron, hole carrier concentration (cm <sup>-3</sup> ). |

| $\delta_{\mathfrak{p}}$    | Excess carrier concentration (cm <sup>-3</sup> ).         |

| Q                          | Total excess carrier base charge (C).                     |

| $\phi_n$ , $\phi_p$        | Electron, hole quasi-fermi potential (V).                 |

| E                          | Electric field (V/cm).                                    |

| $\epsilon_{s}$             | Dielectric constant of silicon (F/cm).                    |

| q                          | Electronic charge (1.6 x 10 <sup>-19</sup> C).            |

| $\mu_n$ , $\mu_p$          | Electron, hole mobility (cm <sup>2</sup> /Vs).            |

| $D_n$ , $D_p$              | Electron, hole diffusivity (cm²/s).                       |

| $	au_{ m HL}$              | High level excess carrier lifetime (s).                   |

| $I_{T} = I_{n} + I_{p}$    | Total current (A).                                        |

| $b = \mu_n / \mu_p$        | Ambipolar mobility ratio.                                 |

| $D = 2(D_n.D_p/D_n+D_p)$   | Ambipolar diffusivity (cm <sup>2</sup> /s).               |

| $L = \sqrt{D.\tau_{HL}}$   | Ambipolar diffusion length (cm).                          |

| X                          | Distance in base from emitter (cm).                       |

| $W_{\scriptscriptstyle B}$ | Metallurgical base width (cm).                            |

| W                          | Quasi-neutral base width (cm).                            |

| $W_{bcj}$                  | Base - collecteur depletion width (cm).                   |

| C                          | Base - collecteur depletion capacitance (F).              |

|                            |                                                           |

N<sub>B</sub> Base doping concentratrion (cm<sup>-3</sup>).

$V_{bi}$  Built - in potential of base - collecteur juction(V).

$V_{bc}$  Applied base - collecteur potential (V).

$I_{snc}$  Emitter electron saturation current (A).

$V_{eb}$  Applied base - emitter potential (V).

V<sub>A</sub> Device anode voltage (V).

$R_s$  Device series resistance  $(\Omega)$ .

R Series load resistance  $(\Omega)$ .

LL Series load inductance (H).

$V_{AA}$  Supply voltage (V).

$K_{\rm p}$  MOSFET channel transconductance (A/V<sup>2</sup>).

$V_{T}$  MOSFET channel threshold voltage (V).

| CHAPITRE II: MODELISATION DU TRANSISTOR IGBT DANS LE<br>LOGICIEL ESACAP29 |

|---------------------------------------------------------------------------|

| II-Introduction30                                                         |

| II-1: Le logiciel ESACAP                                                  |

| II-1-1: Présentation30                                                    |

| II-1-2 : Les modèles dans ESACAP31                                        |

| II-1-2-1 : Le modèle\du transistor MOS                                    |

| A) Les équations du courant de drain Id dans ESACAP                       |

| II-1-2-2 : Le modèle de la diode34                                        |

| A) Présentation                                                           |

| II-2 : Modélisation de la capacité Cgd dans ESACAP35                      |

| I-2-1: Le modèle à initialisation36                                       |

| II-3 : Synthèse de la modélisation du transistor V.DMOS                   |

| de puissance en commutation dans l'ESACAP38                               |

| II-4: Mollélisation du transistor bipolaire39                             |

| II 4.1 · Présentation                                                     |

| II-4-2: Le modèle statique EBERS-MOLL40                    |

|------------------------------------------------------------|

| II-4-2-1: Modèle statique et son implantation dans         |

| l'ESACAP40                                                 |

| A) Formulation des équations41                             |

| B) Implantation dans l'ESACAP41                            |

| C) Modèle statique: effet du second ordre                  |

| et son implantation43                                      |

|                                                            |

| II-5 : Synthèse de la modélisation du transistor bipolaire |

| dans l'ESACAP43                                            |

| II-5-1: Modèle d'EBERS-MOLL43                              |

| II-5-2: Modèle de GUMMEL-POON44                            |

| II-6 : Modèle du transistor IGBT45                         |

| II-6-1 : Comportement statique de l'IGBT dans              |

| 1' ESACAP                                                  |

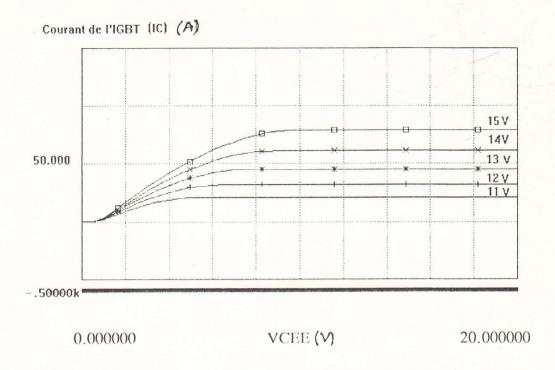

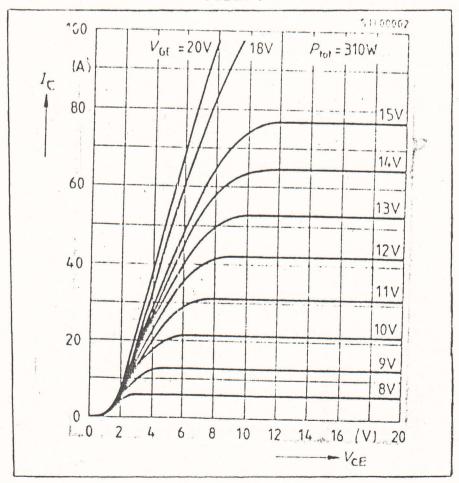

| II-6-1-a : Caractéristique de sortie                       |

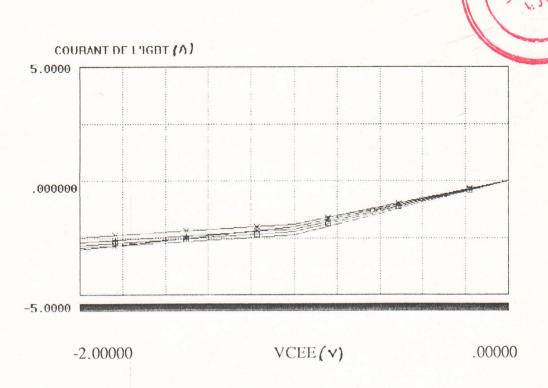

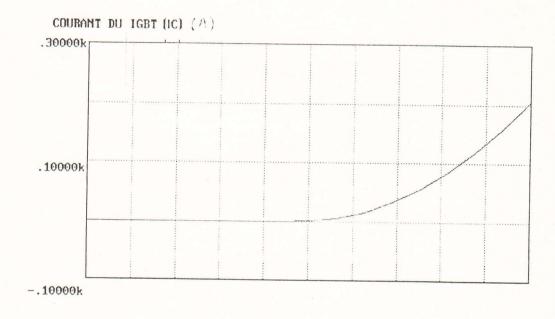

| II-6-1-b : Caractéristique à l'état "on"47                 |

| II-7: Le comportement en commutation48                     |

| II-7-1 : Etat "on"48                                       |

| II-7-2: Etat "off"50                                       |

| II-8 : Conclusion52                                        |

| CHAPITRE III: VALIDATION DES MODELES53                                      |

|-----------------------------------------------------------------------------|

| III-1 Introduction54                                                        |

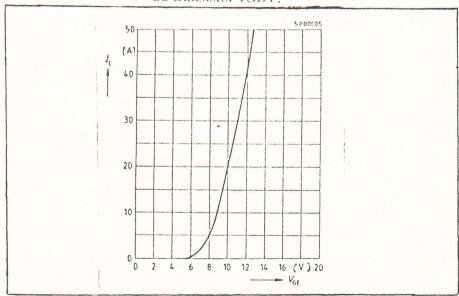

| III-2 : Détermination des paramètres statiques54                            |

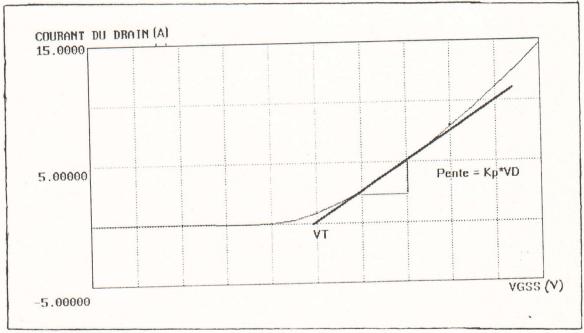

| III-2-1 : Détermination de Kp, et Vt54                                      |

| III-2-2: Détermination de Re, Rg et VAI.s55                                 |

| III-3 : Caractéristiques statiques de l'IGBT56                              |

| III-4 : Application à l'étude en Commutation60                              |

| III-4-1: Généralités60                                                      |

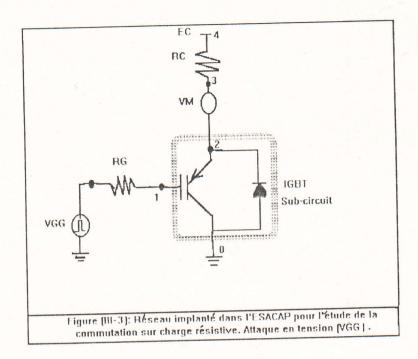

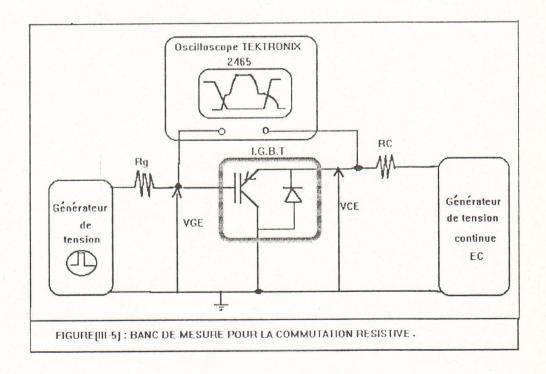

| III-4-2: Commutation sur charge résistive60                                 |

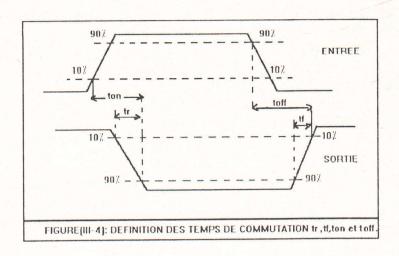

| III-4-2-1: Définition des temps de commutation61                            |

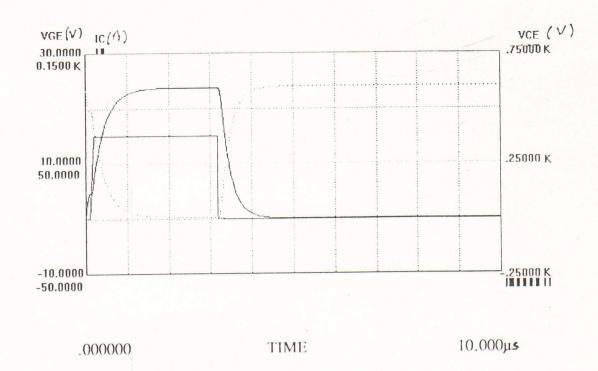

| III-4-2-2: Mesures et simulation                                            |

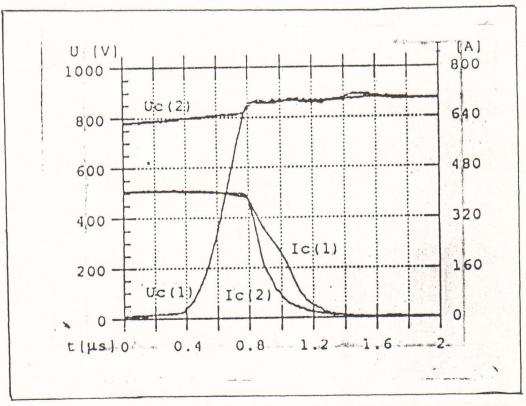

| III-4-3: Commutation sur charge inductive63                                 |

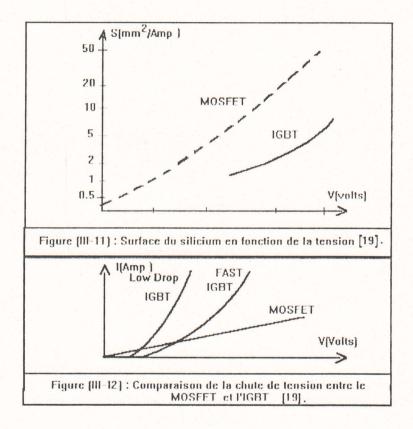

| III-5: Situation de l'IGBT par rapport dux autres composants de puissance69 |

| III-6 : Caractéristiques71                                                  |

| III-7 : Conclusion73                                                        |

| CONCLUSION GENERALE74                                                       |

| BIBLIOGRAPHIE78                                                             |

| ANNEXE.                                                                     |

INTRODUCTION GENERALE

#### INTRODUCTION GENERALE:

L'impact de l'évolution de la technologie de haute puissance (SMART POWER) sur les systèmes électroniques a été étudié [8]. Une fois que la définition de la technologie de haute puissance est fournie, la clé du développement technologique des composants semi-conducteurs de puissance, à savoir le Mosfet de puissance et l'IGBT sont étudiés.

La technologie de haute puissance exige la combinaison de la technologie des composants de puissance avec la logique CMOS et les circuits analogiques bipolaires.

Depuis l'invention du transistor bipolaire, il y'a eu une grande motivation d'augmenter le contrôle de la puissance (handling capability) de ces composants discrets dont le but d'élargir leurs applications et leur champ d'utilisation.

L'interrupteur de puissance IGBT est né en 1982 et à suscité un grand intérêt dans le monde de l'électronique de puissance. Situé entre le transistor MOS et le transistor bipolaire, il occupe le vide laissé par ces composants en utilisant les avantages de chacune de ces technologie, à savoir:

- côté MOS, une facilité de commande et une dynamique rapide,

- côté bipolaire, un bon état passant pour des interrupteurs de tension moyenne.

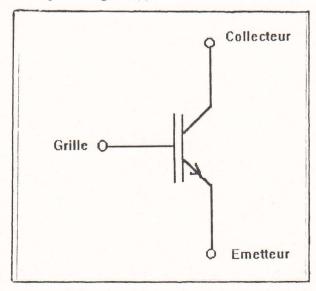

L'I.G.B.T. est un semiconducteur de puissance de type composant à trois broches. Deux broches reliées au circuit de puissance, la troisième au dispositif de commande. Les deux connexions de puissance sont appelées collecteur(ou drain) et émetteur (ou source), l'électrode de contrôle grille G. Son symbole est donné par la figure (1).

Figure I : Symbole de l'I.G.B.T.

Ainsi depuis quelques années et avec l'événement des technologies des transistors de puissance, les composants IGBT (Insulated-Gate-Bipolar-Transistor) ont vu leur champ d'utilisation s'élargir pour englober de nouveaux domaines tels que par exemple, la "conversion et le contrôle de l'énergie", "ajustage des vitesses des moteurs", " assure le contrôle robotique / numérique", ainsi que dans les dispositifs de contrôle.

Bien que le Mosfet de puissance est mieux adapté aux applications où les tensions de blocage sont relativement faibles (inférieur à 200V), sa résistance "on" augmente rapidement avec l'augmentation des tensions de blocage. De ce phénomène, il n'a pas été possible d'économiser la fabrication de haute tension du Mosfet de puissance avec un taux de courant élevé. L'une des solutions à ce problème est l'invention de "Insulated Gate Bipolar Transistor" (IGBT). Il a été toujours appelé " conductivity modulated field-effet transistor" COMFET [1]. A cause de sa caractéristique signifiante pour les applications de basses et moyennes fréquences, lorsqu'il est comparé avec le transistor bipolaire et le Mosfet de puissance, une partie substantielle de notre travail, est prise en compte pour obtenir une bonne compréhension de sa caractéristique d'opération.

Ces composants IGBT ont le même avantage que les Mosfet de puissance qui est la grande impédance d'entrée et peuvent opérer à une densité de courant dans l'ordre de magnitude supérieure que celle des Mosfet de puissance.

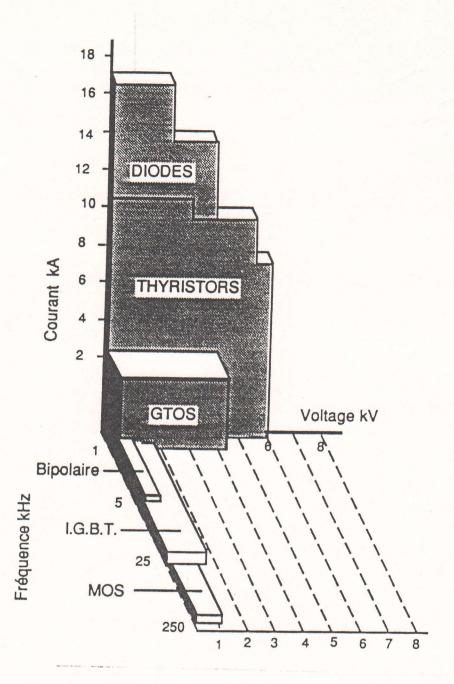

La représentation graphique de la figure(2) permet de situer l'I.G.B.T. parmi les autres composants de l'électronique de puissance. De nombreuses études mettent en avant un espace privilégié de fonctionnement de cet interrupteur qui se situe:

- Dans une gamme de fréquence moyenne f = quelques 10KHz,

- pour des calibres tension  $400V \le U \le 1200V$ ,

- pour des calibres courant  $10A \le I \le 600A$ .

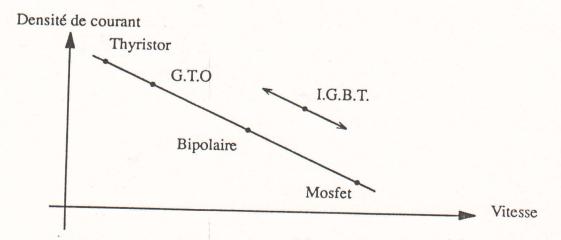

Ce composant oscille entre les deux types de technologie MOS et bipolaire (figure (3)).

Figure(2): Situation de 1.I.G.B.T. [25]

Figure(3): L'I.G.B.T. un compromis entre les structures "MOS" et "bipolaire".[25]

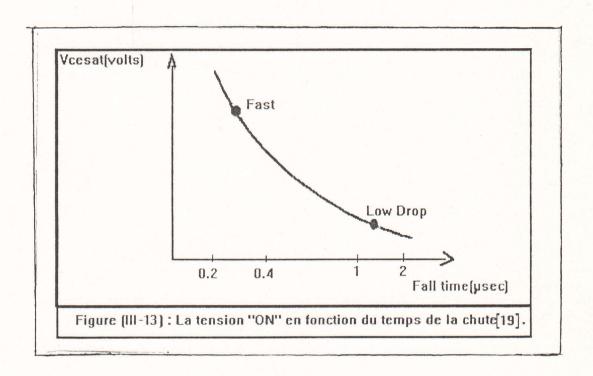

Les fabricants proposent des gammes diversifiées de transistor I.G.B.T. et créent des classes dites lentes, faible saturation ou de première génération, et des classes dites rapides ou de la seconde génération. On favorise soit la structure bipolaire et donc l'état passant du composant, soit la structure MOS et donc les caractéristiques dynamiques de l'interrupteur.

Bien que le transport du courant de l'IGBT se produit sous les conditions de haut niveau d'injection, leur vitesse de commutation est limitée par la recombinaison des porteurs minoritaires.

Leurs temps de "turn off" est de 0.1 à 10µs. Cela leur permet d'être adapter aux applications à fréquence moyennes où les tensions de blocage dépassent les 200V [1].

Ainsi il est apparu que la combinaison du courant de conduction du transistor bipolaire avec le courant contrôlé du Mosfet de puissance présente un avantage idéal : i) densités de courant élevées en direct (" high - operating forward current density ") et, ii) une faible puissance de l'électrode de contrôle grille G.

L'une des approches pour combiner ces avantages est d'utiliser le transistor bipolaire discret et le Mosfet de puissance l'un connecté à l'autre dans une configuration Darlington.

En plus, il a été établi théoriquement et expérimentalement que l'IGBT à canal p a des performances comparables à ceux à canal n, ainsi autorisant l'utilisation des composants complémentaires dans les systèmes de puissance.

Souvent le développement des circuits de contrôle intégrés présente un élan pour incorporer des circuits de protection sur des microcircuits de contrôle contre: la surtension, surintensité et sous des conditions de haute température. En addition, le besoin d'interface de ces composants IGBT avec un microprocesseur mène ou conduit à l'incorporation des circuits logiques.

La disponibilité du Mosfet de puissance et l'IGBT avec leurs caractéristiques du voltage contrôlé résulte d'une simplification énorme dans le circuit de contrôle. Cela a créer l'opportunité pour les développements des circuits du driver grille intégré, avec l'utilisation du développement récent de la technologie de haute tension des circuits intégrés.

Cela permet une grande réduction du coût, une augmentation signifiante de la fiabilité et une amélioration des performances dans les systèmes combinés.

Certes, le développement informatique a permis la réalisation de logiciels, i) de conception des composants de puissance (exp: MOS et transistor bipolaire) au niveau technologique de la puce et ii) de compréhension de mécanismes physiques réagissant les propriétés fonctionnelles de chaque zone de ces composants.

Mais les logiciels qui permettraient de manière suffisamment précise; i) de concevoir; ii) de simuler des circuits comprenant par exemple le MOS de puissance, transistor bipolaire de puissance; iii) de déterminer les contraintes internes et externes, courants et tensions à l'entrée et à la sortie de ces transistors sont inexistantes. Seule la possibilité de simuler ces transistors MOS et le bipolaire de faibles calibres en tension et en courant, par leur modèles " petits signaux " est envisageable: c'est par exemple, le cas du logiciel ESACAP.

Le but de ce mémoire est de présenter une modélisation du transistor IGBT (Insulated Gate Bipolar Transistor) de puissance allant du plus complet (valable en tout régime de fonctionnement) au plus simple (pour l'étude en commutation) qui sera implantée dans le logiciel ESACAP.

Notre étude portera principalement sur une modélisation du transistor IGBT utilisable pour traiter des régimes de commutation. Ce sera un outil d'aide à la conception des circuits de l'électronique de puissance.

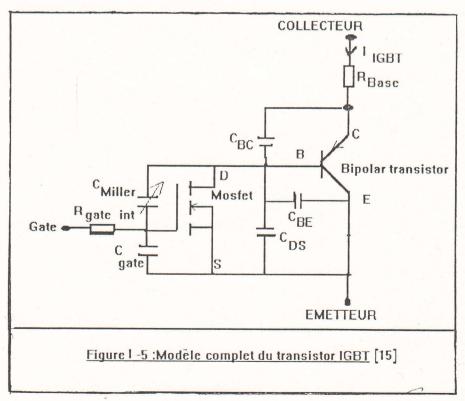

Nous réimplantons :i) un modèle du transistor VDMOS de puissance, ii) un modèle du transistor bipolaire et ainsi la combinaison de ces deux transistors en montage Darlington qui constituera le modèle complet de notre composant IGBT.

Le mémoire s'articule de la façon suivante:

Au premier chapitre, nous présenterons la "modélisation mathématique" du transistor IGBT afin d'établir un schéma équivalent dynamique, physique et complet.

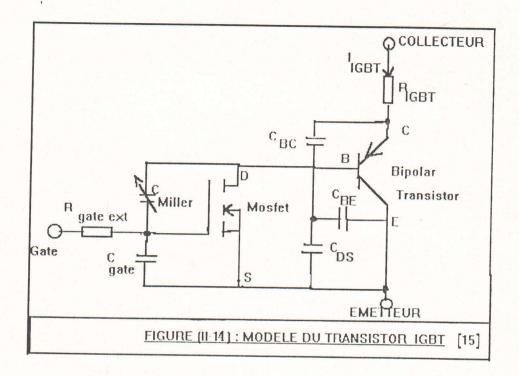

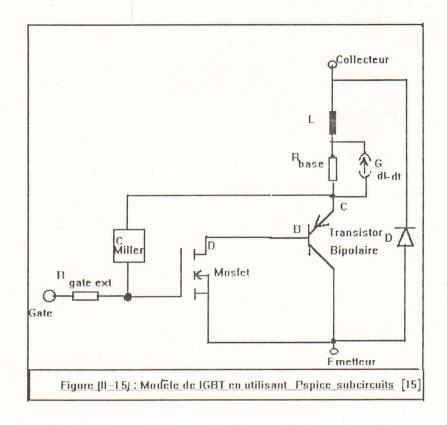

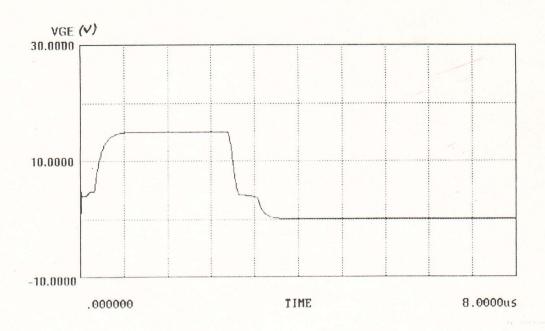

Dans le deuxième chapitre nous présenterons le modèle dynamique du transistor IGBT qui n'est autre qu'une combinaison du transistors VDMOS et du transistor bipolaire, qu'il a fallu donner à chacun son propre modèle afin de représenter un modèle de l'IGBT plus simplifié et plus aisé à intégrer dans un logiciel de simulation des circuits (ESACAP). Nous allons aussi dans ce chapitre, présenter le logiciel ESACAP à travers son formalisme et décrire les

phases essentielles permettant d'aboutir à une version pour ce logiciel du modèle simplifié du transistor I.G.B.T. adapté à l'étude du régime de commutation et nous procéderons ainsi à la transcription du modèle simplifié de l'I.G.B.T. dans ce logiciel. Ensuite et toujours dans le formalisme ESACAP, nous montrerons comment nous réimplanterons le transistor V.DMOS de puissance, le transistor bipolaire ainsi que les éléments non linéaires tels que par exemple la capacité grille-drain et la capacité drainsource par utilisation des modèles de la bibliothèque existante dans l'ESACAP (SPICE). Il sera aussi possible de présenter trois modèles qui sont:

- modèle du VDMOS,

- modèle du transistor bipolaire,

- donc le modèle de l'IGBT.

L'ensemble de ces trois modèles proposés ont la même topologie qui est déduite de celle du modèle physique complet du transistor I.G.B.T. développé au premier chapitre. Il en résulte que tous les paramètres de ces trois modèles gardent un sens physique.

Dans le troisième chapitre nous développerons par ailleurs une méthodologie complète de détermination de quelques paramètres de ces modèles qui seront tous obtenus par des mesures simples ou à partir des données des fabricants des composants. Nous montrerons à cet effet comment doivent être complétés les feuilles de données de ces produits pour fournir les valeurs des paramètres nécessaires à l'étude de la commutation. Le modèle simplifié sera validé en régimes de commutation sur charge résistive et inductive (selfique) par confrontation des résultats de simulation du transistor IGBT en régime de commutation à ceux obtenus sur les maquettes expérimentales.

Ce modèle est d'un grand intérêt pour l'étude des circuits de SMART POWER.

## CHAPITRE I

MODELE MATHEMATIQUE DU TRANSISTOR IGBT.

#### I- INTRODUCTION.

Le bouleversement qui s'est opéré au cours de ces dernières années dans la technologie de réalisation du transistor de puissance IGBT a permis une ouverture significative de sa réalisation en tant que composant de puissance discret.

Actuellement, la gamme de puissance de ce composant atteint des tensions bloquées de  $\approx 2$  Kv et des courants  $> 1200 \land [25]$ .

Le concept de ces composants est basé sur une combinaison de la physique des transistors de puissance bipolaires et des transistors V.DMOS. Ils présentent les avantages suivants :

- Grande vitesse de commutation à L'état "on" et à L'état "off" due à la partie commande représentée par le MOS qui ne nécessite pas un temps d'évacuation des charges minoritaires.

- Grande puissance due à la partie bipolaire (pour des calibres en tension  $400V \le U \le 1200V$  et des calibres courant  $10A \le I \le 600A$ ) [25],

- pertes minimes en commutation,

- utilisation à des fréquences moyennes (f=10KHz).

Notre objectif est d'établir un modèle de simulation des transistors IGBT de puissance avec le logiciel ESACAP. Il faut élaborer celuici (le modèle) en tenant compte des mécanismes physiques existants dans ces nouvelles structures.

Nous allons donc établir le modèle analytique du transistor IGBT. Le modèle décrit les caractéristiques statiques courant-tension de l'IGBT et en dynamiques, pour différentes charges.

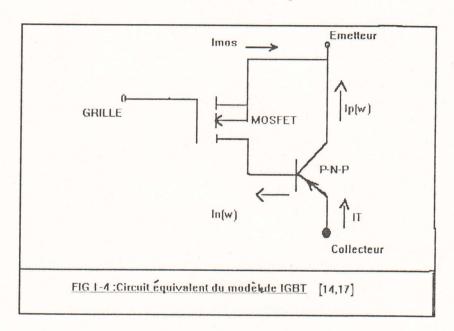

Le modèle est basé sur le circuit équivalent du transistor V.DMOS qui alimente le courant de base du transistor bipolaire de puissance à un faible gain, et à un haut niveau d'injection.

L'élément de base du modèle est l'analyse détaillée du transistor bipolaire qui utilise la théorie du transport ambipolaire et n'assume pas les condition quasistatiques pour l'analyse transitoire.

Pour établir le modèle mathématique de l'IGBT, nous commencerons par rappeler les principales équations qui régissent les comportements statique et dynamique. Pour ce dernier, il sera fait appel à une méthode mathématique non linéaire développée au L.A.A.S [4,5] basé sur la résolution des équations de Poisson, de continuité et de neutralité électrique.

On présentera enfin un schéma électrique équivalent et complet du transistor IGBT.

#### I-1) Technologie du transistor IGBT: [1,13,14,17].

Nous allons présenter un schéma de structure de l'IGBT (Insulated Gate Bipolar Transistor), ainsi que les principales étapes des processus technologiques conduisant à sa réalisation.

La technique de fabrication nécessaire pour réaliser le composant IGBT doit satisfaire les exigences combinées du traitement des composants du VDMOS et du transistor bipolaire.

La durée de vie des porteurs minoritaires doit être suffisamment grande pour assurer une bonne modulation de la conductivité de la région n légèrement dopée, durant la conduction et ainsi qu'une grande qualité de l'oxyde de grille du MOS qui doit être réalisée et maintenue durant le cycle de fabrication.

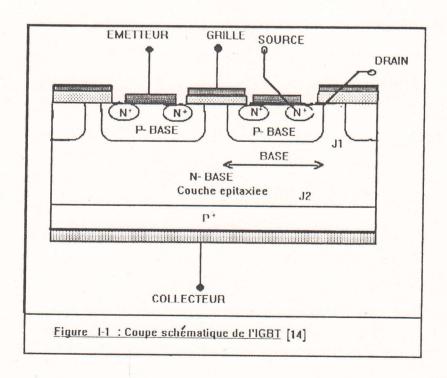

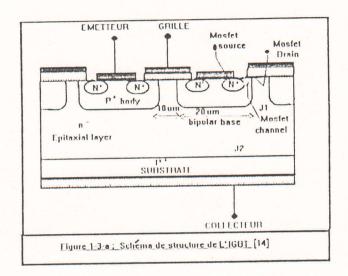

La figure I-1 représente une coupe schématique d'un transistor IGBT à grille en polysilicium. Sa structure est similaire au transistor V.DMOS (Vertical Double Diffused Mosfet) à la seule différence que le substrat fortement dopé de type P<sup>+</sup> remplace le contact drain de type N du Mosfet conventionnel.

La couche épitaxiale épaisse, légèrement dopée du transistor V.DMOS est nécessaire à supporter les grandes tensions en mode de blocage, mais elle présente une grande résistance à l'état "ON".

La jonction PN additionnée J2 ( substrat P,couche épitaxiale N) de l'IGBT sert pour réduire la résistance à l'état "ON" en injectant les porteurs minoritaires qui modulent sa conductivité.

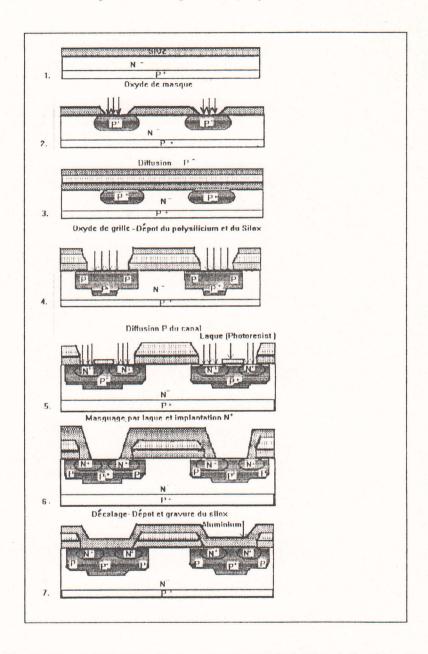

L'excès des porteurs minoritaires qui sont injectés dans la couche épitaxiale (N-Base) diffusent à travers celle-ci. Le reste des porteurs minoritaires(ceux qui n'ont pas été recombinés dans la couche N) atteint la jonction N-Base-P-Base (jonction JΔ) et sont collectés par la base-P, la jonction JΔ étant polarisée en inverse en mode de conduction (mode positif). Le transistor MOS qui se situe sous la grille alimente le base-N en porteurs majoritaires dont une partie est recombinée et l'autre est considérée comme le courant de base du transistor bipolaire. Ainsi l'IGBT fonctionne comme un transistor bipolaire qui est alimenté par le courant du transistor MOS. La figure (I-2) montre les étapes technologiques essentielles pour la réalisation d'une structure pour le transistor IGBT (DMOS) : le matériau de base est un substrat P+ fortement dopé en atomes de Bore (0.01Ω.cm) orienté(111) sur lequel une couche faiblement dopée N avec du Phosphore est épitaxiée. Les couches épitaxiales sont produites en utilisant le tétrachlorure de silicium avec un soin calibré du système de déposition de vapeur chimique.

Les niveaux de dopage dans les couches épitaxiales sont contrôlés à une tolérance  $\pm 10\%$  et les variations d'épaisseurs inférieures à  $\pm 10\%$  sont obtenues.

Sur cette couche N-, un oxyde (étape 1)est réalisé, qui sert de masque à une première diffusion P+(étape 2).

Après la réalisation de l'oxyde mince de grille une couche de polysiliscium est ensuite déposée (étape3). Des fenêtres sont ouvertes à travers le polysiliscium\l'oxyde mince\polysiliscium, définissant ainsi un motif à deux couches qui formera la région de grille, une deuxième diffusion de type P à travers ces fenêtres est effectuée pour former la zone du canal (étape 4); après une étape de masquage par laque (photorésist), les zones N+ de contacts de (l'émetteur) sont diffusées en utilisant le motif de grille comme partie du masque (étape 5). Ces diffusions successives P et N+ permettent à travers leurs extensions latérales d'une part et le procédé d'auto-alignement d'autre part, un contrôle précis de la longueur du canal.

Par la suite, un dépôt d'oxyde basse température (silox) sur la surface de la plaquette suivie d'une gravure de ce silox permettent d'enterrer

la grille et de l'isoler. Les zones de contact sont ensuite gravées; enfin une métallisation des zones de l'émetteur et de collecteur est réalisée, qui est suivie-d'un dépôt d'un matériau de passivation.

Ainsi pour fabriquer des composants IGBTs, un processus standard du DMOS de puissance à grille de polysilicium est donc utilisé.

Figure(I-2): Etapes principales d'un processus typique de réalisation d'une structure pour le transistor IGBT . [4,5]

## I-2) STRUCTURE DE BASE ET FONCTIONNEMENT: [1,13,14,17].

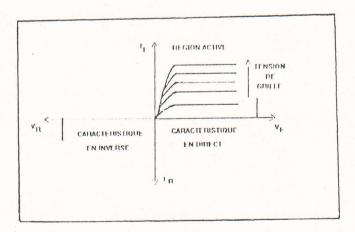

Considérons la structure du transistor IGBT montrée sur la figure (1-3-a). Dans cette structure, le courant ne peut circuler lorsque une tension négative est appliquée au collecteur (respectivement à l'émetteur) car la jonction PN J2 est alors polarisée en inverse.

Lorsque une tension positive est appliquée au terminal collecteur, avec la grille court-circuitée à l'émetteur, la jonction J2 devient polarisée en inverse et le composant opère en son " mode direct de blocage".

Figure (1-3-b) : Caractéristiques électriques de sortie de sortie de l'IGBT . [17]

Avec une tension positive appliquée au collecteur, si une tension suffisamment positive est appliquée à la grille pour inverser la surface de la région P-base sous la grille, le composant opère en mode de conduction direct

("forward conduction state") car les électrons peuvent maintenant circuler de la région émetteur N+ à la région N-base. Dans ce mode d'opération (forward conduction state) à l'état passant, la jonction J2 est polarisée en direct et la région substrat P+ injecte les trous dans la région N-base. Lorsque la tension augmente, la concentration des trous injectés augmente aussi jusqu'à ce qu'elle dépasse le niveau de dopage de la région epitaxiée N-base. Dans ce régime d'opération, les caractéristiques du composant sont similaires à ceux de la diode P-i-N polarisée en directe. Ces composants peuvent opérer avec de grandes densités de courant même lorsqu'ils sont appelés à supporter les grandes tensions de blocage.

Une augmentation de la tension de grille provoque une augmentation de la charge dans le canal et par conséquent un accroissement du nombre d'électrons qui passent dans la base-N. La caractéristique en mode de conduction ressemble à celle de la diode P-i-N. Néanmoins si la conductivité de la couche d'inversion est faible, une chute de tension significative se produit à travers la région , comme celle observée dans les Mosfets conventionnels. Il s'en suit, une saturation du courant direct et le composant opère dans sa région active. La caractéristique électrique du transistor I.G.B.T. s'illustre sur la figure(1-3-b).

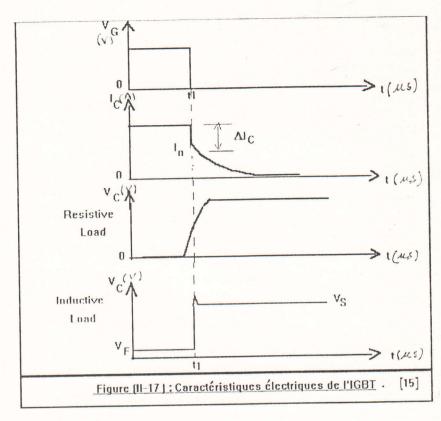

Pour commuter l'IGBT de l'état "on" à l'état "off", il est nécessaire de décharger la grille en court-circuitant celle-ci avec l'émetteur. En l'absence de la tension grille, le canal de la région inversée à la surface de la région P-base sous la grille disparaît. La disparition du canal empêche les électrons de passer dans la région N-base et initialise le processus de " turn-off". Durant celui-ci, il ya une grande concentration des électrons dans la région N-base à la jonction J2. Il s'en suit, une injection significative des électrons dans la région collecteur P+ pendant qu'un courant de trous correspondant circule dans la région P-base. Une fois que la concentration des électrons chute, l'injection de ces derniers dans la région collecteur P+ continue toujours à diminuer, laissant ainsi un nombre d'électrons et de trous dans la région N-base qui doit disparaître par recombinaison. Le processus de " turn off " se divise ainsi en deux phases:

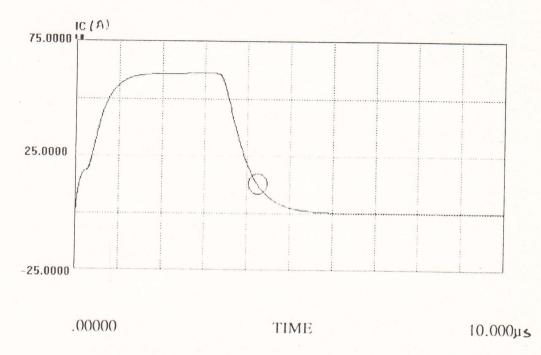

La première phase dans laquelle le courant collecteur doit diminuer rapidement, et la deuxième phase le courant s'affaiblit éxponentiellement en fonction du temps formant une queue(tail) dans la forme d'onde du courant collecteur.

A partir de la précédente description d'opération du transistor IGBT, on peut voir que ce circuit opère avec de grandes densités de courant dans le mode de conduction direct ("forward conduction").

En plus, le composant exige une très faible puissance de la grille, seuls les courants de chargement et de déchargement de la faible capacité de grille sont exigés. Ainsi, ce composant présente des caractéristiques électriques qui s'approchent à ceux d'un interrupteur idéal.

La structure de l'IGBT présentée dans la figure (1-3-a) contient un thyristor P-N-P-N parasite entre les terminaux collecteur et émetteur. Si le thyristor est conducteur, le courant ne peut plus être longuement contrôlé par la grille du transistor MOS. Il est important de concevoir l'IGBT de façon à ce que l'action du thyristor parasite soit supprimée. Ceci peut être fait par la l'élimination de l'injection des électrons de la région N+ émetteur dans la région P-base durant le fonctionnement du composant. La région N+ émetteur commence à injecter des électrons dans la région P-base, si la jonction N+-P devient polarisée en direct avec une tension plus de 0.7V. La de 0.7V est le résultat de la chute de tension due à la circulation d'un courant latéral dans la zone P-base. Cette injection peut être supprimée en choisissant l'épaisseur de la région N+ émetteur étroite et en gardant la résistance Sheet de la région P-base faible.

## I-3) ETUDE ANALYTIQUE DE IGBT: [15]

La modélisation numérique exacte peut être un outil valable lorsqu'on analyse de nouveau types de composants comme l'IGBT.

La modélisation des dispositifs semiconducteurs se fait en utilisant de différents concepts de l'implantation. La première étape est de décrire le comportement physique avec la résolution des équations de drift et de diffusion; ceci se fait généralement dans les programmes de simulation des composants. La connaissance exacte de plusieurs paramètres des composants comme l'épaisseur de la couche, la durée de vie des porteurs et

la réduction de la résistance "ON" sont les facteurs motivant le développement du composant. L'équation mentionnée au dessus, peut être résolue numériquement ou analytiquement, soit à une, ou à deux, ou à trois dimensions. L'avantage de cette méthode est la précision des résultats obtenus, mais pour la simulation de grands circuits elle nécessite beaucoup de temps de calcul.

Pour l'IGBT Hefner a présenté une implantation dans [3] et [4] largement apprécier.

Nous présenterons maintenant un modèle analytique pour un IGBT qui inclue l'analyse détaillée du transport ambipolaire (voir chap.&I-4-a) de la base du transistor bipolaire, partie du composant IGBT et n'assume pas la condition quasi-statique pour l'analyse transitoire.

Le modèle développé qui utilise le circuit équivalent de la figure(I-4) est le modèle analytique de l'IGBT pour décrire les formes d'ondes du courant et tension aux différentes conditions de charge.

#### I-4- MODELE DU TRANSISTOR IGBT:

Le courant de base circule du collecteur à travers la base dans la même direction que le courant collecteur, et le courant total (somme des courants des trous et des électrons) est constant le long de la base, ainsi les caractéristiques du haut niveau d'injection du transistor bipolaire de l'IGBT peuvent être obtenues en utilisant l'équation de transport ambipolaire à une dimension pour décrire le transport de la base. Les équations du transport ambipolaire sont généralement utilisé pour décrire le transport dans la base d'une diode P-i-N. En effet le transistor bipolaire de l'IGBT est traité similairement comme une diode P-i-N mais avec des conditions aux limites du transistor [14].

#### 1-4-a) TRANSPORT AMBIPOLAIRE: [14]

Puisque la base est large et la concentration de dopage de la base est faible pour le transistor bipolaire de l'IGBT, la concentration des porteurs injectés dans la majorité de la base devient supérieure à la concentration de dopage de base pour de faibles densités de courant c'est à dire approximativement 0.2Λ/cm² pour un IGBT avec une durée de vie de la couche épitaxiale de 7μs [14]. Lorsque l'excès des porteurs est supérieur à la concentration de dopage de base, le transport des électrons et le transport des trous se fait sous l'effet d'un champ électrique. Ils ne peuvent être traiter séparément.

L'étude faite en [14], montre que le transport des électrons et des trous dans la base du transistor bipolaire de l'IGBT doit être décrit par le transport ambipolaire, et ne peut pas être décrit par l'approche classique de découplage des équations de transport des électrons et des trous.

En général les courants des électrons et des trous sont donnés par :

$$I_{n} = n.q.\mu_{n}.\Lambda.E + q.\Lambda.D_{n}.\partial n/\partial x$$

(1)

$$Ip = p.q.\mu_{p}.A.E - q.A.D_{p}.\partial p/\partial x$$

(2)

Le premier terme dans l'équation (1) et (2) sont dus au conduction et le second terme sont dus au diffusion.

Dans le cas du transistor bipolaire classique à gain élevé, ces équations peuvent être découplés et le transport des porteurs minoritaires dans la base est décrit par une simple expression, sous les conditions de haut et faible niveau d'injection. Pour un transistor PNP à gain élevé et au faible niveau d'injection (p < < n dans la base ), les conditions de gain élevé exige un courant de conduction des trous négligeable, et le transport des trous est par diffusion seulement ( le deuxième terme dans l'équation (2)).

Dans le cas du transistor bipolaire à gain élevé et au haut niveau d'injection, la quasi neutralité donne n  $\approx p$  et les conditions de gain élevé exige que la conduction des électrons est approximativement celle exigé pour annuler la diffusion des électrons. Ainsi le champ électrique est obtenu en assumant  $I_{\mathfrak{n}}=0.$  En utilisant cette expression du champ électrique et la relation d'Einstein  $D_{n,p}=(k.T/q)\mu_{n,p}$ , une expression du courant des trous est ainsi obtenue.

Néanmoins, dans le cas d'un faible gain, et sous des conditions de haut niveau d'injection du transistor bipolaire de l'IGBT, la différence entre le courant des électrons de conduction et le courant de diffusion est important. Dans ce cas le courant net des électrons a un effet significatif sur le courant de conduction des trous, et les équations de transport des électrons et des trous ne peuvent pas être découplés. En supposant la quasi-neutralité (c'est à dire  $\delta n = \delta p$ ) et un niveau élevé de porteurs en excès (c-à-d  $\delta n > N_B$ ), les courants peuvent être écrits dans le cas du transport ambipolaire en éliminant le champ électrique entre les équations (1) et (2) :

$$I_n = b.I_T/(1+b) + q.D.A.\partial n/\partial x$$

(3)

$$I_p = I_T/(1+b) - q.D.A.\partial p/\partial x$$

(4)

Ces deux expressions dépendent du courant total, ainsi le transport des électrons et des trous sont couplés.

Dans le cas d'un gain élevé (courant des électrons négligeable), le courant total est approximativement égal au courant des trous et l'équation (4) est consignée au modèle à gain élevé et au haut niveau d'injection décrit au dessus. L'équation de continuité est :

$$\partial \delta p/\partial t = -(\delta p/\tau_{HL}) - (\partial J_p/\partial x) \cdot 1/q$$

A partir de cette équation, et l'équation (4), on obtient l'équation de diffusion ambipolaire en fonction du temps:

$$\partial^2 \delta p/\partial x^2 = (\delta p/L^2) + (1/D) \cdot \partial \delta p/\partial t$$

(5)

L'exigence de la résolution de cette équation est que le courant total I<sub>T</sub> est indépendant de la position de la base. Cette exigence est satisfaite pour l'IGBT car le courant de base (courant des électrons) circule du collecteur à travers la base dans la même direction que le courant des trous injectés.

## 1-4-a-1 ) L'ETAT STATIQUE :

Dans cette partie, un système d'équations paramétrique est dérivé pour décrire les densités de courant des électrons et des trous, l'excès de concentration des porteurs, et la tension base-émetteur VBE à l'état statique. Ces équations sont obtenues en résolvant l'équation de transport ambipolaire pour les conditions aux limites du transistor bipolaire. L'analyse décrit aussi:

- a) l'effet du facteur de transport de base,

- b) l'efficacité de l'émetteur pour un faible gain, et le cas du haut niveau d'injection,

#### c) la modulation de la conductivité de la base.

Les caractéristiques du transistor bipolaire sont combinées avec le modèle du transistor MOS pour décrire la caractéristique statique tensioncourant de l'IGBT.

# 1-4-a-2) CONCENTRATION DES PORTEURS ET DENSITE DE COURANT:

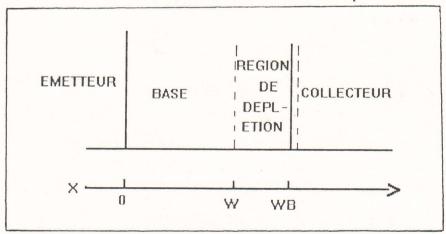

L'analyse a donné des performances en utilisant le système de coordonnées définie par la figure(1-4-a).

#### On défini:

x=0, comme le niveau émetteur au bord de la base.

x=w, comme le bord du collecteur de la base quasi-neutre.

Figure (1-4-a): Système de coordonnées utilisé pour le développement du transistor IGBT [14].

Les conditions aux limites pour la répartition des porteurs en excès sont :

$$\delta p(w) = 0$$

,

$\delta p(0) \equiv p_0$  où  $p_0$  est utilisé comme un paramètre pour le développement du modèle et il est éventuellement éliminé dans le terme du courant.

La largeur de la base quasi-neutrale est donnée par :

$$W = W_{B} - \left[ 2.\xi_{si} \cdot (V_{bc} + V_{bi})/q \cdot N_{B} \right] \frac{1}{2}$$

Largeur de déplétion

de la jonction base-collecteur

où  $V_{bi} \approx 0.7V$ .

L'effet des porteurs mobiles sur la charge de la région de déplétion n'est pas considéré dans l'équation (6).

La résolution de l'équation de diffusion ambipolaire à l'état statique (équ(5) avec  $\partial \delta p/\partial t = 0$ ) dans la base avec ces conditions aux limites donne

$$\delta p(x) = P_0 . \sinh[(w-x)/L] / \sinh(w/L)$$

Cette équation décrit à l'état statique la distribution des porteurs excédentaires dans la base du transistor bipolaire à large base, et à haut niveau d'injection. En tenant compte du quasi-équilibre simplification (c'est à dire que la différence entre les potentiels quasi-Fermi des électrons et des trous est la même sur les deux côtés de la jonction) et en supposant un haut niveau d'injection des trous dans la base, le courant des électrons à la jonction émetteur-base  $I_n(0)$  est donné en fonction de  $P_0$  par la relation :

$$I_n(0)/I_{sne} = \exp(q/kT)^*(\Phi_{pej}-\Phi_{nej}) = P_0(N_B + P_0)/n_i^2 \approx P_0^2/n_i^2$$

(8)

I<sub>sne</sub> = courant de saturation des électrons (mesuré).

En utilisant les équation (3),(4),(7)et(8), on obtient les courants des électrons et des trous dans la base pour une surface A :

$$I_{n}(x) = P_{0}^{2} \cdot I_{sne}/n_{i}^{2} + q \cdot P_{0} \cdot A \cdot D/L$$

$$* \left[ \coth(w/L) \cdot \cosh[(w-x)/L]/\sinh(w/L) \right]$$

$$I_{p}(x) = P_{0}^{2} \cdot I_{sne}/b \cdot n_{i}^{2} + q \cdot P_{0} \cdot A \cdot D/L$$

$$* \left[ \left( \coth(w/L)/b \right) + \cosh[(w-x)/L]/\sinh(w/L) \right]$$

(10)

Ces équations sont évaluées au niveau collecteur de la base (x=w) donnant à l'état statique le courant collecteur Ip(w) et le courant de base  $I_n(W)$  figure(I-4).

#### 1-4-a-3) TENSION BASE-EMETTEUR:

Le contact base a été définie à être au bord du collecteur de la base quasi-neutre où le potentiel quasi-Fermi des électrons coı̈ncide avec ses charges neutres, la valeur de l'équilibre thermique relative au potentiel électrostatique au deux contacts base et émetteur, la tension  $V_{eb}$  est donnée par.

$$V_{be} = (\Phi_{pej} - \Phi_{nej}) + (\Phi_{nej} - \Phi_{nb})$$

(11)

$\Phi_{\mbox{nej}}\text{-}\Phi_{\mbox{nb}}\text{=}$  chute de tension des électrons quasi-Fermi à travers la base quasi-neutre.

Le gradient de potentiel des électrons quasi-Fermi est en relation avec le courant et la concentration des électrons par [14] est:

$$d\Phi_n(x)/dx = -I_n(x)/q.A.\mu_n.n(x)$$

La chute de potentiel des électrons à travers ou le long de la base quasi-neutre est déterminée en intégrant cette équation entre l'émetteur et le bord du collecteur de la base avec  $I_n(x)$  donné par l'équation (3) et  $n(x)\!=\!N_B\!+\!\delta p(x)$  , où  $\delta p(x)$  est donné par l'équation(7) en supposant que la majorité des porteurs dans la base est en haut niveau d'injection. Le résultat de l'intégration est:

$$\begin{split} & \Phi_{nej} - \Phi_{nb} = \left[ I_T.W/(1+1/b).\mu_n.A.q.n_{eff} \right] - (D/\mu_n)*In(P_0 + N_B)/N_B \\ & \text{où} \qquad W \\ & 1/n_{eff} \equiv 1/W \int\limits_{0}^{\infty} dx/(N_B + \delta p(x)) \end{split} \tag{13-a}$$

En utilisant la distribution des porteurs de l'équation (7), on obtient pour n<sub>eff</sub> une solution analytique :

$$\begin{split} n_{eff} & \equiv \left[ (w/2.L). SQRT \left( N_B^2 + P_0^2. csch^2(w/L) \right) \right] / \\ & = \operatorname{arctnh} \left[ \left( SQRT (N_B^2 + P_0^2. csch^2(w/L)). tanh(w/2.L) \right) / \\ & \left( N_B + P_0. csch(w/L)). tanh(w/2.L) \right) \right] \end{split} \tag{13-b}$$

## 1-4-a-4) CARACTERISTIQUE I-VA L'ETAT STATIQUE :

Les équations (6) et (13) sont des équations algébriques en fonction du terme P<sub>0</sub> qui peuvent être combinées pour décrire la caractéristique (I-V) à l'état statique du transistor bipolaire à large base et haut niveau d'injection. Une expression pour la composante P<sub>0</sub> est obtenue en fonction des courants terminaux par l'équ (9) et l'équ (10), ou leur somme évaluée au bord du collecteur de la base pour obtenir le courant voulu par la résolution de l'équation quadratique résultante en terme de P<sub>0</sub>.

Les équations (8),(11)-(13) donnent ainsi  $V_{eb}=f(P_0)$ ; et en utilisant l'expression trouvée de  $P_0$  en fonction de  $I_T$ ; on trouve alors la caractéristique  $V_{eb}=f(I_T)$ .

$$I_{\mathrm{T}}(x) = I_{\mathrm{n}}(x) + I_{\mathrm{p}}(x)$$

Evaluons cette équation au niveau du collecteur de la base à x=w:

$$I_{T}(x) = I_{n}(w) + I_{p}(w)$$

La chute de tension anode-cathode de l'IGBT est donnée par la somme de la : tension V<sub>eb</sub>, tension du canal MOSFET et la chute aux bords de la résistance en série.

$$V_{A} = V_{eb} + R_{mos} \cdot I_{mos} + R_{s} \cdot I_{T}$$

$$\tag{14}$$

Où  $I_{mos} = I_B$  qui est obtenu en évaluant l'expression du courant des électrons donnée par l'équation (9) au côté collecteur,  $I_{Mos} = I_n(w)$  selon la figure(I-4).

Le MOSFET est dans sa région linéaire lorsque l'IGBT est à l'état "ON" et la résistance du MOSFET est donnée par:

$$R_{mos} = 1/Kp*(V_{GS} - V_{T})$$

(15)

La chute de tension annode-cathode de l'IGBT à l'état "on" est donnée explicitement en terme de courant de l'anode et de la tension grille, en supposant  $V_{bc} \approx 0$  (équ.6).

Le gain en courant à l'état statique du transistor bipolaire monté en émetteur commun est donné par :

$$\beta_{SS} \equiv Ip(W)/I_n(W) = f(P_0);$$

en divisant l'équ (10)/ l'équ(9); au point x=w.

$$I_{IGBT} = (1 + \beta_{SS}) * I_{mos}$$

où  $I_{mos} \equiv I_n(w)$ .

En utilisant l'expression trouvée pour  $P_0$  en terme de  $I_n(w)$ , on obtient une expression explicite pour  $I_T$  en terme du canal du Mosfet. Le transistor IGBT est dans sa région de courant de saturation lorsque le Mosfet est dans sa région de saturation. Le courant de saturation du transistor MOS est donné par:

$$I_{mos}^{sat} = (Kp/2)^*(V_{GS}-V_T)^2$$

(16)

En utilisant cette expression et l'expression du courant total en fonction du courant du Mosfet, le courant de saturation de l'IGBT est décrit explicitement en termes de la tension grille  $V_{GS}$  et de la tension de l'anode en supposant  $V_{bc} \approx V_A$  dans l'équation (6).

## 1-4-bl) ANALYSE TRANSITOIRE:

Dans cette partie, le comportement transitoire du transistor bipolaire à base large et à haut niveau d'injection est étudié en accord avec le mode de commutation de l'IGBT.

Pour "ouvrir" l'IGBT, la tension grille est ramenée à une tension plus basse que la tension de seuil  $(V_{\text{TH}})$ , qui élimine rapidement le courant du canal MOSFET qui n'est autre que le courant de base du transistor bipolaire. Le courant collecteur du transistor bipolaire diminue plus longuement, étant donné que les porteurs de charge excédentaires stockés dans la base du transistor bipolaire doivent quitter la base.

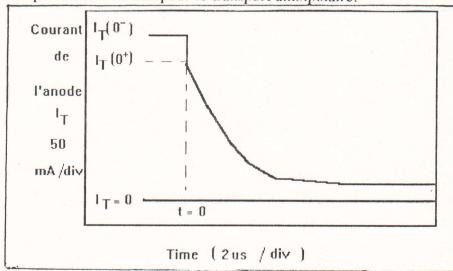

L'affaiblissement de la forme d'onde du courant transitoire de l'IGBT consiste en deux phases :

- Une tombée rapide initiale associé (non égal) au courant de base.

- Un affaiblissement lent dû aux porteurs excédentaires présents dans la base.

Il est montré dans cette partie que la chute rapide initiale du courant est non égal au courant de base à l'état statique. Cette différence existe pour deux raisons :

1- La tension de l'anode et la largeur de la base quasi-neutre sont en général différentes durant l'affaiblissement du courant collecteur qu'à l'état statique.

2- La disparition du courant des électrons (courant de base) réduit toujours le courant des trous (courant collecteur), ainsi l'approximation quasi-statique est non validée pour le transport ambipolaire.

Figure (1-4-b-1): Forme d'onde du courant au turn off en notant le courant avant, après la tombée rapide initiale. [1], [14], [15]

La valeur du courant immédiatement après la tombée rapide [I(0<sup>+</sup>)] de la figure(1-4-b-1) dépend :

- i) des conditions de charge et,

- ii) du courant à l'état statique avant l'initialisation du mode transitoire [I(0<sup>-</sup>)] et il est tiré séparément pour les deux conditions de charge.

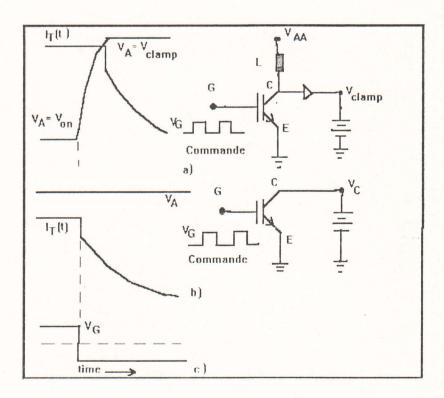

Un modèle à transition de la tension pour une charge inductive est ainsi développé. Il est important de noter que cette transition est plus lente pour un IGBT que pour un MOSFET. La perte de charge durant la transition lente de la tension est toujours importante pour déterminer la valeur de  $I(0^+)$  de la forme d'onde du courant à charge inductive.

Finalement, l'analyse de la transition de la tension est étendue pour décrire les formes d'ondes de courant et de tension transitoires, pour une série de charges, résistance, inductance.

Figure (1-4-b-2): Circuit de test et les formes d'onde du courant et tension correspondantes. [14]

# I-4-b-1) Phase d'affaiblissement lent du courant collecteur à une tension constantel!

A cause de l'absence de la source des porteurs majoritaires (courant de base) durant la phase d'affaiblissement lent de la forme d'onde du courant, l'excès total des porteurs majoritaires stockés dans la base s'affaiblit

soit par recombinaison ou par injection dans l'émetteur. L'excès des porteurs minoritaires dans la base continue à être alimenté par injection à partir de l'émetteur, il est appauvri par le rassemblement à la jonction base-collecteur et recombiné dans la base de telle manière que la quasi-neutralité est maintenue entièrement dans la base.

Ce courant des porteurs minoritaires collecté (courant des trous) est égal au courant total de l'IGBT durant la phase d'affaiblissement lent du courant à une tension constante.

$$I_T(t) = 4.D_p.q(t)/w^2$$

(17)

Ce courant peut être plus bas pour une charge donnée que le courant collecteur à l'état statique ( c'est à dire l'approximation quasi-statique est non validée) car le courant net des électrons (courant de base) qui circule le long de la base ne dure pas longtemps, alors la portion du courant de conduction des trous associé au courant des électrons à l'état statique ne dure pas longtemps non plus. L'excès de charge des porteurs de la base s'affaiblit par recombinaison dans la base et par injection dans l'émetteur.

Le taux d'affaiblissement de la charge totale est donné par :

$$dQ/dt = -Q/\tau_{HL} - I_n(0)$$

(18)

En utilisant l'équation (3),(17) et (18), le taux d'affaiblissement du courant pour une distribution linéaire  $[P_0 = 2.Q/(q.A.W)]$  est donné par :

$$d \ln I_T/dt = (dI_T/dt)/I_T \approx -1/\tau_{HL} \left[1 + I_T/I^\tau_k\right]$$

où  $I^\tau_k = q^2.\Lambda^2.D_p.n_i^2/I_{sne}.\tau_{HL}$  (19)

La solution analytique de l'équation (19) est :

$$I_{T}(t) = I_{T}(0^{+}) / \left\{ \left[ 1 + I_{T}(0^{+}) / I_{\tau_{k}} \right] * \exp(t / \tau_{HL}) - I_{T}(0^{+}) / I_{\tau_{k}} \right\}$$

(20)

où  $I_T(0^+)$  est le courant de charge de contrôle au début de la phase d'affaiblissement lent du courant .

## I-4-b-2) Mode de commutation pour une tension anodique constante :

Dans ce cas, la tension anode et la largeur de la base neutre restent les mêmes durant l'état statique et l'état transitoire. Alors, l'excès des porteurs de charge de la base du début de la phase d'affaiblissement du

courant [Q(0)] est déterminé par l'intégration de la distribution initiale des porteurs excédentaires à l'état statique (équ 7), de l'émetteur au collecteur.

$$Q(0) = q.P_0.A.L.tanh(W/2.L)$$

(21)

L'expression de  $I_T(0^+)$ , du courant immédiatement après la chute rapide initiale, est tirée à partir des équations (17) et (21).

En tirant l'expression du courant trouvée dans l'équation (20), le courant est décrit en fonction du temps après la redistribution.  $I_{T}(0^{-})$  est le courant total à l'état statique avant le début du mode transitoire, il est donné par la somme des équations (9) et (10).

#### I-4-b-3) Transitions de la tension anodique:

En général l'équation de diffusion doit être résolue en tenant compte des conditions aux limites de déplacement de la jonction collecteur-base, pour décrire la distribution des porteurs et le courant des trous collecté durant la transition de la tension. Néanmoins, une expression analytique décrivant l'effet de redistribution des porteurs sur le courant collecté peut être obtenue en utilisant une analyse de perturbation. En général, le courant des électrons dans le collecteur au bord de la base après élimination du courant du canal du MOSFET, est égal au courant de déplacement de la jonction collecteur-base dépletée.

$$(1+1/b)C.dV_A(t)/dt = I_T(t) + 2.q.A.D_P.\partial_P/\partial_X \Big|_{X=W}$$

(21)

où

$$W_{bcJ} \approx \left(2.\varepsilon_{Si}.V_{A}(t)/q.N_{B}\right)^{1/2}$$

(22)

$$W = W_{B^-} W_{bcJ}$$

(23)

et

$$C = A.\epsilon_{si}/W_{bcJ}$$

(24)

$$-2.q.A.Dp.\partial p/\partial x \Big|_{x=w} = I_{CC} + I_{R}$$

(25)

En Annexe B, I<sub>CC</sub> est équivalent au courant de contrôle de charge par l'équation (17) et la composante de redistribution est donnée par :

$$I_{R} \approx -(1+1/b)*(Q/3.W)*dW/dt$$

$$\Rightarrow I_{R} = (1+1/b)*(Q/3.q.N_{B}.A.W)*C.dVA/dt,$$

(26)

La variation de la tension est obtenue à partir des équations (21)-(26) et l'équation (17):

$$dV_{A}(t)/dt = \left[I_{T}(t)-4*D_{P}*Q(t)/(W_{B}-W_{bcJ})^{2}\right]/$$

$$(A*\epsilon_{Si}/W_{bcJ})*(1+1/b)\left[1+Q(t)/3*q*N_{B}*A*(W_{B}-W_{bcJ})\right]$$

(27)

Pour une grande charge inductive:  $I_T(t) \approx I(0^-)$ , alors l'état transitoire, avant que la tension clamp soit atteinte, est déterminée par la charge Q et la tension  $V_A$ . En utilisant les équations (8),(18) et (23), le taux d'affaiblissement de l'excès de charge total dans la base due à la recombinaison et à l'injection dans l'émetteur est donnée par :

$$dQ(t)/dt \approx \left(-Q/\tau_{HL}\right) - \left[4*Q^{2*}I_{sne}/(W_{B}-W_{bcJ})^{2*}A^{2*}q^{2*}n_{i}^{2}\right]$$

(28)

En général les équations (27) et (28) doivent être résolues simultanément avec précision pour décrire l'augmentation de la tension et aussi pour décrire l'excès total de la charge initiale dans la base au début de la phase d'affaiblissement du courant pour une charge inductive.

## I-4-b-4) Conditions de charge générales :

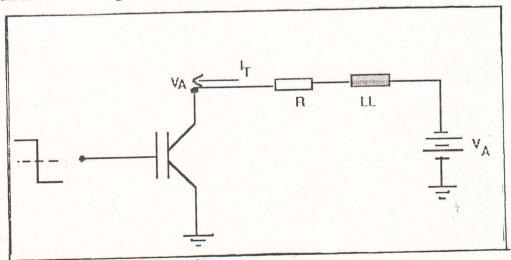

L'analyse précédente peut être facilement étendue à plusieurs conditions de charge générales où les éléments additifs résultent dans l'addition des variables d'état (c'est à dire l'addition d'une équation différentielle couplée avec les conditions initiales). Considérons l'exemple d'un circuit de charge de la figure (1-4-c).

Figure (1-4-c) : Schéma de simulation de la commutation sur charge résistive et inductive de l'IGBT. [14]

La variation du courant terminal peut être écrite dans ce cas en terme de la tension terminale, en utilisant la loi de Kirchoff :

$$dI_{T}/dt = \left(V_{\Lambda\Lambda} - R*I_{T}(t) - V_{\Lambda}\right)/LL \tag{29}$$

En utilisant les équations (27), (28) et (29) simultanément aux conditions initiales du courant , de tension et de charge ; le courant , la tension et la charge qui sont fonction du temps sont obtenus à partir du circuit de la figure(1-4-c). Ces équations différentielles contiennent toute l'analyse transitoire présentée auparavant.

#### I-5) SYNTHESE DU MODELE COMPLET:

Dans cet synthèse, le chemin présenté qui tente de combiner un temps de calcul court et une précision raisonnable.

Pour atteindre ce but, il existe des submodèles qui servent comme outils de simulation et qui sont utilisés pour designer le modèle de l'IGBT.

Le transistor IGBT peut être vu comme une connexion spéciale du transistor V.DMOS et du transistor bipolaire. Cette structure de base forme la colonne vertébrale du nouveau modèle du transistor IGBT.

#### I-6) CONCLUSION :

Dans ce chapitre, nous avons établi un modèle analytique de l'IGBT pour traduire son comportement aussi bien à l'état statique qu'à l'état dynamique et transitoire. Pour cela nous avons rappelé sa structure de base et son mode de fonctionnement; ensuite nous avons proposé un schéma équivalent au moyen des méthodes tant numériques qu'analytiques.

Dans un premier temps, nous avons décrit la méthode de calcul théorique des caractéristiques statiques de l'IGBT dans le cadre de deux hypothèses simplificatrices qui sont :

- i) transport ambipolaire.

- ii) l'approximation quasi-statique est non validée .

Dans un deuxième temps, une analyse transitoire théorique a été rappelée, analyse qui permet d'obtenir des équations différentielles régissant son comportement transitoire.

Cette modélisation complexe de l'IGBT est nécessaire puisque nous voulons une modélisation adaptée à l'étude des régimes de commutation.

# CHAPITRE II

MODELISATION DU TRANSISTOR

IGBT DANS LE LOGICIEL ESACAP.

#### II- INTRODUCTION:

Le modèle physique complet qui a été décrit au premier chapitre, traduit correctement le comportement du transistor IGBT en tout régime de fonctionnement. La mise en oeuvre de ce modèle nécessite la connaissance de certaines données de technologie (longueur de dopage de la zone du canal par exemple).

Dans ce chapitre , nous allons présenter un chemin qui essaye d'assurer un temps de calcul court et une précision raisonnable. Pour assurer ce but ,l'outil de simulation utilisé est le logiciel ESACAP. Ce dernier est utilisé pour ses applications largement répondues , ainsi qu'il offre des submodèles complets pour décrire le modèle de l'IGBT .

Comme expliqué avant , l'IGBT est vu comme une connexion spéciale de VDMOS et du transistor bipolaire. Etant donné que les submodèles disponibles dans l'ESACAP ne sont pas appropriés pour les applications de l'électronique de puissance , des éléments spéciaux doivent être ajoutés dans le but d'obtenir le comportement réel.

Un des objectifs qui sera toujours gardé en mémoire lors de l'élaboration du modèle , est que les topologies doivent être directement déduites du celle du modèle physique de l'IGBT développé au chapitre précèdent . Ainsi tous les paramètres du modèle gardent un sens physique .

### II-1 LE LOGICIEL ESACAP: II-1-1 PRESENTATION :

L'ESACAP est un logiciel de simulation et d'analyse des circuits électroniques initialement développé par European Space Agency en 1970. Ce logiciel est utilisé dans une large mesure pour l'analyse et la conception des circuits intégrés. La facilité de son utilisation sur les mini et micro-ordinateurs fait qu'il est aujourd'hui répondu mondialement dans les laboratoires de recherche universitaires ou industriels. L'un de ses avantages essentiels est la possibilité d'écrire des expressions arithmétiques permettant à l'utilisateur d'établir arbitrairement la dépendance non linéaire entre les systèmes des variables. Le logiciel ESACAP contient toutes les fonctions standards (racine carrée, exponentiel, trigonométriques etc....

Un autre avantage, il permet de définir des sous-circuits et de les implanter par la suite autant de fois que nous les désirons sans avoir à les redéfinir à chaque fois.

Un sous-circuit peut être un macrocomposant accessible par un certain nombre de noeuds. Cette possibilité permet de définir des modèles particuliers à partir des modèles de la bibliothèque ESACAP. En plus il permet d'être couplé avec un programme Fortran quelconque qui est compilé et exécuté par la suite à chaque pas d'intégration.

## II-1-2 LES MODELES DANS L'ESACAP:

Comme nous l'avons déjà signalé, la plupart des composants à semi-conducteur sont modélisés dans l'ESACAP pour des simulations à petits signaux. Pour ce qui nous concerne, nous allons nous limiter à rappeler les modèles des composants qui intéressent cette étude, c'est à dire :

- le modèle de la diode qui servira à décrire d'une part la jonction drain-source, la capacité M.O.S grille-drain et la diode Dbody.

- le modèle du transistor M.O.S, qui n'interviendra en fait que par son générateur de courant.

- le modèle Gummel-Poon du transistor bipolaire.

# II-1-2-1 le modèle du transistor M.O.S:

Trois modèles du transistor M.O.S sont proposés dans l'ESACAP; ils diffèrent par la formulation de la caractéristique statique  $Id(V_{dS})$  et sont classés suivant trois niveaux [1,3,4,5,7]:

- i) <u>le niveau 1</u> est associé au modèle de base; il s'agit du modèle de *Shichman-Hodges* pour le transistor M.O.S à canal long. La mobilité est constante et le courant de saturation Idss varie suivant une loi parabolique en fonction de la tension de grille( $V_G V_T$ ).

- ii) <u>Le niveau 2</u> correspond à un modèle analytique unidimensionnel qui tient compte de la majorité des phénomènes du second ordre associés aux structures de petite géométrie, les effets du canal court sont par exemple pris en compte (mobilité variable, saturation de la vitesse des porteurs etc...).

- iii) <u>Le niveau 3</u> est un modèle semi-empirique pour des M.O.S. de petites dimensions géométriques,  $L < 2\mu m$  et  $W < 2\mu m$ , décrit par une série de

courbes expérimentales plutôt que par des considérations physiques(mobilité variable etc...).

Chacun de ces trois modèles est défini par un certain nombre de paramètres qui sont de deux types: i) électriques (tension de seuil, facteur de pente,...)et ii) des paramètres liés au processus technologique (physiques et géométriques). Au total, on dénombre plus de 40 paramètres pour les trois modèles du transistor M.O.S dont certains sont spécifiques à un niveau de modèle.

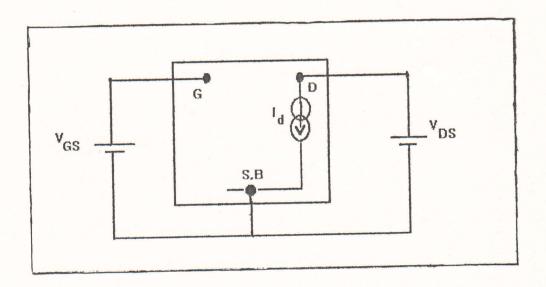

Le schéma équivalent du transistor M.O.S implanté dans l'ESACAP est celui de la figure (II-1):

Figure (II-1): Modèle du transistor MOS implanté dans PSPICE,[4,5].

A) Les équations de courant de drain Id dans PSPICE et réimplantées dans | ESACAP:

Les trois modèles du M.O.S diffèrent par la formulation de la caractéristique statique  $Id(V_{dS})$  qui est explicitée par le tableau de la figure (II-2) pour chacun des trois modèles.

| Niveau | Formulation du courant Id en régime ohmique                          | Relation |

|--------|----------------------------------------------------------------------|----------|

| 1      | $Id = \mu 0.Cox.Z/L [(V_G - V_T).V_D - V_D^2/2]$                     | (II-1)   |

| 2      | $Id = \mu 0.Cox.Z/L \{ [(V_G-V_{bin}-\eta.V_D/2)-(2.\gamma S/3). \}$ | (II-2)   |

| * 3    | $[(2.\phi_F + V_D)^{3/2} - (2.\phi_F)^{3/2}]$                        |          |

| 3      | $Id = \mu_{eff}.Cox.Z/L.[(V_G-V_T).V_D-(1+F_B).V_D^2/2]$             | (11-3)   |

Figure(II-2): Les différentes formulations du courant de drain Id dans le modèle SPICE du transistor M.O.S [4,5].

D'après les relations (II-1) à (II-3), nous remarquerons que le niveau 1 correspond à un modèle classique à mobilité constante (M.O.S. à canal long). Seuls les niveaux 2 et 3 tiennent compte des effets du canal court donc à mobilité variable.

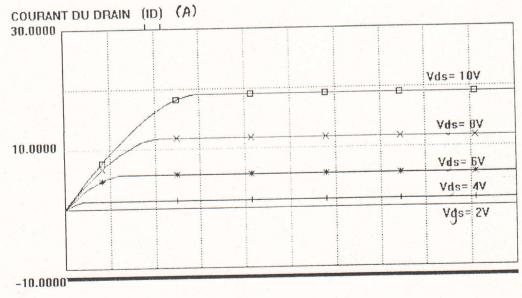

# B) Comportement statique du transistor MOS dans l'ESACAP:

Nous venons de voir que le formalisme niveau 1 s'identifie assez bien au notre. Il nous faut voir maintenant les similitudes pour les relations du courant Id. Le courant de drain est décrit pour le niveau 1 en zone ohmique par la relation suivante (figure(II-1)):

$$Id = \mu 0.Cox.Z/L [(VG - VT).VD - VD^2/2]$$

\*  $Kp(Esacap) = \mu 0.Cox.Z/L$ .

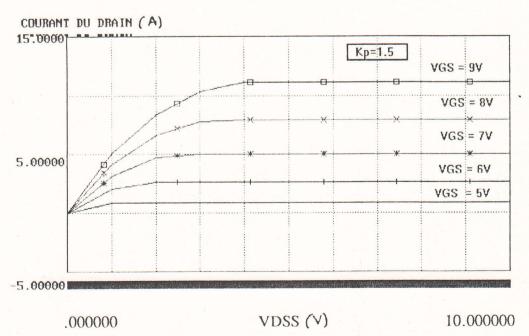

Un exemple de caractéristique Id(Vds) à VGS constant simulées avec le niveau "1", à faible tension de drain Vds, est représenté par la figure(II-3). La courbure et la saturation de ces caractéristiques sont linéaires car la mobilité est considérée comme étant constante égal à  $\mu_0$ . Ce modèle (niveau 1) n'est donc pas adéquat pour l'application aux transistors VDMOS de puissance faible ou moyenne tension, surtout à ceux dont l'épaisseur d'oxyde mince de grille est faible(500A°, M.O.S. à niveau logique) et qui sont particulièrement sensibles aux effets dus au champ électrique transversal.

0.0000 Figure(II-3): Caractéristique statique du M.O.S niveau 1 Id= f(Vds) à Vgs = constante.(simulé)

VDSS (V)

30,0000

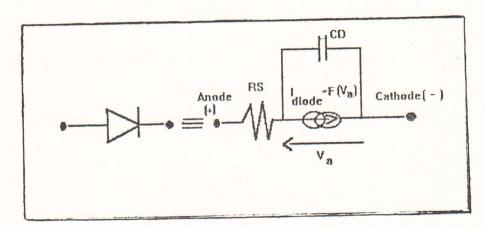

#### II-1-2-2) Le modèle de la diode.

#### A) Présentation:

Le modèle de la diode disponible dans SPICE (ESACAP) est schématisé sur la figure(II-4). Ce modèle vise à décrire indifféremment plusieurs types de diodes réelles(diode Schottky, etc...). La caractéristique statique de la diode, relation(II-4), est définie par le courant de saturation inverse I<sub>S</sub>, le facteur d'idéalité n. La résistance série *Rs* étant comprise dans le modèle.

$$I_{diode} = I_{S}[exp[V_{a}/n.U_{T}]-1]$$

(II-4)

\*  $V_a$  la tension appliquée aux bornes de la diode intrinsèque et  $U_T=K.T/q=1$ 'unité thermodynamique.

Figure (II-4) : Modèle de la diode implanté dans PSPICE réimplanté dans ESACAP. [4],[5]

Le comportement de la diode en régime dynamique est décrit par une capacité  ${\rm C}_{\rm D}$ , relation (II-5a et b), qui comporte en fait deux termes :

$$\begin{split} C_D &= C_S + C_T : \\ & & | C_{J0} / \big[ 1 - V_a / V_j \big]^m; \\ & (CT1), \text{ Si } V_a < V_j * F_c \\ & (II - 5a) \\ \\ C_D &= \Big( \tau . I_S / n . U_T \Big) . \exp \big[ V_a / n . U_T \big] + \big| \\ & | C_{J0} / 1 + F_c \big]^{1 + m} * \\ & | \big[ 1 - F_c * (1 + m) + m * V_a / V_j \big]; \\ & | (CT2), \text{ Si } V_a > V_j * F_c \text{ (II - 5b)} \end{split}$$

Le premier terme, qui prend en compte les effets de stockage des porteurs minoritaires et qui sont directement proportionnel au temps de transit TT, représente la capacité de stockage Cs. Le second terme représente la capacité de transition CT (capacité de déplétion), où la non-linearité est déterminée par les paramètres CJ0 (la capacité pour une polarisation nulle), le potentiel de diffusion VJ et le coefficient m de gradualité de la jonction PN, dont la valeur est voisine de 0.5 pour une jonction réelle.

Nous utiliserons le modèle de la diode pour représenter principalement les capacités "non -linéaires" (Cgd et Cds ) et la diode Dbody.

B) Hypothèses faites pour modéliser Cds, Cgd et la diode Dbody avec le modèle de la diode PSPICE (ESACAP):

Pour la modélisation de la *diode Dbody* de la jonction PN drain-substrat, il faut caractériser le courant de saturation inverse *Is*, la résistance *Rs*, le facteur d'idéalité *n*. Comme nous n'allons considérer cette diode uniquement que lorsqu'elle est polarisée en direct, il faut aussi déterminer sa capacité de stockage C<sub>S</sub> qui est définie connaissant le temps de transit *TT*. La capacité de transition C<sub>T</sub> est automatiquement nulle par défaut dans ESACAP si le paramètre Cj0 n'est pas spécifié.

La capacité C<sub>S</sub> est, aussi nulle par défaut si le temps de transition TT n'est pas défini. En outre, la relative liberté de choix de la valeur des paramètres φ<sub>DB</sub> (φ<sub>DB</sub> >0) et (0< m <0.9), permet d'utiliser ce modèle de diode pour décrire la *capacité de déplétion grille-drain Cgddes* (Cgd étant composée de Cgdmax et de Cgddes représentant la capacité de transition d'une jonction PN polarisée en inverse). La mise en série ou en parallèle de cette capacité avec celle de l'oxyde Cgdmax peut constituer la capacité grille-drain Cgd du V.DMOS.

La détermination des paramètres Cgdmax, VJ, m et  $CJ\theta$  a été faite dans [4,5].

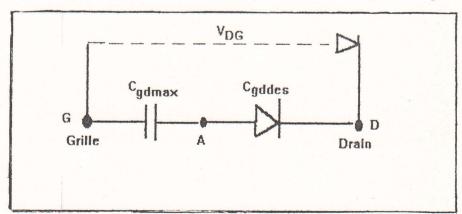

# II-2) MODELISATION DE LA CAPACITE Cgd DANS l'ESACAP:

Parmi les capacités que nous avons à modéliser Cgd, Cds et Cgs, c'est la capacité Cgd qui pose le plus de problème. Cela provient du fait qu'elle est l'association de deux capacités. L'une est la capacité d'oxyde Cgdmax (de valeur constante) qui est prépondérante lorsque la tension VD est

inférieure à la tension  $V_G$ . La deuxième est la capacité de déplétion de la zone sous la grille Cgddes qui n'a d'influence que lorsque la tension  $V_D$  est supérieure à la tension  $V_G$ . Nous remarquons de ce fait que la plus forte variation en valeur de la capacité Cgd se fait lorsque  $V_D = V_G$ . Nous allons donc proposer dans l'ESACAP trois possibilités de représentation de la capacité Cgd, qui seront plus au moins fidèles à la capacité réelle (expérimentale).

- Le modèle à initialisation.

- Le modèle à interrupteurs.

- Le modèle simple à interrupteurs.

On se limitera à la simulation du premier modèle, vu qu'il est le plus "rapide" de 30% à peu prés par rapport aux modèles à interrupteurs, sa topologie est la plus simple mais il nécessite cependant l'utilisation d'un de ses noeuds. Il sera ainsi comparé en tant qu'exemple, aux résultats expérimentaux provenant du transistor V.DMOS de MOTOROLA (25 ampères, 60volts).

#### II-2 MODELE A INITIALISATION:

Ce modèle est une représentation "série" de la capacité Cgd. Il est surnommé à initialisation car lors de l'intégration pour une simulation de cette branche capacitive dans la modélisation ESACAP du transistor V.DMOS, il faudra calculer le potentiel initial du point "A" pour une tension  $V_{DS}\!=\!E_D$  donnée à  $V_{GS}\!=\!0$  donc pour un tension  $V_{DG}\!=\!E_D$ . Ceci est dû au fait que lorsque le point de fonctionnement( $V_{DS}\!=\!E_D$  et  $V_{GS}\!=\!0$ ) est évalué par le programme, celui-ci remplace toutes les branches capacitives par circuit

Figure (II-5): Modèle à initialisation de la capacité Cgd, [4],[5].

ouvert et toutes les inductances par un court circuit.

Il s'en suit que si une branche du réseau contient deux capacités en série comme c'est le cas ici, <u>le calcul transitoire n'est plus correctement initialisé dans cette branche</u>, cela conduit particulièrement à des erreurs sur le calcul des formes d'onde de tension. Ceci est dû essentiellement aux algorithmes de calcul utilisés par l'ESACAP. Nous pouvons résoudre ce problème d'initialisation de la branche capacitive grille-drain de la façon suivante:

#### Détermination des tensions d'initialisation:

Si nous partons d'un état initial(t=0) où le transistor est bloqué( $V_{GS}$ =0), celui-ci ne fait transiter aucun courant dans la charge. Il s'en suit que la tension continue  $E_D$  se trouve entièrement supportée par la capacité  $C_{gd}$  et se distribue d'une part aux bornes de  $C_{gd}$  (diode en inverse) et d'autre part aux bornes de  $C_{gd}$  (diode en capacités peuvent être déterminées de trois manière différentes:

i) - Par calcul en appliquant la relation suivante:[4,5]

$$V = V \left[ 1 - Cgddes / Cgdmax(1-m) \right]$$

- ii) A l'aide du logiciel ESACAP : pour cela, il faut traiter la branche capacitive grille-drain isolée du reste du modèle du V.DMOS. Cette branche est attaquée par un générateur de rampe de tension (0 à ED)de telle sorte que la diode, symbolisant la capacité Cgddes, soit toujours polarisée "en inverse". Le réseau ainsi défini est simulé en régime transitoire à partir des conditions initiales nulles. Le programme ESACAP calcule alors les tensions aux bornes des capacités et détermine les résultats à chaque pas de sortie. Il nous faudra alors attribuer ces tensions pour initialiser les capacités, Cgddes et Cgdmax, par IC=XXVolts lors de l'implantation du modèle dans l'ESACAP pour une tension de polarisation choisie.

- iii)- La troisième méthode consiste en une "auto-initialisation" de la tension par le programme lui-même. Sur le principe, elle est similaire à la deuxième méthode, mis à part le fait que la polarisation continue de drain  $E_D$  est remplacée par une rampe de tension qui monte de 0 à la valeur  $E_D$  et se stabilise à cette valeur pendant toute la durée de la simulation proprement dite. Pendant que la tension de drain "monte", la grille subit une variation  $dV_{DS}/dt$ , il faudra donc laisser un temps de retard pour que celle-ci se décharge avant d'appliquer le signal de commande.

Cette dernière méthode est particulièrement utile dans le cas où le circuit contient plusieurs transistors (bras d'onduleur, etc..).

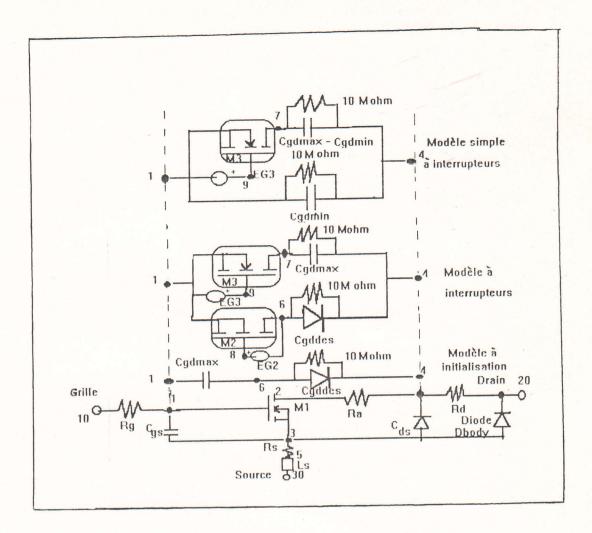

### II-3 ) SYNTHESE DE LA MODELISATION DU TRANSISTOR V.DMOS DE PUISSANCE EN COMMUTATION DANS L'ESACAP :

Pour synthétiser le modèle dynamique du V.DMOS pour la commutation, il suffit de compléter le modèle statique du transistor M.O.S dans l'ESACAP, réduit au générateur de courant, par les éléments dynamiques c'est à dire les capacités inter électrodes Cgs, Cgd, et Cds. La capacité drainsource Cds sera représentée par la capacité de transition d'une diode, la capacité grille-drain Cgd quant à elle, sera représentée par l'une ou l'autre des trois configurations présentées dans le paragraphe précèdent(§-II-2). Quant à la capacité grille-source Cgs, elle sera considérée en premier approximation, constante, du fait qu'elle varie peu avec les tensions de grille et de drain. Il faut compléter avec les éléments parasites liés aux électrodes de grille, de drain et de source. Dans notre cas, les résistances Rg et Rs et l'inductance Ls. Ainsi, trois modèles ESACAP du transistor V.DMOS en commutation peuvent être proposés. Il sont représentés sur la figure(II-6). Le nom des modèles du transistor M.O.S est directement lié à la modélisation choisie de la capacité Cgd, nous avons donc :

- Le modèle du transistor V.DMOS à initialisation .

- Le modèle du transistor V.DMOS à interrupteurs .

- Le modèle du transistor V.DMOS simple à interrupteurs

Au niveau de l'ESACAP, les modèles M.O.S sont implantés sous forme des sous-circuit afin de pouvoir créer une bibliothèque qui comprend les éléments suivants :

- Un transistor MOS de l'ESACAP qui intervient uniquement par son générateur de courant Jd défini par les paramètres suivants :Kp,  $V_T$ ,  $V_{max}$  et  $\theta$  dans le cas du niveau 3 et par Kp  $V_T$  dans le cas du niveau 1(produits haute-tension).

- Deux diodes DDS et DGD pour représenter les capacités nomlinéaires drain-source Cds et grille-drain Cgddes définies par les paramètres :  $C_{IO}$ , m,  $V_{I}$ .

- Des éléments linéaires Ra, Rd, Rs, Rg, Ls, Cgs et Cgdmax.

- La diode Dbody définie par : Rs, Is, N, TT.

Ces paramètres ont été déterminés dans [4,5].

Figure (II-6): Modélisation du transistor V.DMOS implanté dans l'ESACAP [4,5].

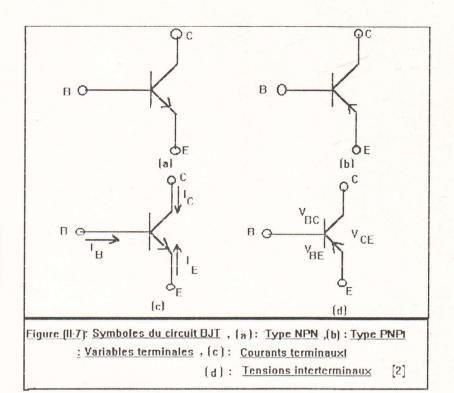

# II-4) LE MODELE DU TRANSISTOR BIPOLAIRE. II-4-1) Présentation:

Le transistor bipolaire(BJT) a une configuration physique de deux jonctions liées à une région mince de type n ou p entre eux. En concordance avec l'ordre des couches des deux jonctions, on a deux types de structure: npn ou pnp(figure(II-7)). La couche interne est appelée base à travers laquelle circule les porteurs minoritaires.

De part et d'autre de la base, l'une des couches qui est l'origine des porteurs minoritaires est appelée émetteur, et l'autre est appelée collecteur.

Dans notre analyse du fonctionnement de BJT, on utilise un modèle à une dimension du transistor npn. Le fonctionnement est similaire pour les BJT de type p, seulement les rôles des trous et des électrons sont inversés ,ainsi que les polarités des courants et tensions terminaux .

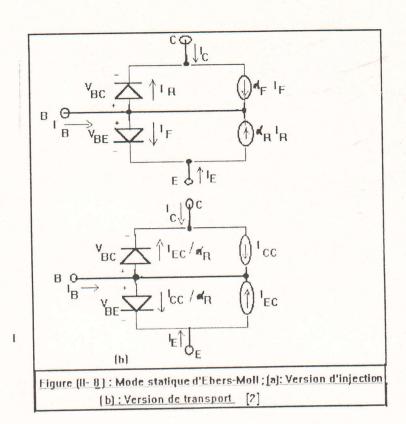

## II-4-2) MODELE STATIQUE EBERS-MOLL.

Le BJT est considéré comme une interaction paire de deux jonctions P-N, l'approche au problème est la même que celle utilisé pour la diode. Les équations de Ebers-Moll expriment cette formalité, elles donnent l'expression du courant  $I_E$  et  $I_C$  de BJT en fonction des tensions des diodes  $V_{BE}$  et  $V_{BC}$ .

# II-4-2-1) Le modèle statique et son implantation dans l'ESACAP. A) Formulation des équations:

Généralement, il ya deux versions du modèle Ebers-Moll: La version d'injection (figure(II-8-a)) et la version transport (figure(II-8-b)). Ces deux versions sont mathématiquement les mêmes, néanmoins la seconde version est préférée pour la simulation et est la base de l'analyse du comportement de BJT.

Dans la version d'injection :

$$I_F = I_{ES} (e^q \cdot V_{BE}/k.T - 1)$$

$$I_R = I_{CS} (e^{q.V}_{BC}/k.T - 1)$$

Où

I<sub>ES</sub> = Courant de saturation base-émetteur

I<sub>CS</sub> = Courant de saturation base-collecteur

Les courants terminaux sont donnés par :

$$I_C = \alpha_F . I_F - I_R$$

$$I_E = \alpha_R.I_R-I_F$$

$$I_{B} = (1-\alpha_{F}).I_{F} + (1-\alpha_{R}).I_{R}$$

$\alpha_F =$  Le gain de courant du "forward large signal" ) de la base

$\alpha_R =$  Le gain de courant du "reverse large signal" ) commune BJT

## B) Implantation dans l'ESACAP :

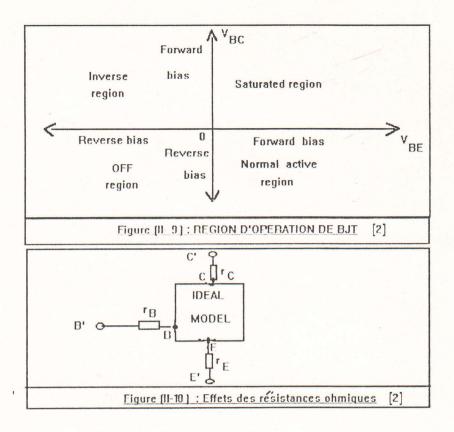

Les courants terminaux du modèle des quatre régions de la figure (II-9) peuvent être écrits et ainsi implantés dans l'ESACAP. Pour assurer la convergence, une petite conductance GMIN (10-12mh) est additionnée automatiquement par l'ESACAP et elle est mise en parallèle à chaque jonction PN:

#### Région active normale:

$$Si \ V_{BE} > -5k.T/q \quad et \ Si \ V_{BC} \le -5k.T/q$$

$$I_{C} = I_{S}.(eq.V_{BE}/k.T + 1/\beta_{R}) + [V_{BE}-(1+1/\beta_{R}).V_{BC}].GMIN$$

$$I_{B} = I_{S}[(1/\beta_{F}).(eq.V_{BE}/k.T - 1)-(1/\beta_{R})] + [V_{BE}/\beta_{F} + V_{BC}/\beta_{R}].GMIN \qquad (II-6)$$

#### Région inverse :

$$\begin{split} \text{Si V}_{BE} & \leq \text{-5k.T/q} \quad \text{et Si V}_{BC} > \text{-5k.T/q} \\ \text{I}_{C} & = \text{-I}_{S}.[e^{q} \cdot {}^{V}_{BC}/k.T + (e^{q} \cdot {}^{V}_{BC}/k.T).(1/\beta_{R})] \\ & + [V_{BE}\text{-}(1+1/\beta_{R}).V_{BC}].\text{GMIN} \\ \text{I}_{B} & = \text{-I}_{S}.[(1/\beta_{F})\text{-}(1/\beta_{R}).(e^{q} \cdot {}^{V}_{BC}/k.T \text{-1})] \\ & + [V_{BE}/\beta_{F} + V_{BC}/\beta_{R}].\text{GMIN} \end{split} \tag{II-7}$$

### Région de saturation :

$$\begin{split} \text{Si V}_{BE} > -5k.\text{T/q} &\quad \text{et Si V}_{BC} > -5k.\text{T/q} \\ \text{I}_{C} = \text{I}_{S}.[(e^{q.V}_{BE}/k.\text{T} - e^{q.V}_{BC}/k.\text{T}) - (e^{q.V}_{BC}/k.\text{T}).(1/\beta_{R})] \\ + [\text{V}_{BE} - (1 + 1/\beta_{R}).\text{V}_{BC}].\text{GMIN} \end{split}$$

$$I_{B} = I_{S}.[(1/\beta_{F})(e^{q}.V_{BE}/k.T-1)+(1/\beta_{R}).(e^{q}.V_{BC}/k.T-1)] + [V_{BE}/\beta_{F} + V_{BC}/\beta_{R}].GMIN$$

(II-8)

#### Région off (blocage):

$$\begin{split} &\text{Si V}_{BE} \leq \text{-5k.T/q} \quad \text{et Si V}_{BC} \leq \text{-5k.T/q} \\ &\text{I}_{C} = (\text{I}_{S}/\beta_{R}) + [\text{V}_{BE}\text{-}(1+1/\beta_{R}).\text{V}_{BC}].\text{GMIN} \\ &\text{I}_{B} = \text{-I}_{S}.[(\beta_{F}+\beta_{R})/\beta_{F}.\beta_{R}] + [\text{V}_{BE}/\beta_{F} + (\text{V}_{BC}/\beta_{R})].\text{GMIN} \end{split} \tag{II-9}$$

La limitation de ce modèle simple se situe principalement dans la négligence de la charge de stockage(nom des capacités de diffusion et de la jonction) et les résistances ohmiques aux terminaux.

#### C) Modèle statique :

\* effet du second ordre et son implantation :

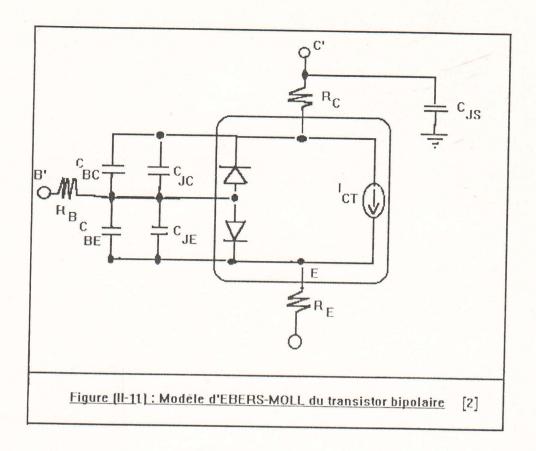

Dans cette partie, le modèle de BJT est développé avec plus de précision: on introduit quatre nouveaux paramètres  $R_{E}$ ,  $R_{B}$ ,  $R_{C}$  et  $V_{A}$  (fonction de  $I_{S}$  sur  $V_{BC}$ ), selon la figure (II-10). La résistance  $R_{C}$  fait diminuer la pente des courbes dans la région de saturation pour la tension  $V_{CE}$  basse.

Dans le modèle idéal,  $R_C$  =0; alors que dans le comportement actif, elle est une fonction du courant collecteur et de la tension  $V_{BC}$ , donc  $R_C$  peut limiter le courant de "handling capability" de BJT .

# II-5) SYNTHESE DE LA MODELISATION DU TRANSISTOR BIPOLAIRE DANS l'ESACAP.

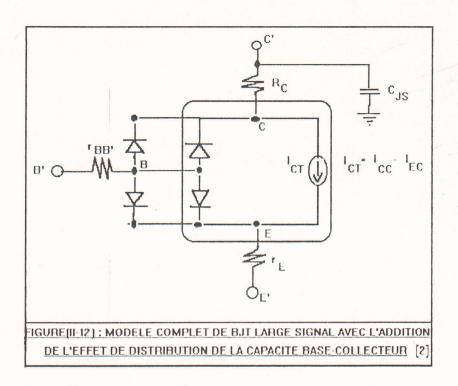

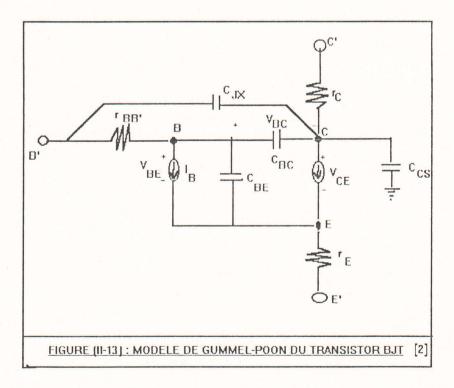

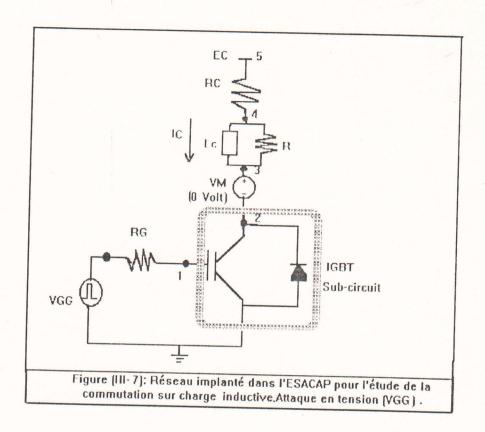

II-5-1 ) Modèle d'Ebers - Moll :